# **NEWT Microprocessor**

## **Technical Manual**

Every effort has been made to ensure the accuracy of the information contained herein. If you find errors or inconsistencies please bring them to our attention. In all cases, however, the Verilog HDL source code for the NEWT design defines "proper operation".

Copyright © 2013, 2014, Systemyde International Corporation. All rights reserved.

#### Notice:

"HP-41C", "HP-41CV", "HP-41CX" and "HP" are registered trademarks of Hewlett-Packard, Inc. All uses of these terms in this document are to be construed as adjectives, whether or not the noun "calculator", "CPU" or "device" are actually present.

#### Acknowledgements:

This project never could have succeeded without Warren Furlow's excellent Web site hp41.org. And even more important was his SDK41R6 software suite, for code development, and his V41 program for code debugging. Numerous people have answered my dumb questions on the Web site hpmuseum.org, and the book "Inside the HP-41" by Jean-Daniel Dodin was invaluable for getting a foothold on understanding the HP-41 operating system and register usage. Gene Wright was kind enough to be my voice at the HHC 2010 conference.

# Index

| Revision History       | 2   |

|------------------------|-----|

| 1. Introduction        | 3   |

| 2. Programming Model   | 5   |

| 3. Memory Organization | 9   |

| 4. Instruction Set     | 15  |

| 5. Turbo Mode          | 127 |

| 6. Keyboard Scanner    | 131 |

| 7. External Interface  | 133 |

| 8. Timing              | 141 |

| 9. Power Control       | 147 |

| 10. I/O Ports          | 151 |

| 11. Pin Assignments    | 157 |

| Appendix               | 161 |

# **Revision History**

| Date       | Changes                                                                             | Pages           |

|------------|-------------------------------------------------------------------------------------|-----------------|

| 01/01/2010 | Complete review & update                                                            |                 |

| 01/14/2010 | Update module image list to avoid copyright issues                                  | 163-169         |

| 01/20/2010 | clarify y-functions options                                                         | 157-169         |

| 07/02/2010 | Correct CLRST instruction description                                               | 69              |

| 07/19/2010 | Change Turbo behavior for a number of instructions:<br>?LLD, DADD=C, DATA=C, REGn=C | 24, 76, 77, 103 |

|            | Correct C=REGn instruction description.                                             | 63              |

| 07/21/2010 | Update Turbo mode description.                                                      | 123-126         |

| 07/21/2010 | Update Keyboard Scanner description                                                 | 127-128         |

|            | Update Memory Organization description                                              | 167-172         |

| 09/13/2010 | "final" review and update                                                           | 157-181         |

| 09/17/2010 | Clarify serial function boundary cases                                              | 170-173         |

|            | Clarify reg_addr operation with C=REGN and REGN=C                                   | 63, 103         |

| 10/18/2010 | Update Light Sleep signal states                                                    | 135             |

|            | Update appendices                                                                   | 157-186         |

| 11/10/2010 | Added instruction table. Miscellaneous clean-ups.                                   | various         |

| 11/12/2010 | Added MMU registers for pages 4, 6, and 7.                                          | various         |

| 11/19/2010 | Added ASTROUI image                                                                 | 167, 187        |

|            | Added DISASM-4C image                                                               | Appendices      |

| 11/29/2010 | Added 1-page option for SandMath image                                              | Appendices      |

|            | Changed ENBANKx operation description                                               | 81              |

| 01/14/2011 | Deleted Appendices to separate NEWT from 41CL                                       |                 |

| 04/04/2011 | Updated power-up timing description.                                                | 148             |

| 04/06/2011 | Updated Rate and Control registers to write-only                                    | 152, 153        |

| 04/12/2011 | Updated Tx Status register.                                                         | 152             |

| 07/15/2011 | Updated peripheral registers                                                        | 151, 154        |

| 08/22/2011 | Updated Page mapping information                                                    | 10,             |

| 08/22/2011 | Updated WCMD operation for special MMU enable/disable.                              | 12-13, 121      |

| 03/07/2012 | Added description of bank registers for pages 6 and 7.                              | 10-14           |

| 01/20/2013 | Typos (p14), added Appendix                                                         |                 |

| 02/08/2013 | MMU Write command cannot be used for pages 0-3                                      | 12              |

| 09/22/2014 | CHKKB, RSTKB instruction timing                                                     | 153-154         |

| 06/27/2015 | Typos (register names)                                                              |                 |

| 06/29/2015 | Typos about MMU enable bit                                                          | 11              |

| 06/30/2015 | Tx Buffer Empty status bit polarity                                                 | 153             |

# Introduction

The NEWT (Nut, Expanded, With Turbo) CPU is an upgraded version of the Hewlett-Packard Nut microprocessor, which was employed in a number of HP calculators, including the HP-41 series. Only publicly available documentation was used to create this design so there may be minor differences where the public documentation is misleading or lacking. The instruction set and register architecture are identical between the two designs.

This document should always be used as the final word on the operation of the NEWT microprocessor, but it is useful to refer to the Hewlett-Packard documentation if the description given here is too cryptic. The Nut architecture is over twenty years old, so we assume that it is already at least somewhat familiar to the reader.

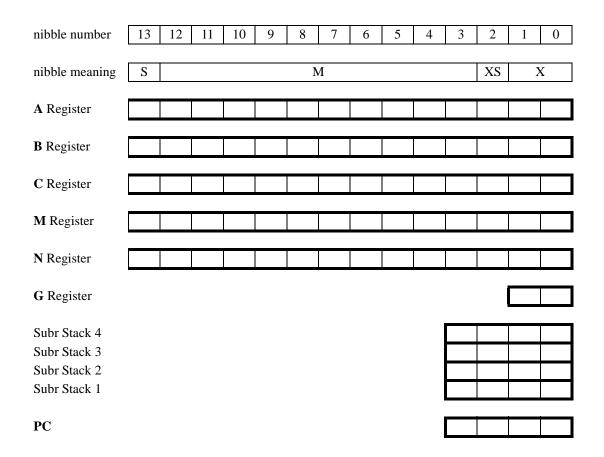

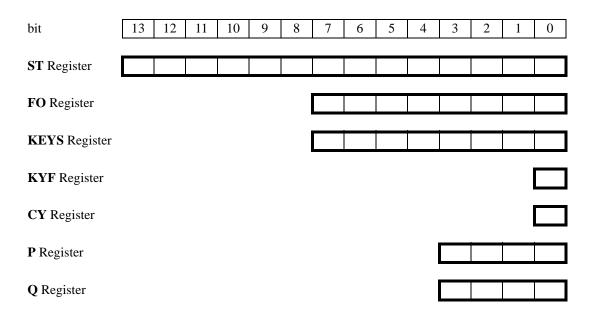

As one would expect for a microprocessor targeted for handheld calculators, the NEWT architecture is highly optimized for BCD floating point math. The architecture includes three primary 56-bit (14 digit) registers, two auxiliary 56-bit registers, and one 8-bit general-purpose register. There are two 4-bit pointer registers that are used to select fields within the 56-bit registers. A Carry bit communicates carry information from one operation to the next, and there is a 14-bit general-purpose status register.

A dedicated keyboard scanner continuously scans a keyboard of up to seven rows and six columns. There is also an 8-bit serial status output and a 14-bit serial flag input. The Program Counter (PC) is sixteen bits wide and the instructions are ten bits wide. The program memory is logically separate from the data memory.

In the original Nut design all information was transferred serially to or from the CPU. One of the expanded features of the NEWT design is a traditional 16-bit parallel memory interface. This allows the use of standard word-wide memories to hold both program and data information. It also allows program information to be held in RAM memory, a feature that was not present in the original NUT architecture. This interface contains two Chip Selects, one for a FLASH memory and one for a RAM memory.

As mentioned previously, the PC is sixteen bits wide, providing 64k words of instruction memory. This instruction memory is divided into sixteen pages of 4k words each. In addition, many of these 4k pages can have up to four banks, only one of which is active at a time. In the NEWT design a Memory Management Unit (MMU) can be used to map each

page and bank into a physical address that is in either the Flash memory or the RAM memory.

One unique feature of the original Nut architecture was the ability to transfer control from the CPU to an intelligent peripheral that executes in-line instructions while the CPU is idled. This feature is still available in the NEWT design, even when operating in the Turbo mode.

The Turbo mode speeds up the clock to the CPU by a factor of up to fifty, under program control. The serial Nut-compatible signals continue to be generated but the CPU executes via the new parallel memory bus for both instructions and data. Instructions that will affect the serial signals or that must be seen by an external peripheral or memory automatically slow down the CPU to normal speed to execute, preserving system compatibility. In addition, since the instruction is only ten bits wide, two of the unused bits in the 16-bit parallel memory devices are used to modify Turbo mode execution for things such as timing loops.

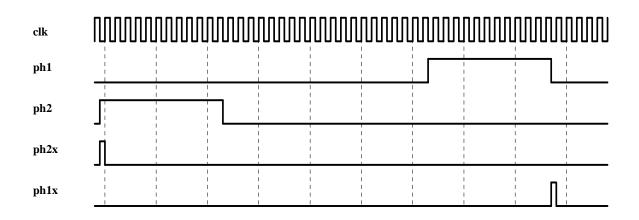

Throughout this document Nut-compatible pin signals will be denoted in bold (for example, **ph1**). It is important to remember, however, that the actual NEWT design must be surrounded by a virtual pad ring constructed out of discrete circuitry. This is necessary to maintain compatibility with the existing Nut hardware, which uses a 6V supply, and the NEWT hardware, which of necessity will use a lower voltage. This voltage translation is explained in detail in the External Interface chapter.

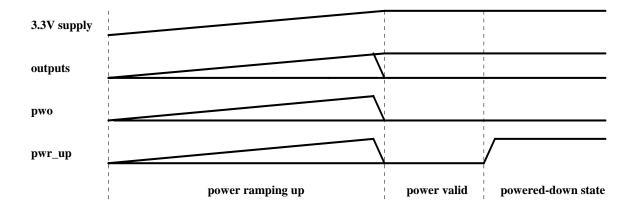

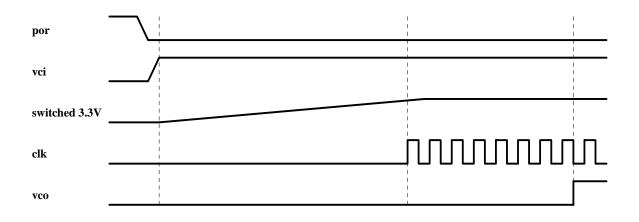

The NEWT design is partitioned into two sections. The first section contains the majority of the CPU and is designed to be powered down while not in use. The second section, which is much smaller, is continuously powered and controls the power-up and power-down for the CPU. If the NEWT design is implemented in programmable logic, the CPU will be implemented in an FPGA, while the second section will be implemented using a CPLD. If the NEWT design is implemented in a stand-alone chip both sections can be on the same chip, on separate power planes. The details of the power-up and power-down operation is explained in the Power Control chapter.

# **Programming Model**

The NEWT register architecture contains five 56-bit (14 digit) general-purpose registers, called A, B, C, M and N. C is the primary register, and most operations involve this register as either one of the sources or as the destination. These 56-bit registers generally hold BCD floating point numbers, with a two digit exponent, one digit for the exponent sign, a ten-digit mantissa, and one digit for the mantissa sign.

Normally both the exponent and mantissa hold 10's-complement BCD numbers. However, the CPU can also be operated in Hexadecimal mode, where the full binary encoding is allowed in the registers, for binary data or alphanumeric data. In the Hexadecimal mode all arithmetic operations operate in binary fashion, with binary carries from bit-to-bit and digit-to-digit. In the Decimal mode, BCD digits are handled, with all arithmetic results converted automatically to BCD, with BCD carries across digits as necessary.

There is also an 8-bit G register that can be loaded, stored and exchanged with an two adjacent digits of the C register.

The Program Counter is 16 bits wide, and a four-level subroutine stack is included. This subroutine stack does not overflow to any external memory, so no more than four levels of nested subroutines can be handled without additional program overhead.

The architecture includes a number of other special-purpose registers. The Status (ST) register is fourteen bits wide and is usually accessed as individual bits. These bits can be used for program status. The Flag Output (FO) register is automatically shifted out serially during each instruction time. The individual bits can be latched externally or merely used to create a repeating waveform.

The Keyboard Flag (KYF) register is set automatically by the keyboard scanner when a keypress is detected. The scan code of the key being pressed is then loaded into the Keyboard (KEYS) register. The keyboard scanner handles multiple key presses and the KYF register operation aids in implementing rollover for the keys. The keyboard scanner operation is covered in more detail in the Keyboard Scanner chapter.

The Carry (CY) flag is a single bit that communicates carry information from one instruction to the next. This flag can also be tested for jumps and subroutine calls. Note that the state of the CY flag does not persist. If it is not explicitly set by an instruction, then it will always be cleared by an instruction. At the end of a peripheral operation, the selected peripheral can communicate information back to the CPU via the CY flag.

The P and Q registers are four-bit registers used to point to specific digits or ranges of digits in the general-purpose registers. When pointing to a specific digit only one of the registers is active at a time, but both are used when selecting a range of digits.

The CPU does not automatically operate on the entire floating-point number. Rather, software must handle individual fields explicitly. Hence the need for the Time Enable Field, or TEF. Most operations on the general-purpose registers include a TEF, to specify exactly which digits will be affected by the operation. All digits not selected by the TEF are unchanged. Eight different TEF values are encoded into those instructions that use this function according to the following table.

| Encoding | Mnemonic | Meaning                     |

|----------|----------|-----------------------------|

| 000      | РТ       | On Pointer                  |

| 001      | Х        | Exponent & Sign             |

| 010      | WPT      | Word Through Pointer        |

| 011      | W        | Whole Word                  |

| 100      | PQ       | Pointer P through Pointer Q |

| 101      | XS       | Exponent Sign               |

| 110      | М        | Mantissa Only               |

| 111      | S        | Mantissa Sign               |

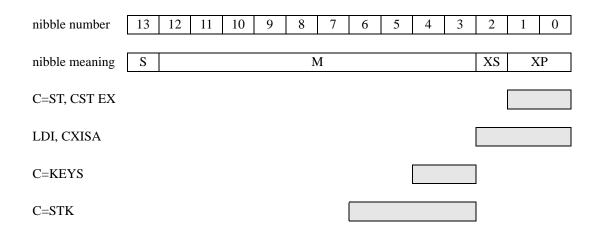

Most of these TEF values are straightforward, selecting one or more of the floating point fields, as shown in the figure below:

| nibble number  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|----------------|----|----|----|----|---|---|---|---|---|---|---|----|---|---|

| nibble meaning | S  |    |    |    |   |   |   |   |   |   |   | XS | Х | P |

| X TEF          |    |    |    |    |   |   |   |   |   |   |   |    |   |   |

| W TEF          |    |    |    |    |   |   |   |   |   |   |   |    |   |   |

| XS TEF         |    |    |    |    |   |   |   |   |   |   |   |    |   |   |

| M TEF          |    |    |    |    |   |   |   |   |   |   |   | ]  |   |   |

| S TEF          |    | ]  |    |    |   |   |   |   |   |   |   |    |   |   |

The three remaining TEF values use the pointers. The On Pointer (PT) value selects only the digit pointed at by the current pointer. Word Through Pointer (WPT) selects all digits from digit 0 through the digit pointed at by the current pointer.

Pointer P through Pointer Q (PQ) operates as would be expected when P points to a digit lower than the digit pointed at by Q, selecting digit P through digit Q, inclusive. If P and Q are equal only that digit is selected. If P is greater than Q the value of Q is ignored and digits starting with the digit selected by P through the end of the word are selected.

In addition to these Time Enable Fields, there are a few other instructions that use specific digit times. These are shown in the figure below:

# **Memory Organization**

The memory organization of the NEWT microprocessor must be viewed from two different perspectives. The first view is the memory organization of the original Nut microprocessor. This is the logical memory organization and consists of separate program and data memory spaces. The second view is the native memory organization of the NEWT microprocessor itself. This is the physical memory organization and consists of a unified memory space divided in half by the two available chip selects. The logical memory usually maps into the physical memory.

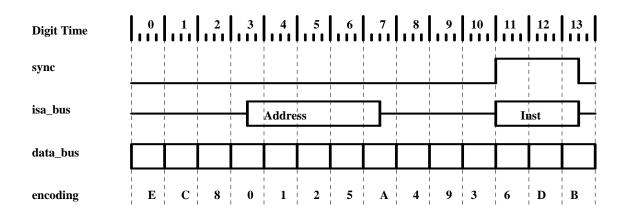

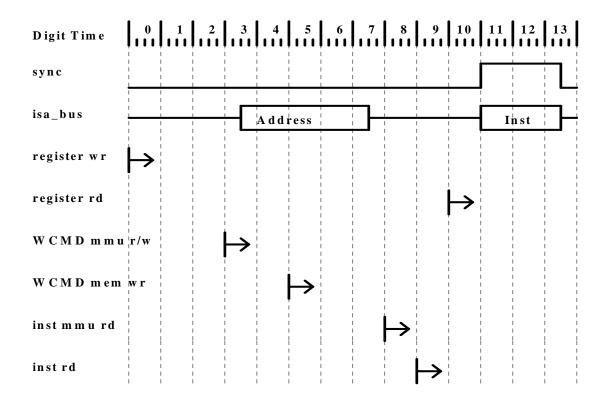

The logical memory is what is normally visible to the programmer. It consists of a 64K by 10-bit program memory space and a 4K by 56-bit "register" memory space. Program memory is accessed via the bidirectional serial **isa\_bus** signal, which carries both the instruction address and the instruction data. Register memory is accessed via the bidirectional serial **data\_bus** signal for the data, which communicates with the C register. Register addresses are handled differently, with the register address being latched in a dedicated location external to the processor. The program memory is normally read-only and the register memory is read/write.

The 4K by 56-bit register memory is used for data, alarms or user programs. However, from the point of view of the microprocessor, register memory is just read/write data memory. In the NEWT microprocessor, all register memory is mapped automatically into a particular region of physical memory. This mapping is completely transparent to the user. Note that even though the NEWT microprocessor properly handles 4096 registers, existing 41C Operating System software only provides for accessing 1024 registers.

In the original 41C system, register addresses were stored in the register memory chips. The NEWT design stores the register address in a reserved physical memory location. The contents of this memory location, called reg\_addr, are retrieved from physical memory each time a register is accessed.

The 64K by 10-bit program memory is divided into sixteen 4k "pages" using the upper four bits of the address. Some of these pages support up to four "banks". A number of pages are dedicated to particular software functions in the HP-41C series of calculators. This is shown in the table below, along with the bank information. Note that the 8K "Ports" allow the use of external plug-in modules for software, and the Card Reader peripheral always uses Page E in Port 4.

| Logical<br>Address MSB | Logical<br>Page | Banks | HP-41C function                       |

|------------------------|-----------------|-------|---------------------------------------|

| 0000-0010              | 0-2             | one   | Operating System                      |

| 0011                   | 3               | one   | Extended Functions                    |

| 0100                   | 4               | one   | Service Module                        |

| 0101                   | 5               | four  | Time Module and<br>Extended Functions |

| 0110                   | 6               | four  | Printer                               |

| 0111                   | 7               | four  | HP-IL                                 |

| 1000-1001              | 8-9             | four  | Port 1                                |

| 1010-1011              | A-B             | four  | Port 2                                |

| 1100-1101              | C-D             | four  | Port 3                                |

| 1110-1111              | E-F             | four  | Port 4                                |

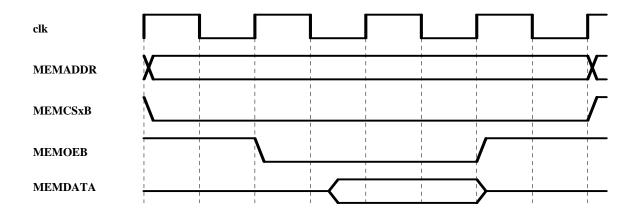

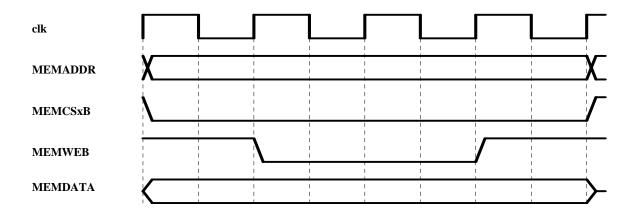

The physical memory in the NEWT microprocessor is 16M by 16 bits. This physical memory is divided into two 8M regions, with a separate chip select for each region. The lower half of physical memory uses **MEMCS0B** and is normally connected to a Flash memory device. The upper half uses **MEMCS1B** and is normally connected to a RAM memory device.

The register memory is automatically mapped to the 16K word section of physical memory starting at address 0x800000. This places it at the bottom of RAM memory. The register address is stored in physical memory location 0x804000. The 56-bit register data is automatically packed and unpacked into this 16K word region so that it appears to be the normal register memory. Certain areas of program memory are also automatically mapped to physical memory as shown in the table below.

| Logical<br>Page | Bank     | Physical Address [23:12]                                 |

|-----------------|----------|----------------------------------------------------------|

| 0               |          | normally 0x000                                           |

| 1               |          | normally 0x001                                           |

| 2               |          | normally 0x002                                           |

| 3               |          | normally 0x003                                           |

| 4               |          | from MMU (if enabled)                                    |

| 5               | all four | normally bank 1: 0x006<br>normally banks 2, 3 & 4: 0x005 |

| 6               |          | from MMU (if enabled)                                    |

| 7               |          | 0x007 if MMU disabled;<br>otherwise from MMU             |

| 8 | all four | from MMU (if enabled) |

|---|----------|-----------------------|

| 9 | all four | from MMU (if enabled) |

| А | all four | from MMU (if enabled) |

| В | all four | from MMU (if enabled) |

| С | all four | from MMU (if enabled) |

| D | all four | from MMU (if enabled) |

| Е | all four | from MMU (if enabled) |

| F | all four | from MMU (if enabled) |

Logical pages 0-3 and 5 are normally reserved for the Operating System. Enabling the Special MMU operation turns on the translation circuitry for those pages, but only if the the regular MMU operation is also enabled.

When program memory is mapped to physical memory the ten bits of actual program data are right-justified in the sixteen bits of physical memory. Bits 15-14 and 11-10 are unused and bits 13 and 12 are used by the Turbo control logic to control execution speed on an instruction-by-instruction basis. This operation is explained in the Turbo Mode chapter.

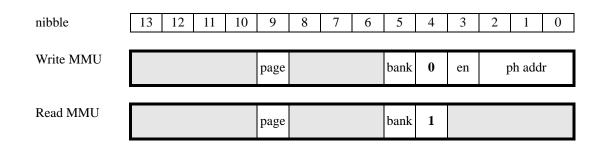

The NEWT-specific WCMD instruction is used to write to either the physical program memory or to the MMU registers, using the contents of the C register for the actual command, address and data information. The command in digit 4 determines the destination of the write data. These commands are described below. When a bank selection is required, it is encoded into digit 5 according to the following table:

| Nibble 5 | Memory bank selected |

|----------|----------------------|

| xx00     | bank 1               |

| xx01     | bank 3               |

| xx10     | bank 2               |

| xx11     | bank 4               |

A command value of 0000 identifies a write to an MMU register to enable or disable address translation for a particular page and bank. A command value of 0001 identifies a read of an MMU register. The specific MMU register is selected by the combination of the page value in digit 9 and the bank select value in digit 5. A one in the most-significant bit of digit 3 enables address translation, while a zero in this bit disables address translation. The twelve bits of the physical address that will be substituted for the page value in the selected bank is contained in digits 2-0. Read data is latched by the command and must be accessed using the on-chip I/O Port. Programming the MMU requires some care. The

MMU entry for a particular page/bank should never be updated while executing from that page/bank. Doing so will switch the instruction fetch to another region of physical memory, which may lead to unexpected results.

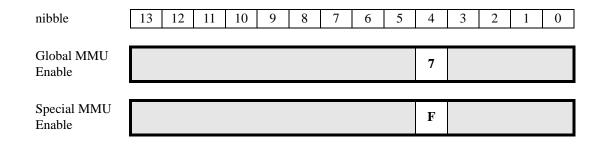

Writes to MMU registers for pages 0-3 are ignored, and these MMU registers must be accessed using the Write Physical Address command. Disabled pages (and/or banks) are not fetched from physical memory, but are fetched from external memory via the **isa\_bus**. Disabled pages are always fetched at normal speed. Note that on first power-up the entire MMU is disabled because the MMU registers have not been initialized. Once the MMU has been completely initialized, a WCMD instruction with a command value of 0111 globally enables MMU translation.

A WCMD instruction with a command value of 1111 enables the special MMU translation circuitry, which maps logical pages 0-3 and 5. Note that the special MMU enable information is volatile. That is, the enabled state is lost when the NEWT is powered down.

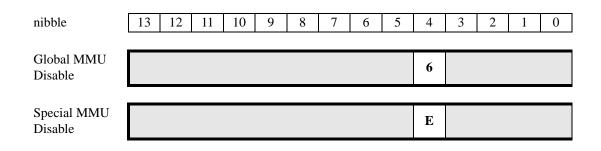

It is also possible to globally disable MMU translation. A WCMD instruction with a command value of 0110 globally disables MMU translation. Both of these commands are buffered, and do not take effect until the Program Counter returns to one of the Operating System pages (0, 1 or 2). This function is necessary to protect the software that enables or disables the MMU from having "the rug yanked out from underneath it" when the MMU programming changes. A WCMD instruction with a command value of 1110 disables the special MMU translation circuitry, returning pages 0-3 and 5 to their normal locations in Flash memory.

A command value of 0010 identifies a write to a logical address, while a command value of 0011 identifies a read from a logical address. The logical address is specified in digits 9-6 and the bank select value in digit 5. This logical address is automatically translated to a physical address and for a write all 16 bits of data in digits 3-0 are written to the external word-wide memory.

For a read the memory data is latched for and can be read via the on-chip I/O Port. Normally the write command will be used to write to the external RAM, but it can also be used to write to the external Flash memory.

| nibble                   | 13 | 12 | 11 | 10 | 9  | 8      | 7      | 6  | 5    | 4 | 3 | 2  | 1   | 0 |

|--------------------------|----|----|----|----|----|--------|--------|----|------|---|---|----|-----|---|

| Write Logical<br>Address |    |    |    |    | lo | ogical | addres | 55 | bank | 2 |   | da | ita |   |

| Read Logical<br>Address  |    |    |    |    | lo | ogical | addres | 5S | bank | 3 |   |    |     |   |

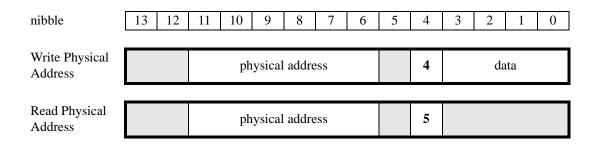

A command value of 0100 identifies a write directly to a physical address, while a command of 0101 identifies a read from a physical address. The physical address specified in digits 11-6. For a write all 16 bits of data in digits 3-0 are written to the external word-wide memory.

For a read the memory data is latched for and can be read via the on-chip I/O Port. Normally the write command will be used to write to the external RAM, but it can also be used to write to the external Flash memory.

Most of the remaining command values are used to control the turbo mode. This is detailed in the Turbo Mode chapter.

The NEWT design automatically latches the bank change information by monitoring the CPU instruction execution. Even though the MMU mapping occurs as a function of the current 4K page and selected bank, there are actually only seven bank select registers. This is consistent with the original HP-41C implementation of the memory bank function. The seven sets of bank select registers are for Page 5, Page 6, Page 7, Port 1 (Pages 8 and 9), Port 2 (Pages A and B), Port 3 (Pages C and D) and Port 4 (Pages E and F). Even though a pair of 4K pages may share a bank select register, each individual 4K page and bank select combination is individually mapped into the physical memory by the MMU. If a particular 4K page does not require separate mapping for each bank, the MMU translation for each bank should still be programmed, in this case pointing to the same 4K page in physical memory.

Note that the MMU registers are not stored in the NEWT microprocessor itself. Rather, they are stored in the 4K page of physical memory starting at address 0x804000. This allows the NEWT microprocessor to be powered down while retaining all data stored in the external RAM memory.

Both the register memory area of physical memory (at physical addresses 0x80000-0x803FFF) and the MMU area of physical memory (at physical addresses 0x804000-0x804FFF) are managed automatically by the NEWT microprocessor itself. Care should be exercised accessing these areas via a user programs.

# **Instruction Set**

This chapter presents the NEWT instruction set, including the assembly language syntax, operands, Carry flag settings, binary encoding, and execution time. The entire instruction set, including those peripheral instructions that affect the CPU, is presented in alphabetical order. Many of the restrictions present in the original NUT instruction set have been eliminated and these differences will be listed in notes at the end of individual instruction descriptions.

All unused binary encodings execute as NOP as far as the CPU is concerned. However, a number of these encodings are interpreted by logic external to the CPU. In some cases this logic is part of the NEWT design, and in other cases the logic is external to the NEWT design. Unused opcodes always execute at normal bus speed for compatibility.

The assembly language syntax is shown here identical to that used by the original HP assembler. At least two other sets of assembly language syntax exist, but no attempt will be made here to support them.

The operation of each instruction is specified in a format similar to Verilog HDL for minimum ambiguity, but no descriptive text or examples are included. In these descriptions bits and bit fields are enclosed in square brackets [ and ]. In addition, digits (nibbles) and digit fields ar enclosed in triangular brackets < and >. In those cases where more than one operation takes place concurrently, such as in register exchanges, the individual operations that occur simultaneously are enclosed by a Verilog fork-join pair.

The effect of the instruction on the Carry flag is listed separately. In addition, the effect of the two operating modes, Decimal/Hexadecimal and Turbo, are also listed.

Fields in the instruction are listed using shortcuts for common fields. These shortcuts should be self-explanatory in most cases, but will be detailed here for completeness.

The most common field in the instruction specifies a Time Enable Field (shown as TEF), employing the following shortcuts:

| Encoding | Mnemonic | Meaning                     |

|----------|----------|-----------------------------|

| 000      | PT       | On Pointer                  |

| 001      | Х        | Exponent & Sign             |

| 010      | WPT      | Word Through Pointer        |

| 011      | W        | Whole Word                  |

| 100      | PQ       | Pointer P through Pointer Q |

| 101      | XS       | Exponent Sign               |

| 110      | М        | Mantissa Only               |

| 111      | S        | Mantissa Sign               |

The second common field (shown as dddd) selects one of the fourteen digits or digit times during execution. Thus this field has only fourteen valid values, leaving two unused or illegal values. Often these two illegal values will be used to encode an entirely different instruction. Hence the apparent overlap of instruction encodings. The valid encodings are shown in the table below.

| Encoding | Mnemonic | Digit                    |

|----------|----------|--------------------------|

| 0000     | 3        | 3 (Mantissa digit 0)     |

| 0001     | 4        | 4 (Mantissa digit 1)     |

| 0010     | 5        | 5 (Mantissa digit 2)     |

| 0011     | 10       | 10 (Mantissa digit 7)    |

| 0100     | 8        | 8 (mantissa digit 5)     |

| 0101     | 6        | 6 (Mantissa digit 3)     |

| 0110     | 11       | 11 (Mantissa digit 8)    |

| 0111     |          | illegal encoding         |

| 1000     | 2        | 2 (Exponent Sign digit)  |

| 1001     | 9        | 9 (Mantissa digit 6)     |

| 1010     | 7        | 7 (Mantissa digit 4)     |

| 1011     | 13       | 13 (Mantissa sign digit) |

| 1100     | 1        | 1 (Exponent digit 1)     |

| 1101     | 12       | 12 (Mantissa digit 9)    |

| 1110     | 0        | 0 (Exponent digit 0)     |

| 1111     |          | illegal encoding         |

The third common field (shown as nnnn) selects one of sixteen values, registers (in the NUT sense) or peripherals, using standard binary encoding.

### **?A#0**

### **Test A Not Equal To Zero**

| ?A#0               | operand: Time Enable Field                                                            |              |                |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------|--------------|----------------|--|--|--|--|

| Operation:         | CY <= (A <time_enable_field< th=""><th>l&gt; != 0)</th><th></th></time_enable_field<> | l> != 0)     |                |  |  |  |  |

| Flag:              | Set if A is not zero at any time during the Time Enable Field; cleared otherwise.     |              |                |  |  |  |  |

| Dec/Hex:<br>Turbo: | Independent<br>Independent                                                            |              |                |  |  |  |  |

|                    | Assembly Syntax                                                                       | Encoding     | Machine Cycles |  |  |  |  |

|                    | ?A#0 TEF                                                                              | 1101_0TEF_10 | 1              |  |  |  |  |

|                    |                                                                                       |              |                |  |  |  |  |

### **?A#C**

### Test A Not Equal To C

| operand: Time Enable Field                                                                    |                                                                                               |                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY <= (A <time_enable_field> != C<time_enable_field>)</time_enable_field></time_enable_field> |                                                                                               |                                                                                                                                                                                                                     |

| Set if A is not equal to C at any time during the Time Enable Field; cleared otherwise.       |                                                                                               |                                                                                                                                                                                                                     |

| Independent<br>Independent                                                                    |                                                                                               |                                                                                                                                                                                                                     |

| Assembly Syntax                                                                               | Encoding                                                                                      | Machine Cycles                                                                                                                                                                                                      |

| ?A#C TEF                                                                                      | 1101_1TEF_10                                                                                  | 1                                                                                                                                                                                                                   |

|                                                                                               | Set if A is not equal to C at any tim<br>Independent<br>Independent<br><b>Assembly Syntax</b> | CY <= (A <time_enable_field> != C<time_enable_field>) Set if A is not equal to C at any time during the Time Enable Field; Independent Independent Assembly Syntax Encoding</time_enable_field></time_enable_field> |

### ?A<B

### Test A Less Than B

|                                                                   | ?A <b tef<="" th=""><th>1100_1TEF_10</th><th>] 1</th></b>                                       | 1100_1TEF_10 | ] 1            |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------|----------------|

|                                                                   | Assembly Syntax                                                                                 | Encoding     | Machine Cycles |

| Dec/Hex:<br>Turbo:                                                | Independent<br>Independent                                                                      |              |                |

| Flag:                                                             | Set if A is less than B, for the bits during the Time Enable Field; cleared otherwise.          |              |                |

| Operation:                                                        | CY <= (A <time_enable_field> &lt; B<time_enable_field>)</time_enable_field></time_enable_field> |              |                |

| ?A <b< th=""><th colspan="3">operand: Time Enable Field</th></b<> | operand: Time Enable Field                                                                      |              |                |

### Test A Less Than C

| ?A <c< th=""><th colspan="3">operand: Time Enable Field</th></c<> | operand: Time Enable Field                                                                      |              |                |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------|----------------|

| Operation:                                                        | CY <= (A <time_enable_field> &lt; C<time_enable_field>)</time_enable_field></time_enable_field> |              |                |

| Flag:                                                             | Set if A is less than C, for the bits during the Time Enable Field; cleared otherwise           |              |                |

| Dec/Hex:<br>Turbo:                                                | Independent<br>Independent                                                                      |              |                |

|                                                                   | Assembly Syntax                                                                                 | Encoding     | Machine Cycles |

|                                                                   | ?A <c tef<="" th=""><th>1100_0TEF_10</th><th>1</th></c>                                         | 1100_0TEF_10 | 1              |

### **?B#0**

### **Test B Equal To Zero**

| operand: Time Enable Field                                                        |                                                                                             |                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY <= (B <time_enable_field> !=</time_enable_field>                               | = 0)                                                                                        |                                                                                                                                                                                                      |

| Set if B is not zero at any time during the Time Enable Field; cleared otherwise. |                                                                                             |                                                                                                                                                                                                      |

| Independent<br>Independent                                                        |                                                                                             |                                                                                                                                                                                                      |

| Assembly Syntax                                                                   | Encoding                                                                                    | Machine Cycles                                                                                                                                                                                       |

| ?B#0 TEF                                                                          | 1011_0TEF_10                                                                                | 1                                                                                                                                                                                                    |

|                                                                                   | Set if B is not zero at any time du<br>Independent<br>Independent<br><b>Assembly Syntax</b> | CY <= (B <time_enable_field> != 0)         Set if B is not zero at any time during the Time Enable Field; cleare         Independent         Independent         Assembly Syntax</time_enable_field> |

### **?C#0**

### Test C Equal To Zero

| ?C=0               | operand: Time Enable Field                                                           |                                      |                |

|--------------------|--------------------------------------------------------------------------------------|--------------------------------------|----------------|

| Operation:         | CY <= (C <time_enable_field< th=""><th>&gt; != 0)</th><th></th></time_enable_field<> | > != 0)                              |                |

| Flag:              | Set if C is not zero at any time                                                     | e during the Time Enable Field; clea | red otherwise. |

| Dec/Hex:<br>Turbo: | Independent<br>Independent                                                           |                                      |                |

|                    | Assembly Syntax                                                                      | Encoding                             | Machine Cycles |

|                    | ?C#0 TEF                                                                             | 1011_1TEF_10                         | 1              |

## ?Fd=1

**Test Flag Input Equal to One**

| operand: Digit Number                                                 |                                                                                                             |                                                                                                                                                                   |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY <= FI <digit></digit>                                              |                                                                                                             |                                                                                                                                                                   |

| Set/Cleared to match the selected F                                   | ïlag Input                                                                                                  |                                                                                                                                                                   |

| Independent<br>Automatically fetched and executed at normal bus speed |                                                                                                             |                                                                                                                                                                   |

| Assembly Syntax                                                       | Encoding                                                                                                    | Machine Cycles                                                                                                                                                    |

| ?Fd=1                                                                 | dddd_1011_00                                                                                                | 1                                                                                                                                                                 |

|                                                                       | Set/Cleared to match the selected F<br>Independent<br>Automatically fetched and executed<br>Assembly Syntax | CY <= FI <digit> Set/Cleared to match the selected Flag Input Independent Automatically fetched and executed at normal bus speed Assembly Syntax Encoding</digit> |

**Note:** The flag input, **fi\_bus**, is sampled near the middle of the appropriate digit time (on the falling edge of the second **ph1** clock) during the execution phase of this instruction. The following flags are currently used in an HP-41 system:

| flag number | device           | Mnemonic | Used for                   |

|-------------|------------------|----------|----------------------------|

| 0           | 82143A<br>82242A | ?PBSY    | Printer Busy               |

| 1           | 82104A           | ?CRDR    | Card Reader                |

| 2           | 82153A           | ?WNDB    | Wand Byte Available        |

| 5           | 82242A           | ?EDAV    | Emitter Diode Available    |

| 6           | 82160A           | ?IFCR    | Interface Clear Received   |

| 7           | 82160A           | ?SRQR    | Service Request Received   |

| 8           | 82160A           | ?FRAV    | Frame Available            |

| 9           | 82160A           | ?FRNS    | Frame Received Not As Sent |

| 10          | 82160A           | ?ORAV    | Output Register Available  |

| 12          | 82182A           | ?ALM     | Alarm                      |

| 13          | all              | ?SER     | Service Request            |

## ?LLD

### Low Level Detect

| ?LLD               | operand: none                           |                                     |                |

|--------------------|-----------------------------------------|-------------------------------------|----------------|

| Operation:         | CY <= low_battery_status                |                                     |                |

| Flag:              | Set if the <b>lld</b> input is Low, sig | naling a Low Battery; cleared other | wise.          |

| Dec/Hex:<br>Turbo: | Independent<br>Independent              |                                     |                |

|                    | Assembly Syntax                         | Encoding                            | Machine Cycles |

|                    | ?LLD                                    | 0101_1000_00                        | 1              |

# **?P=Q**

### Test P Equal To Q

|                    | ?P=Q                              | 0100_1000_00 | ] 1            |

|--------------------|-----------------------------------|--------------|----------------|

|                    | Assembly Syntax                   | Encoding     | Machine Cycles |

| Dec/Hex:<br>Turbo: | Independent<br>Independent        |              |                |

| Flag:              | Set if P equals Q; cleared otherw | ise.         |                |

| Operation:         | CY <= (P == Q)                    |              |                |

| ?P=Q               | operand: none                     |              |                |

## ?PFLGn=1

### **Test Peripheral Flag N**

| ?PFLGn=1           | operand: none                                   |              |                |

|--------------------|-------------------------------------------------|--------------|----------------|

| Operation:         | CY <= Peripheral Flag n                         |              |                |

| Flag:              | Set/Cleared as a result of the test             |              |                |

| Dec/Hex:<br>Turbo: | Independent<br>Automatically executed at normal | bus speed.   |                |

|                    | Assembly Syntax                                 | Encoding     | Machine Cycles |

|                    | ?PFLGn=1                                        | nnnn_0000_11 | 1              |

|                    |                                                 |              |                |

**Note:** This instruction is only available while a peripheral is in control of the bus, and automatically returns control of the bus to the CPU. Peripherals may have up to sixteen flags to communicate information to the CPU via this instruction. The active peripheral drives the state of the selected flag on the **isa\_bus** during the first clock cycle of the following bus cycle. Thus the next instruction, which will be executed by the CPU, should be a conditional branch. This next instruction will always be executed at normal bus speed to allow the active peripheral time to respond.

## **?PT**=

### **Test Pointer Equal To**

| ?PT=               | operand: Digit Number            |                                         |                |

|--------------------|----------------------------------|-----------------------------------------|----------------|

| Operation:         | CY <= (PT == digit)              |                                         |                |

| Flag:              | Set if the pointer is equal to t | the dddd field in the instruction; clea | red otherwise. |

| Dec/Hex:<br>Turbo: | Independent<br>Independent       |                                         |                |

|                    | Assembly Syntax                  | Encoding                                | Machine Cycles |

|                    | ?PT= d                           | dddd_0101_00                            | 1              |

|                    |                                  |                                         |                |

**Note:** In the original NUT implementation this instruction cannot immediately follow an arithmetic (type 10) instruction. This restriction is not present in the NEWT implementation.

# ASL

Shift Left A

| ASL                | operand: Time Enable Field                                                                          |              |                |

|--------------------|-----------------------------------------------------------------------------------------------------|--------------|----------------|

| Operation:         | A <time_enable_field> &lt;= A<time_enable_field> &lt;&lt; 1</time_enable_field></time_enable_field> |              |                |

| Flag:              | Cleared                                                                                             |              |                |

| Dec/Hex:<br>Turbo: | Independent (no decimal adjust)<br>Independent                                                      |              |                |

|                    | Assembly Syntax                                                                                     | Encoding     | Machine Cycles |

|                    | ASL TEF                                                                                             | 1111_1TEF_10 | 1              |

Note: Zero is shifted into the least-significant (time-enabled) digit.

# ASR

| operand: Time Enable Field                                                                          |                                                                              |                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <time_enable_field> &lt;= A<time_enable_field> &gt;&gt; 1</time_enable_field></time_enable_field> |                                                                              |                                                                                                                                                                                                         |

| Cleared                                                                                             |                                                                              |                                                                                                                                                                                                         |

| Independent (no decimal adjust)<br>Independent                                                      |                                                                              |                                                                                                                                                                                                         |

| Assembly Syntax                                                                                     | Encoding                                                                     | Machine Cycles                                                                                                                                                                                          |

| ASR TEF                                                                                             | 1110_0TEF_10                                                                 | 1                                                                                                                                                                                                       |

|                                                                                                     | Cleared<br>Independent (no decimal adjust)<br>Independent<br>Assembly Syntax | A <time_enable_field> &lt;= A<time_enable_field> &gt;&gt; 1         Cleared         Independent (no decimal adjust)         Independent         Assembly Syntax</time_enable_field></time_enable_field> |

Note: Zero is shifted into the most-significant (time-enabled) digit.

Clear A

| A=0                | operand: Time Enable Field                        |              |                |

|--------------------|---------------------------------------------------|--------------|----------------|

| Operation:         | A <time_enable_field> &lt;= 0</time_enable_field> |              |                |

| Flag:              | Cleared                                           |              |                |

| Dec/Hex:<br>Turbo: | Independent<br>Independent                        |              |                |

|                    | Assembly Syntax                                   | Encoding     | Machine Cycles |

|                    | A=0 TEF                                           | 0000_0TEF_10 | 1              |

### A=A+1

### **Increment A**

| A=A+1              | operand: Time Enable Field                                                                         |              |                |

|--------------------|----------------------------------------------------------------------------------------------------|--------------|----------------|

| Operation:         | {CY, A <time_enable_field>} &lt;= A<time_enable_field> + 1</time_enable_field></time_enable_field> |              |                |

| Flag:              | Set/Cleared as a result of the operation                                                           |              |                |

| Dec/Hex:<br>Turbo: | Decimal adjusted in Decimal Mode<br>Independent                                                    |              |                |

|                    | Assembly Syntax                                                                                    | Encoding     | Machine Cycles |

|                    | A=A+1 TEF                                                                                          | 0101_1TEF_10 | 1              |

|                    |                                                                                                    |              |                |

## A = A + B

### Load A With A + B

| operand: Time Enable Field                                                                                                                |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| {CY, A <time_enable_field>} &lt;= A<time_enable_field> + B<time_enable_field></time_enable_field></time_enable_field></time_enable_field> |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Set/Cleared as a result of the operation                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |