# **Y51 Microcontroller**

## **Technical Manual**

#### Disclaimer

Systemyde International Corporation reserves the right to make changes at any time, without notice, to improve design or performance and provide the best product possible. Systemyde International Corporation makes no warrant for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make any commitment to update the information contained herein.

Systemyde International Corporation products are not authorized for use in life support devices or systems unless a specific written agreement pertaining to such use is executed between the manufacturer and the President of Systemyde International Corporation. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents, copyrights or other rights of third parties. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Systemyde International Corporation. All trademarks are trademarks of their respective companies.

Every effort has been made to ensure the accuracy of the information contain herein. If you find errors or inconsistencies please bring them to our attention. In all cases, however, the Verilog HDL source code for the Y51 design defines "proper operation".

Copyright © 2013, Systemyde International Corporation. All rights reserved.

Notice:

"Intel" and "8051" are registered trademarks of Intel, Inc. All uses of these terms in this document are to be construed as adjectives, whether or not the noun "microprocessor", "microcontroller", "CPU" or "device" are actually present.

## Table of Contents

| 1. Introduction               |   |

|-------------------------------|---|

| 2. Features                   |   |

| 3. Pin Descriptions           | 7 |

| 4. External Timing            |   |

| 5. Instruction Set            |   |

| 6. Special Function Registers |   |

| 7. CPU Registers              |   |

| 8. System Registers           |   |

| 9. Interrupt Control          |   |

| 10. Parallel Ports            |   |

| 11. Timer/Counters            |   |

| 12. Serial Port               |   |

|                               |   |

# **Revison History**

| Date       | Changes                                             | Page(s) |

|------------|-----------------------------------------------------|---------|

| 10/20/2012 | Preliminary issue                                   |         |

| 06/28/2013 | Added details for peripherals                       |         |

| 07/18/2013 | corrected JBC operation details; typos and spelling |         |

| 08/16/2013 | TCON register description                           | 94      |

| 08/22/2013 | Timer operation                                     |         |

|            |                                                     |         |

# Introduction

This publication documents the operation of the Y51 microcontroller. This CPU design is supplied in Verilog HDL and can be implemented in any technology supported by a logic synthesis tool that accepts Verilog HDL. Included in the design package is a test bench that exercises all instructions, flag settings, and representative data patterns. The test patterns should achieve at least 95% fault coverage.

The Y51 CPU was designed in a clean-room environment and is compatible with the Intel 8051 microcontroller. Only publicly available documentation was used to create this design so there may be minor differences where the public documentation is misleading or lacking. The instruction execution times are not identical between the two designs. The Y51 CPU operates with a consistent two-clock-cycle machine cycle, while the 8051 microcontroller uses a machine cycle with six clock cycles.

This document should always be used as the final word on the operation of the Y51 CPU, but it is useful to refer to the Intel documentation if the description given here is too cryptic. The 8051 architecture is over thirty years old, so it is assumed that it is already at least somewhat familiar to the reader.

The Y51 CPU is accompanied by full design documentation, in the form of a large spreadsheet, which describes nearly every facet of the internal operation of the processor. This provides knowledgeable users the opportunity to customize the design for unique application requirements.

# Features

- \* Fully functional synthesizable Verilog HDL version of the 8051/8052 CPU

- \* Vendor and technology independent

- \* Software compatible with several industry-standard processors

- \* Static, fully synchronous design uses no 3-state buses

- \* Uniform 2 clock-cycle machine cycle

- \* All memory interfaces match common synchronous FPGA and ASIC memory timing

- \* Program memory and External RAM memory share address and data buses

- \* Separate strobes for Program Memory and External RAM memory

- \* Separate Special Function Register (SFR) bus with dedicated strobes

- \* Internal RAM uses FPGA memory macros

- \* Four Parallel Ports

- \* Two Timer/Counters

- \* One serial channel

- \* Two additional internal interrupts for additional peripherals

- \* Full design documentation included

- \* Verilog simulation and test suite included

# **Interface Description**

This CPU design makes no attempt to match the signals or timing present on the 8051 microprocessor. Rather, all of the bus interfaces and signals are optimized for use in either an ASIC or an FPGA. The interface signals for the design are detailed below.

#### **CLOCK and RESET**

The design uses a single clock and single reset. No clock gating is employed in the design.

- **clk** (input, active-High) The rising edge of the Master Clock samples all inputs except for the asynchronous reset and all outputs normally change in response to the rising edge of the Master Clock.

- **resetb** (input, active-Low) The Master Reset signal is used to initialize all state flip-flops, and user registers consistent with the original 8051 design. This is an asynchronous signal, but the trailing edge should be synchronized with the rising edge of the Master Clock.

#### **PROGRAM MEMORY and EXTERNAL RAM**

The interface for Program Memory and External RAM consists of a single 16-bit address bus and separate buses for read data and write data. Program Memory and External RAM accesses use separate strobes. The cycle time for this these buses is two clock cycles.

- **mem\_addr** (output, 16-bit bus) The Memory Address bus carries the address all Program Memory read transactions, as well as External RAM read and write transactions.

- **mem\_rdata** (input, 8-bit bus) The Memory Read Data bus is sampled during Program Memory and External RAM read transactions.

- mem\_rd (output, active-High) The Memory Read signal is one clock cycle wide and identifies the data transfer clock cycle for Program Memory read transactions. There is no corresponding Memory Write signal, because the 8051 architecture does not support writing to Program Memory.

- **mem\_wdata** (output, 8-bit bus) The Memory Write Data bus carries the output data for External RAM write transactions. To conserve power, this bus only changes state as required for a memory write.

- **ph** (output, active-High) The Bus Phase signal is High during the first clock of a machine cycle and Low during the second clock of a machine cycle.

- xram\_rd (output, active-High) The External RAM Read signal is one clock cycle wide and identifies the data transfer clock cycle for External RAM read transactions.

- xram\_wr (output, active-High) The External RAM Write signal is one clock cycle wide and identifies the data transfer clock cycle for External RAM write transactions.

#### **SPECIAL FUNCTION REGISTERS**

Access to external Special Function Registers is via the SFR bus. The SFR bus operates with a one-clock cycle time, and simultaneous reads and writes are not possible. Internal Special Function Registers do not use this bus, but are directly connected internally in the design.

- **sfr\_addr** (output, 7-bit bus) The Special Function Register Address bus carries the address for Special Function Register transactions. This bus only valid during Special Function Register transfers.

- sfr\_rd (output, active-High) The Special Function Register Read Enable signal identifies data transfer clock cycles for Special Function Register read transactions.

- **sfr\_rdata** (input, 8-bit bus) The Special Function Register Read Data bus is sampled by the clock when the **sfr\_rd** signal is active and an external Special Function Register is addressed.

- **sfr\_wdata** (output, 8-bit bus) The Special Function Register Write Data bus carries the output data for Special Function Register write transactions. This bus is valid only during Special Function write operations.

- **sfr\_wr** (output, active-High) The Special Function Register Write Enable signal identifies data transfer clock cycles for Special Function Register write transactions.

#### **INTERRUPTS**

The design supports two external interrupt requests, and provides an output to signal that an interrupt acknowledge is in progress. The two "internal" interrupt requests are intended for use with on-chip peripherals beyond those native to the design.

- **ext0\_int, ext1\_int** (input, active-High) The standard External Interrupt Request signals can be independently programmed to be either level-sensitive or edge-triggered. In the case of a level triggering the interrupt request must be deasserted before the end of the interrupt service routine. Edge-triggered interrupts are sampled by the Master Clock to recognize a rising edge. This information is latched until the interrupt is acknowledged, at which point the hardware will automatically clear the latched status.

- int0\_int, int1\_int (input, active-High) The new Internal Interrupt Request signals are always level-sensitive. These inputs are not synchronized, because it is assumed that they will be generated by on-chip peripheral devices.

- **intack** (output, active-High) The Interrupt Acknowledge signal is active for two clock cycles to indicate that an interrupt acknowledge sequence is in progress.

#### PARALLEL PORTS

The parallel port functionality is implemented as separate inputs and outputs. There is no multiplexing with address or data information or other peripheral functionality, to make the design as general-purpose as possible.

- p0\_in, p1\_in, p2\_in, p3\_in (input, 8-bit bus) The state of the Port inputs is returned during reads of the port data registers unless the read is part of a read-modifywrite instruction. In this case the port output data register will be returned to allow for proper modify operation.

- p0\_out, p1\_out, p2\_out, p3\_out (output, 8-bit bus) The Port outputs reflect the contents of the port output data registers.

#### TIMER/COUNTERS

The design includes the two timer/counters found in the 8052. To ensure backwards compatibility, these timers are clocked at 1/12 the rate of the Master Clock.

**t0\_cnt**, **t1\_cnt** (input, active-High) The Timer x Count signals are used in the counter mode of operation to cause the counter to increment. After synchronization,

these inputs are sampled at the timer clock rate to detect a falling edge. The falling edge cause the counter to increment.

- **t0\_gate, t1\_gate** (input, active-High) The Timer x Gate signals are used to enable the count signal, in either timer or counter mode. This function is enabled or disabled under program control.

- **t0\_out, t1\_out** (output, active-High) The Timer x Output signals are active for one clock cycle (of the Master Clock) when the counter/timer overflows or is reloaded.

#### SERIAL CHANNEL

The design includes the basic serial channel found in the 8051. Backwards-compatible enhancements provide more error reporting and improved features.

- **rxd\_in** (input, active-High) The Receive Data Input signal is the data input for the serial channel.

- **syn\_dir** (output) The Synchronous Direction signal indicates the transfer direction for the serial data in the synchronous mode. Low indicates data reception and High indicates data transmission.

- **txc\_out** (output, active-High) The Transmit Clock Output signal outputs the data clock in the synchronous mode. This signal is inactive (Low) when the serial channel is in a UART mode.

- **txd\_out** (output, active-High) The Transmit Data Output signal is the data output for the serial channel.

#### **UNCOMMITTED OUTPUTS**

The design includes two uncommitted 8-bit Special Function Registers, called PCON (Power Control) and ECOM (Extended Control), which can be used in a system for hard-ware control.

- econ\_reg (output, 8-bit bus) The Extended Control register is intended for hardware control of logic external to the CPU.

- **pcon\_reg** (output, 8-bit bus) The Power Control register is intended for hardware control of power-control logic external to the CPU.

# **External Timing**

This CPU design uses a uniform two-clock-cycle machine cycle. This consistent timing simplifies the design of logic external to the CPU makes it easier to track the state of the CPU.

The program memory interface timing and signals are designed to make it easy to interface to standard ASIC and FPGA memories. This interface uses separate read and write strobes.

The SFR interface is similar to the AMBA Peripheral Bus (APB), except that it uses separate read and write strobes. The only timing difference relative to the APB is the setup time for the write data. In the APB the write data is setup one clock before the strobe; in this interface the write data changes coincident with the leading edge of the strobe. In most cases this will not be a problem.

In the diagrams below only the relevant signals are shown for each transaction. All other signals are either inactive or hold the previous value.

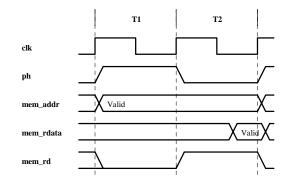

## **Program Memory Read**

The figure below shows a Program Memory read transaction. Program Memory is readonly.

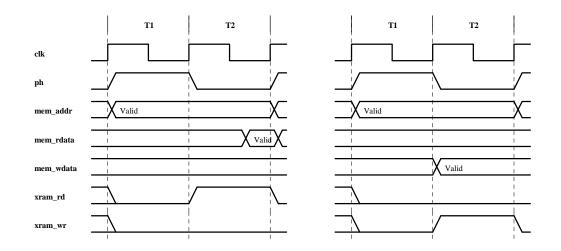

## **External RAM Read and Write**

The figures below show read and write transactions with External RAM.

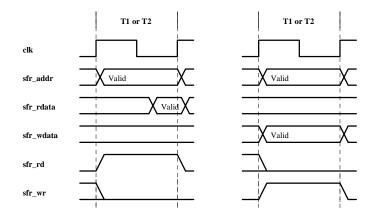

### SFR Read and Write

The figures below show read and write transactions on the SFR interface. Unlike the Program Memory and External RAM interfaces, the SFR interface uses one clock-cycle timing. The **sfr\_addr** and **sfr\_wdata** buses are driven with all zeros when not in use, but since they are also used to carry information to the internal Special Function Registers as well as the Internal RAM, these buses will carry non-zero information at other times. External Special Function Registers must use the **sfr\_rd** and **sfr\_wr** strobes to read and write information.

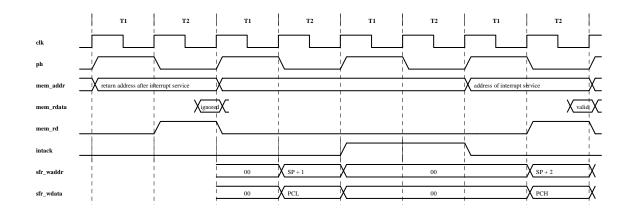

## **Interrupt Acknowledge**

The figure below shows the interrupt acknowledge transaction, including the preceding aborted instruction fetch and dummy cycle, and subsequent instruction fetch for the service routine. The **sfr\_addr** and **sfr\_wdata** buses are also shown to indicate where the internal RAM is written.

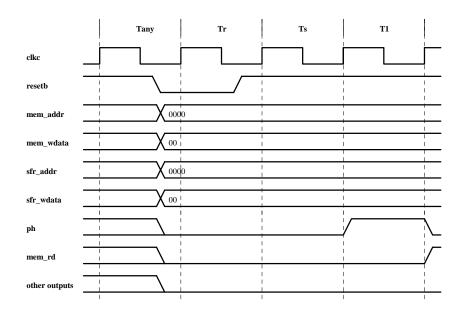

### Reset

The Reset state is entered immediately when the **resetb** signal goes Low, independent of the current state, and this state continues until the first rising edge of **clk** after the **resetb** signal is de-asserted. At this rising edge there is a one clock cycle transient state to set up the internal pipeline controls, and on the next clock the processor begins fetching the first instruction from address 0x0000.

The minimum width of the **resetb** signal is set by the flip-flops used in the design. The setup time for the **resetb** signal to the rising edge of the **clk** signal is likewise determined by the flip-flops used in the design.

# **Instruction Set**

This chapter presents the assembly language syntax, addressing modes, flag settings, binary encoding, and execution time for the Y51 instruction set. The entire instruction set is presented in alphabetical order.

The assembly language syntax is identical to that used by the original Intel assembler. Different assembler programs may or may not use identical syntax. The syntax is presented generically at the beginning of each instruction, with the details presented for each addressing mode later in each entry.

The operation of each instruction is specified in a format similar to Verilog HDL for minimum ambiguity, but no descriptive text or examples are included.

The effect of the instruction on each flag is listed, with a brief description. The flags are organized as shown below in the PSW (Processor Status Word) register:

| СҮ | AC | FO | RS1 | RS0 | OV | F1 | Р |

|----|----|----|-----|-----|----|----|---|

|----|----|----|-----|-----|----|----|---|

These flags have the following meanings:

| Flag     | Meaning                                                             |

|----------|---------------------------------------------------------------------|

| CY       | Carry (arithmetic carry, shift linkage bit, bit operation result).  |

| AC       | Auxiliary Carry (carry out of the lower nibble, used for BCD math). |

| F1, F0   | User Flags 1 and 0.                                                 |

| RS1, RS0 | Register Select control.                                            |

| OV       | Overflow (arithmetic overflow).                                     |

| Р        | Parity.                                                             |

Fields in the instruction are listed using shortcuts for common fields. These shortcuts should be self-explanatory in most cases, but will be detailed here for completeness.

The most common field in the instruction specifies a CPU register, employing the following encoding:

| rrr | <b>Register selected</b> |

|-----|--------------------------|

| 000 | R0                       |

| 001 | R1                       |

| 010 | R2                       |

| 011 | R3                       |

| 100 | R4                       |

| 101 | R5                       |

| 110 | R6                       |

| 111 | R7                       |

Indirect registers are similarly encoded:

| i | Indirect Register selected |

|---|----------------------------|

| 0 | R0                         |

| 1 | R1                         |

The execution time for instructions is always a multiple of two clocks.

|    | 0/8  | 1/9  | 2/A  | 3/B  | 4/C   | 5/D   | 6/E   | 7/F   |    |

|----|------|------|------|------|-------|-------|-------|-------|----|

| F8 | IP1  |      |      |      |       |       |       |       | FF |

| FO | в    |      |      |      |       |       |       |       | F7 |

| E8 |      |      |      |      |       |       |       |       | EF |

| EO | ACC  |      |      |      |       |       |       |       | E7 |

| D8 |      |      |      |      |       |       |       |       | DF |

| D0 | PSW  |      |      |      |       |       |       |       | D7 |

| C8 |      |      |      |      |       |       |       |       | CF |

| C0 |      |      |      |      |       |       |       |       | C7 |

| в8 | IP0  |      |      |      |       |       |       |       | BF |

| в0 | P3   |      |      |      |       |       |       |       | В7 |

| A8 | IE   |      |      |      |       |       |       |       | AF |

| A0 | P2   |      |      |      |       |       |       |       | A7 |

| 98 | SCON | SBUF | BRLL | BRLH | BRCON | ESCON | SADDR | SADEN | 9F |

| 90 | P1   |      |      |      |       |       |       |       | 97 |

| 88 | TCON | TMOD | TL0  | TL1  | TH0   | TH1   | RCON  | ECON  | 8F |

| 80 | P0   | SP   | DPL  | DPH  | DP1L  | DP1H  | DPS   | PCON  | 87 |

| 78 |      |      |      |      |       |       |       |       | 7F |

| 70 |      |      |      |      |       |       |       |       | 77 |

| 68 |      |      |      |      |       |       |       |       | 6F |

| 60 |      |      |      |      |       |       |       |       | 67 |

| 58 |      |      |      |      |       |       |       |       | 5F |

| 50 |      |      |      |      |       |       |       |       | 57 |

| 48 |      |      |      |      |       |       |       |       | 4F |

| 40 |      |      |      |      |       |       |       |       | 47 |

| 38 |      |      |      |      |       |       |       |       | 3F |

| 30 |      |      |      |      |       |       |       |       | 37 |

| 28 |      |      |      |      |       |       |       |       | 2F |

| 20 |      |      |      |      |       |       |       |       | 27 |

| 18 | R0   | Rl   | R2   | R3   | R4    | R5    | R6    | R7    | 1F |

| 10 | R0   | Rl   | R2   | R3   | R4    | R5    | R6    | R7    | 17 |

| 08 | R0   | Rl   | R2   | R3   | R4    | R5    | R6    | R7    | OF |

| 00 | R0   | R1   | R2   | R3   | R4    | R5    | R6    | R7    | 07 |

| CPU register set 0                  |

|-------------------------------------|

| CPU register set 1                  |

| CPU register set 2                  |

| CPU register set 3                  |

| Bit-addressable registers           |

| External Special Function Registers |

#### Notes:

1. Addresses 0x00-0x7F can be accessed using either a direct address or an indirect address.

2. Indirect addressing with addresses 0x80-0xFF accesses RAM.

3. Direct addressing with addresses 0x80-0xFF access the Special Function Registers.

4. RAM addresses 0x80-0xFF support multiple banks, depending on the technology used for the implementation.

5. Bit-addressed operations access addresses 0x20-0x2F in RAM and addresses 0x80, 0x88, 0x90... 0xE8, 0xF0 and 0xF8 in the Special Function Registers.

### ACALL Absolute Call

| ACALL addr11        |                                                                    |          |        |

|---------------------|--------------------------------------------------------------------|----------|--------|

| Operation:          | (SP+1) <= PCL<br>(SP+2) <= PCH<br>PC[10:0] <= addr11<br>SP <= SP+2 |          |        |

| Flags:              | C: Unaffected<br>AC: Unaffected<br>OV: Unaffected.                 |          |        |

| Addressing<br>Modes | Assembly Syntax                                                    | Encoding | Clocks |

|                     | ACALL addr11                                                       | aaa10001 | 4      |

#### Notes:

1. Bits 7:5 in the first opcode contain addr11[11:8].

2. The PC value used for PC[15:12] is the address of the next instruction.

## ADD

Add

| ADD A, src | src: R, DA, IR, IM                                                                                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | $A \le A + src$                                                                                                                                                                                               |

| Flags:     | <ul><li>C: Set if arithmetic carry out of bit 7; cleared otherwise.</li><li>AC: Set if arithmetic carry out of bit 3; cleared otherwise.</li><li>OV: Set if arithmetic overflow; cleared otherwise.</li></ul> |

| Addressing<br>Modes | Assembly Syntax | Encoding       | Clocks |

|---------------------|-----------------|----------------|--------|

| R:                  | ADD A, Rn       | 00101rrr       | ] 2    |

| DA:                 | ADD A, direct   | 00100101       | 4      |

|                     |                 | direct address | ]      |

| IR:                 | ADD A, @Ri      | 0010011i       | ] 4    |

| IM:                 | ADD A, #data    | 00100100       | 4      |

|                     |                 | immediate data |        |

| ADDC A, src | src: R, DA, IR, IM                                                                                                                                                                                            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:  | $A \le A + src + C$                                                                                                                                                                                           |

| Flags:      | <ul><li>C: Set if arithmetic carry out of bit 7; cleared otherwise.</li><li>AC: Set if arithmetic carry out of bit 3; cleared otherwise.</li><li>OV: Set if arithmetic overflow; cleared otherwise.</li></ul> |

| Addressing<br>Modes | Assembly Syntax | Encoding                   | Clocks |

|---------------------|-----------------|----------------------------|--------|

| R:                  | ADDC A, Rn      | 00111rrr                   | 2      |

| DA:                 | ADDC A, direct  | 00110101<br>direct address | 4      |

| IR:                 | ADDC A, @Ri     | 0011011i                   | 4      |

| IM:                 | ADDC A, #data   | 00110100<br>immediate data | 4      |

# AJMP

#### **Absolute Jump**

| AJMP addr11         |                                                    |                       |        |

|---------------------|----------------------------------------------------|-----------------------|--------|

| Operation:          | PC[11:0] <= addr11                                 |                       |        |

| Flags:              | C: Unaffected<br>AC: Unaffected<br>OV: Unaffected. |                       |        |

| Addressing<br>Modes | Assembly Syntax                                    | Encoding              | Clocks |

|                     | AJMP addr11                                        | aaa00001<br>addr[7:0] | 4      |

|                     |                                                    |                       |        |

Notes:

1. Bits 7:5 in the first opcode contain addr11[11:8].

2. The PC value used for PC[15:12] is the address of the next instruction.

### ANL Logical AND

| ANL A, src          |                                                      | src: R, DA, IR, IM         |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Operation:          | $A \le A \& src$                                     |                            |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

| R:                  | ANL A, Rn                                            | 01011rrr                   | 2      |

| DA:                 | ANL A, direct                                        | 01010101<br>direct address | 4      |

| IR:                 | ANL A, @Ri                                           | 0101011i                   | 4      |

| IM:                 | ANL A, #data                                         | 01010100<br>immediate data | 4      |

### **ANL** Logical AND with Memory

| ANL direct, src     |                                                      | src: A, IM                                   |        |

|---------------------|------------------------------------------------------|----------------------------------------------|--------|

| Operation:          | direct <= direct & src                               |                                              |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                              |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                                     | Clocks |

| Α                   | ANL direct, A                                        | 01010010<br>direct address                   | 4      |

| IM                  | ANL direct, #data                                    | 01010011<br>direct address<br>immediate data | 6      |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

### **ANL** Logical AND with Carry

| ANL C, src          | src: bit, /bit                                                                                                     |                         |        |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------|--------|--|

| Operation:          | $C \ll C$ & src, where src can be either a bit or the complement of a bit                                          |                         |        |  |

| Flags:              | <ul><li>C: Set/cleared with the result of the operation.</li><li>AC: Unaffected.</li><li>OV: Unaffected.</li></ul> |                         |        |  |

| Addressing<br>Modes | Assembly Syntax                                                                                                    | Encoding                | Clocks |  |

| Bit:                | ANL C, bit                                                                                                         | 10000010<br>bit address | 4      |  |

|                     | =                                                                                                                  |                         |        |  |

### **CJNE** Compare and Jump if Not Equal

| CJNE dst, src | e, offset src: DA, IM<br>dst: A, DA                                                              |

|---------------|--------------------------------------------------------------------------------------------------|

| Operation:    | if (dst != src) then begin<br>PC <= PC + offset<br>if (dst < src) then C <= 1 else C <= 0<br>end |

| Flags:        | C: Set if dst < src; cleared otherwise.<br>AC: Unaffected.<br>OV: Unaffected.                    |

| Addressing    | a                                                                                                |

| Addressing<br>Modes | Assembly Syntax         | Encoding                   | Clocks |

|---------------------|-------------------------|----------------------------|--------|

| DA:                 | CJNE A, src, offset     | 10110101                   | 8      |

|                     |                         | direct address             |        |

|                     |                         | address offset             |        |

| IM:                 | CINE A #data affaat     | 10110100                   | 8      |

| 11v1;               | CJNE A, #data, offset   | 10110100<br>immediate data | 0      |

|                     |                         |                            |        |

| IM:                 | CJNE Rn, #data, offset  | address offset             | 8      |

| 1111.               | CJNE KII, #data, offset | immediate data             | 0      |

|                     |                         | address offset             |        |

| IM:                 | CJNE @Ri, #data, offset | 1011011i                   | 8      |

|                     |                         | immediate data             |        |

|                     |                         | address offset             |        |

#### Notes:

1. The PC value used in the address calculation is the address of the next instruction.

2. For the comparison, the src and dst are treated as unsigned numbers.

| CLR A               |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | A <= 8'h00                                           |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | CLR A                                                | 11100100 | 2      |

# CLR

**Clear Bit**

| CLR dst             |                                                                          | dst: C, bit             |        |

|---------------------|--------------------------------------------------------------------------|-------------------------|--------|

| Operation:          | dst <= 1'b0                                                              |                         |        |

| Flags:              | C: Cleared if dst is C; unaffected of AC: Unaffected.<br>OV: Unaffected. | herwise.                |        |

| Addressing<br>Modes | Assembly Syntax                                                          | Encoding                | Clocks |

| C:                  | CLR C                                                                    | 11000011                | 2      |

| Bit:                | CLR bit                                                                  | 11000010<br>bit address | 4      |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

| CPL A               |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | A <= ~A                                              |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | CPL A                                                | 11110100 | 2      |

### **CPL** Complement Bit

| CPL dst             |                                                        | dst: C, bit                 |        |

|---------------------|--------------------------------------------------------|-----------------------------|--------|

| Operation:          | dst <= ~dst                                            |                             |        |

| Flags:              | C: Complemented if dst is C; unaffe<br>AC: Unaffected. | ected otherwise             |        |

|                     | OV: Unaffected.                                        |                             |        |

| Addressing<br>Modes | OV: Unaffected.<br>Assembly Syntax                     | Encoding                    | Clocks |

| -                   |                                                        | <b>Encoding</b><br>10110011 | Clocks |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

| DA A                |                                                                          |                 |        |

|---------------------|--------------------------------------------------------------------------|-----------------|--------|

| Operation:          | A <= Decimal Adjust A                                                    |                 |        |

| Flags:              | C: Set if result is negative; clea<br>AC: Unaffected.<br>OV: Unaffected. | ared otherwise. |        |

| Addressing<br>Modes | Assembly Syntax                                                          | Encoding        | Clocks |

|                     | DA A                                                                     | 11010100        | 2      |

Notes:

| C before | A[7:4]    | AC before | A[3:0]    | Number     | C after |

|----------|-----------|-----------|-----------|------------|---------|

| DA       | before DA | DA        | before DA | added to A | DA      |

| 0        | 0-9       | 0         | 0-9       | 00         | 0       |

| 0        | 0-8       | 0         | A-F       | 06         | 0       |

| 0        | 0-9       | 1         | 0-3       | 06         | 0       |

| 0        | A-F       | 0         | 0-9       | 60         | 1       |

| 0        | 9-F       | 0         | A-F       | 66         | 1       |

| 0        | A-F       | 1         | 0-3       | 66         | 1       |

| 1        | 0-2       | 0         | 0-9       | 60         | 1       |

| 1        | 0-2       | 0         | A-F       | 66         | 1       |

| 1        | 0-3       | 1         | 0-3       | 66         | 1       |

|          |           |           |           |            |         |

# DEC

#### Decrement

| <b>DEC</b> dst      |                                                      | dst: A, R, DA, IR        |        |  |  |

|---------------------|------------------------------------------------------|--------------------------|--------|--|--|

| Operation:          | dst <= dst - 1                                       |                          |        |  |  |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                          |        |  |  |

|                     |                                                      |                          |        |  |  |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                 | Clocks |  |  |

|                     | Assembly Syntax DEC A                                | <b>Encoding</b> 00010100 | Clocks |  |  |

| Modes               |                                                      |                          | 7      |  |  |

#### Notes:

IR:

DEC @Ri

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

0001011i

4

| DIV AB              |                                                                     |                       |        |

|---------------------|---------------------------------------------------------------------|-----------------------|--------|

| Operation:          | A <= A / B<br>B <= rem (A / B)                                      |                       |        |

| Flags:              | C: Cleared.<br>AC: Unaffected.<br>OV: Set if B = 0 before operation | r; cleared otherwise. |        |

| Addressing<br>Modes | Assembly Syntax                                                     | Encoding              | Clocks |

|                     | DIV AB                                                              | 10000100              | 6      |

|                     |                                                                     |                       |        |

#### Notes:

1. Both A and B are treated as unsigned numbers for the division.

## **DJNZ** Decrement, Jump if Non-Zero

| DJNZ dst, offse     | t                                                    | dst: R, DA                                             |        |

|---------------------|------------------------------------------------------|--------------------------------------------------------|--------|

| Operation:          | dst <= dst - 1<br>if (dst != 0) then PC <= PC + off  | fset                                                   |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                                        |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                                               | Clocks |

| R:                  | DJNZ Rn, offset                                      | 11011rrr<br>address offset                             | 6      |

| DA:                 | DJNZ direct, offset                                  | 11010101         direct address         address offset | 8      |

#### Notes:

1. The PC value used in the address calculation is the address of the next instruction.

2. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

| INC dst             |                                                      | dst: A, R, DA, IR          |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Operation:          | $dst \leq dst + 1$                                   |                            |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

| <b>A:</b>           | INC A                                                | 00000100                   | 2      |

| R:                  | INC Rn                                               | 00001rrr                   | 2      |

| DA:                 | INC direct                                           | 00000101<br>direct address | 4      |

| IR:                 | INC @Ri                                              | 0000011i                   | ] 4    |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

## INC Increment DPTR

## INC DPTR Operation: DPTR <= DPTR + 1</th> Flags: C: Unaffected. AC: Unaffected. OV: Unaffected. C: Unaffected. OV: Unaffected. Addressing Modes Assembly Syntax Encoding Clocks INC DPTR 10100011 2

| if (bit) then PC <= PC + offset                      |                                                                         |                                                                                                |

|------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                                                         |                                                                                                |

| Assembly Syntax                                      | Encoding                                                                | Clocks                                                                                         |

| JB bit, offset                                       | 00100000                                                                | ] 8                                                                                            |

|                                                      | bit address                                                             |                                                                                                |

|                                                      | address offset                                                          |                                                                                                |

|                                                      | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected.<br>Assembly Syntax | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected.<br>JB bit, offset 00100000<br>bit address |

#### Notes:

## **JBC** Jump if Bit Set and Clear Bit

#### JBC bit, offset

| Operation:          | if (bit) then PC <= PC + offset<br>bit <= 1'b0       |                                           |        |

|---------------------|------------------------------------------------------|-------------------------------------------|--------|

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                           |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                                  | Clocks |

|                     | JBC bit, offset                                      | 00010000<br>bit address<br>address offset | 8      |

#### Notes:

1. The PC value used in the address calculation is the address of the next instruction.

2. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

| if (C) then PC <= PC + offset                        |                                                                         |                                                                                  |

|------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                                                         |                                                                                  |

| Assembly Syntax                                      | Encoding                                                                | Clocks                                                                           |

| JC bit, offset                                       | 01000000<br>address offset                                              | 6                                                                                |

| -                                                    | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected.<br>Assembly Syntax | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected.<br>Assembly Syntax Encoding |

#### Notes:

## JMP

**Jump Indirect**

#### JMP @A+DPTR

| Operation:          | PC <= A + DPTR                                       |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | JMP @A+DPTR                                          | 01110011 | 4      |

Notes:

1. A is treated as an unsigned number for the addition.

| JNB bit, offset     |                                                      |                   |        |

|---------------------|------------------------------------------------------|-------------------|--------|

| Operation:          | if (!bit) then PC <= PC + offset                     |                   |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                   |        |

|                     |                                                      |                   |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding          | Clocks |

|                     | Assembly Syntax JNB bit, offset                      | Encoding 00110000 | Clocks |

|                     |                                                      |                   |        |

#### Notes:

## JNC Jump if Carry Clear

#### JNC bit, offset

| Operation:          | if (!C) then PC <= PC + offset                       |                            |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

|                     | JNC bit, offset                                      | 01010000<br>address offset | 6      |

Notes:

| Operation:          | if (A != 8'h00) then PC <= PC + of                   | fset     |        |

|---------------------|------------------------------------------------------|----------|--------|

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     |                                                      | 01110000 | 6      |

|                     | JNZ bit, offset                                      | 01110000 |        |

#### Notes:

JZ bit, offset

# Operation: if (A == 8'h00) then PC <= PC + offset</td> Flags: C: Unaffected. AC: Unaffected. OV: Unaffected. Addressing Modes Assembly Syntax Encoding Clocks JZ bit, offset 01100000 address offset 6

Notes:

## LCALL Long Call

| LCALL addr16        | 1                                                            |                        |        |

|---------------------|--------------------------------------------------------------|------------------------|--------|

| Operation:          | (SP+1) <= PCL<br>(SP+2) <= PCH<br>PC <= addr16<br>SP <= SP+2 |                        |        |

| Flags:              | C: Unaffected<br>AC: Unaffected<br>OV: Unaffected.           |                        |        |

| Addressing<br>Modes | Assembly Syntax                                              | Encoding               | Clocks |

| DA:                 | LCALL addr16                                                 | 00010010<br>addr[15:8] | 6      |

## LJMP

#### Long Jump

| Clocks |

|--------|

| 6      |

| -      |

## MOV

Move Byte to Accumulator

| MOV A, src          | src: R, DA, IR, IM                                   |                            |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Operation:          | A <= src                                             |                            |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

| R:                  | MOV A, Rn                                            | 11101rrr                   | 2      |

| DA:                 | MOV A, direct                                        | 11100101<br>direct address | 4      |

| IR:                 | MOV A, @Ri                                           | 1110011i                   | 4      |

| IM:                 | MOV A, #data                                         | 01110100<br>immediate data | 4      |

## MOV Move Byte to Register

| MOV Rn, src         |                                                      | src: A, DA, IM |        |

|---------------------|------------------------------------------------------|----------------|--------|

| Operation:          | Rn <= src                                            |                |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding       | Clocks |

| <b>A:</b>           | MOV Rn, A                                            | 11111rrr       | ] 2    |

| DA:                 | MOV Rn, direct                                       | 10101rrr       | 4      |

|                     |                                                      | direct address |        |

## MOV

#### Move Byte to Direct Address

| MOV direct, src     |                                                      | src: A, R, DA, IR, IM                                          |        |

|---------------------|------------------------------------------------------|----------------------------------------------------------------|--------|

| Operation:          | direct <= src                                        |                                                                |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                                                |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                                                       | Clocks |

| <b>A:</b>           | MOV direct, A                                        | 11110101<br>direct address                                     | 4      |

| R:                  | MOV direct, Rn                                       | 10001rrr<br>direct address                                     | 4      |

| DA:                 | MOV direct, direct                                   | 10000101         direct src address         direct dst address | 6      |

| IR:                 | MOV direct, @Ri                                      | 1000011i<br>direct address                                     | 4      |

| IM:                 | MOV direct, #data                                    | 01110101<br>direct address<br>immediate data                   | 6      |

## **MOV** Move Byte via Indirect Register

| MOV @Ri, src        |                                                      | src: A, DA, IM             |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Operation:          | @Ri <= src                                           |                            |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

| <b>A:</b>           | MOV @Ri, A                                           | 1111011i                   | ] 4    |

| DA:                 | MOV @Ri, direct                                      | 1010011i<br>direct address | 4      |

| IM:                 | MOV @Ri, #data                                       | 0111011i<br>immediate data | 4      |

### MOV Move Bit

| MOV dst, src        |                                                                  | src: bit, C<br>dst: bit, C |        |

|---------------------|------------------------------------------------------------------|----------------------------|--------|

| Operation:          | dst <= src                                                       |                            |        |

| Flags:              | C: Updated if destination.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                                  | Encoding                   | Clocks |

| C, bit:             | MOV C, bit                                                       | 10100010<br>bit address    | 4      |

| bit, C:             | MOV bit, C                                                       | 10010010<br>bit address    | 4      |

|                     |                                                                  |                            |        |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

## MOV Move to Data Pointer

| MOV DPTR, src |                                                      | src: IM  |        |

|---------------|------------------------------------------------------|----------|--------|

| Operation:    | DPTR <= src                                          |          |        |

| Flags:        | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing    |                                                      |          |        |

| Modes         | Assembly Syntax                                      | Encoding | Clocks |

## MOVC Move Code Byte

| MOVC A, src         |                                                      | src: DPTR-relative, PC-relative |        |

|---------------------|------------------------------------------------------|---------------------------------|--------|

| Operation:          | A <= src                                             |                                 |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                                 |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                        | Clocks |

| DPTRrel;            | MOVC A, @A+DPTR                                      | 10010011                        | 6      |

| PCrel:              | MOVC A, @A+PC                                        | 10000011                        | 6      |

#### Notes:

## MOVX

#### Move from External Byte

| MOVX A, src         |                                                      | src: DPTR, IR |        |

|---------------------|------------------------------------------------------|---------------|--------|

| Operation:          | A <= src                                             |               |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |               |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding      | Clocks |

| DPTR;               | MOVX A, @DPTR                                        | 11100000      | 6      |

| IR:                 | MOVX A, @Ri                                          | 1110001i      | 6      |

#### Notes:

1. External RAM uses the same address and data bus as Program Memory, but different data strobe signals.

2. When using register-indirect addressing, the upper byte of the address the contents of the Port 2 data output register.

## MOVX Move to External Byte

| MOVX dst, A         |                                                      | dst: DPTR, IR |        |

|---------------------|------------------------------------------------------|---------------|--------|

| Operation:          | dst <= A                                             |               |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |               |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding      | Clocks |

| DPTR                | MOVX @DPTR, A                                        | 11110000      | ] 6    |

| IR                  | MOVX @Ri, A                                          | 1111001i      | 6      |

#### Notes:

1. External RAM uses the same address and data bus as Program Memory, but different data strobe signals.

2. When using register-indirect addressing, the upper byte of the address the contents of the Port 2 data output register.

## MUL

#### Multiply

#### MUL AB

| Operation:          | $\{B,A\} <= A * B$                                                                                                     |          |        |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------|----------|--------|--|

| Flags:              | <ul> <li>C: Cleared.</li> <li>AC: Unaffected.</li> <li>OV: Set if B = 0 after operation; cleared otherwise.</li> </ul> |          |        |  |

| Addressing<br>Modes | Assembly Syntax                                                                                                        | Encoding | Clocks |  |

|                     | MUL AB                                                                                                                 | 10100100 | 4      |  |

Notes:

1. A and B are treated as unsigned numbers for the multiplication.

| NOP                 |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | none                                                 |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | NOP                                                  | 00000000 | 2      |

## ORL

#### Logical OR

R:

DA:

IR:

IM:

ORL A, Rn

ORL A, direct

ORL A, @Ri

ORL A, #data

| ORL A, src          |                                                      | src: R, DA, IR, IM |        |

|---------------------|------------------------------------------------------|--------------------|--------|

| Operation:          | $A \le A \mid src$                                   |                    |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                    |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding           | Clocks |

01001rrr

01000101

direct address

0100011i

01000100

immediate data

2

4

4

4

# **ORL** Logical OR with Memory

| <b>ORL</b> direct, src |                                                      | src: A, IM                 |        |

|------------------------|------------------------------------------------------|----------------------------|--------|

| Operation:             | direct <= direct   src                               |                            |        |

| Flags:                 | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes    | Assembly Syntax                                      | Encoding                   | Clocks |

| А                      | ORL direct, A                                        | 01000010<br>direct address | 4      |

| IM                     | ORL direct, #data                                    | 01000011                   | 6      |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

## **ORL** Logical OR with Carry

| src: bit, /bit                                                               |                                                                                                              |                                                                                                                                                                                                                |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $C \le C \mid$ src, where src can be either a bit or the complement of a bit |                                                                                                              |                                                                                                                                                                                                                |

| C: Set/cleared with the result of the AC: Unaffected.<br>OV: Unaffected.     | operation.                                                                                                   |                                                                                                                                                                                                                |

| Assembly Syntax                                                              | Encoding                                                                                                     | Clocks                                                                                                                                                                                                         |

| ORL C, bit                                                                   | 01110010<br>bit address                                                                                      | 4                                                                                                                                                                                                              |

| ORL C, /bit                                                                  | 10100000<br>bit address                                                                                      | 4                                                                                                                                                                                                              |

| -                                                                            | C: Set/cleared with the result of the<br>AC: Unaffected.<br>OV: Unaffected.<br>Assembly Syntax<br>ORL C, bit | C <= C   src, where src can be either a bit or the complement of a C: Set/cleared with the result of the operation. AC: Unaffected. OV: Unaffected. OV: Unaffected. ORL C, bit ORL C, bit OIII0010 bit address |

| POP direct          |                                                      |                            |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Operation:          | direct <= @SP<br>SP <= SP - 1                        |                            |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

|                     | POP direct                                           | 11010000<br>direct address | 4      |

## PUSH

**Push to Stack**

| PUSH direct         |                                                      |                            |        |

|---------------------|------------------------------------------------------|----------------------------|--------|

| Operation:          | SP <= SP + 1<br>@SP <= direct                        |                            |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |

|                     | PUSH direct                                          | 11000000<br>direct address | 4      |

| RET                 |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | PC[15:8] <= @SP<br>PC[7:0] <= @SP - 1<br>SP <= SP -2 |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | RET                                                  | 00100010 | 6      |

## RETI

#### **Return from Interrupt**

#### RETI

| Operation:          | PC[15:8] <= @SP<br>PC[7:0] <= @SP - 1<br>SP <= SP -2 |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | RETI                                                 | 00110010 | 6      |

| RL A                |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | A <= {A[6:0], A[7]}                                  |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | RL A                                                 | 00100011 | 2      |

## **RLC** Rotate Left through Carry

| RLC A               |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | $\{C, A\} \le \{A[7:0], C\}$                         |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | RLC A                                                | 00110011 | 2      |

| RR A                |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | A <= {A[0], A[7:1]}                                  |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | RR A                                                 | 00000011 | 2      |

## **RRC** Rotate Right through Carry

# RRC A Operation: {C, A} <= {A[0], C, A[7:1]}</td> Flags: C: Unaffected.<br/>AC: Unaffected.<br/>OV: Unaffected. Addressing<br/>Modes Assembly Syntax Encoding Clocks RRC A 00010011 2

# SETB

Set (Bit)

| SETB dst            |                                                                            | dst: C, bit                         |        |

|---------------------|----------------------------------------------------------------------------|-------------------------------------|--------|

| Operation:          | dst <= 1'b1                                                                |                                     |        |

| Flags:              | C: Set if dst is C; unaffected other<br>AC: Unaffected.<br>OV: Unaffected. | rwise.                              |        |

| Addressing<br>Modes | Assembly Syntax                                                            | Encoding                            | Clocks |

| C:                  |                                                                            | 11010011                            | 2      |

|                     | SETB C                                                                     | 11010011                            |        |

| Bit:                | SETB C                                                                     | 11010011<br>11010010<br>bit address | 2      |

#### Notes:

1. This is a read-modify-write instruction, so when reading a Port register the data returned by the Port register is the contents of the output register rather than the input register.

# SJMP

### **Short Jump**

| Operation:          | PC <= PC + offset                                  |                            |        |  |  |

|---------------------|----------------------------------------------------|----------------------------|--------|--|--|

| Flags:              | C: Unaffected<br>AC: Unaffected<br>OV: Unaffected. |                            |        |  |  |

| Addressing<br>Modes | Assembly Syntax                                    | Encoding                   | Clocks |  |  |

|                     | SJMP rel                                           | 10000000<br>address offset | 6      |  |  |

Notes:

1. The PC value used in the address calculation is the address of the next instruction.

2. The relative address is sign-extended to 16 bits before the addition.

# SUBB

Subtract

| SUBB A, src | src: R, DA, IR, IM                                                                                                                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:  | A <= A - src - C                                                                                                                                                                                                |

| Flags:      | <ul><li>C: Set if arithmetic borrow out of bit 7; cleared otherwise.</li><li>AC: Set if arithmetic borrow out of bit 3; cleared otherwise.</li><li>OV: Set if arithmetic overflow; cleared otherwise.</li></ul> |

| Addressing Assembly Syntax<br>Modes |                | Encoding       | Clocks |  |

|-------------------------------------|----------------|----------------|--------|--|

| R:                                  | SUBB A, Rn     | 10011rrr       | 2      |  |

| DA:                                 | SUBB A, direct | 10010101       | 4      |  |

|                                     |                | direct address |        |  |

| IR:                                 | SUBB A, @Ri    | 1001011i       | 4      |  |

| IM:                                 | SUBB A, #data  | 10010100       | 4      |  |

|                                     |                | immediate data |        |  |

# SWAP

## Swap Nibbles

| SWAP A              |                                                      |          |        |

|---------------------|------------------------------------------------------|----------|--------|

| Operation:          | A <= {A[3:0], A[7:4]}                                |          |        |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |          |        |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding | Clocks |

|                     | SWAP A                                               | 11000100 | 2      |

| XCH A, src          | CH A, src src: R, DA, IR                             |                            |        |  |

|---------------------|------------------------------------------------------|----------------------------|--------|--|

| Operation:          | tmp <= src<br>src <= A<br>A <= tmp                   |                            |        |  |

| Flags:              | C: Unaffected.<br>AC: Unaffected.<br>OV: Unaffected. |                            |        |  |

| Addressing<br>Modes | Assembly Syntax                                      | Encoding                   | Clocks |  |

| R:                  | XCH A, Rn                                            | 11001rrr                   | 2      |  |

| DA:                 | XCH A, direct                                        | 11000101<br>direct address | 4      |  |

| IR:                 | XCH A, @Ri                                           | 1100011i                   | ] 4    |  |

# XCHD

## Exchange Digit

| XCHD A, src         |                                                        | src: IR  |        |

|---------------------|--------------------------------------------------------|----------|--------|