## **Y90 Microprocessor**

#### **Technical Manual**

#### Disclaimer

Systemyde International Corporation reserves the right to make changes at any time, without notice, to improve design or performance and provide the best product possible. Systemyde International Corporation makes no warrant for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make any commitment to update the information contained herein.

Systemyde International Corporation products are not authorized for use in life support devices or systems unless a specific written agreement pertaining to such use is executed between the manufacturer and the President of Systemyde International Corporation. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents, copyrights or other rights of third parties. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Systemyde International Corporation. All trademarks are trademarks of their respective companies.

Every effort has been made to ensure the accuracy of the information contain herein. If you find errors or inconsistencies please bring them to our attention. In all cases, however, the Verilog HDL source code for the Y90 design defines "proper operation".

Copyright © 2010, 2012, 2013, 2016 Systemyde International Corporation. All rights reserved.

#### Notice:

"Z80", "Z180" and "Zilog" are registered trademarks of Zilog, Inc. All uses of these terms in this document are to be construed as adjectives, whether or not the noun "microprocessor", "CPU" or "device" are actually present.

### Table of Contents

| 1. Introduction                         | 3   |

|-----------------------------------------|-----|

| 2. Features                             | 5   |

| 3. Pin Descriptions                     | 7   |

| 4. External Timing                      | 19  |

| 5. Instruction Set                      | 47  |

| 6. Memory Management Unit (MMU)         | 149 |

| 7. Interrupt Control                    | 157 |

| 8. DMA Request Control                  | 159 |

| 9. Wait State Control                   | 161 |

| 10. Watch-Dog Timer                     | 163 |

| 11. System Status                       | 167 |

| 12. Real-Time Interrupt (RTI) Generator | 175 |

| 13. Top Level Verilog Code              | 179 |

| 14. HDL Compile Options                 |     |

### **Revison History**

| Date       | Changes                                                                               | Page(s)            |

|------------|---------------------------------------------------------------------------------------|--------------------|

| 03/04/2010 | Added ext status bus and ext status rd to MPU version.                                | Ch 3 and Ch 11     |

|            | Added MPU version timing diagrams.                                                    | Ch 4               |

|            | Added Z80/Z180 compile option for CCF instruction.                                    | Ch 5               |

|            | Changed timing for MLT to increase overall clock speed                                | Ch 5               |

|            | Changed opcode for LDMS instruction.                                                  | Ch 6               |

| 03/04/2010 | Changed timing for some new instructions.                                             | Ch 6               |

|            | Added dma_req Status compile option.                                                  | Ch 11              |

|            | Added wait_req Status compile option.                                                 | Ch 11              |

|            | Added RTI Status.                                                                     | Ch 11              |

|            | Added RTI Generator discussion, diagrams.                                             | Ch 12              |

| 03/27/2010 | Updated <b>dma_req</b> timing diagram.                                                | Ch 4               |

| 03/27/2010 | Added HDL Compile Option descriptions.                                                | Appendix 1         |

| 04/08/2010 | Signal values during dma_ack, halt_tran and sleep_tran                                | Ch 3 & Ch 4        |

| 04/12/2010 | Signal values during HALT and SLP instructions.                                       | Ch 5               |

| 06/03/2010 | Added Top Level Verilog chapter                                                       | Ch 13              |

| 10/11/2012 | Updates to System Status Block                                                        | Ch 11              |

| 10/16/2012 | Changed all MMU and System Status instructions so that they do not sample interrupts. | Ch 6 and Ch 11     |

| 10/22/2012 | Fixed Typos in interrupt table                                                        | 156                |

| 11/10/2012 | Added nmiack_tran output                                                              | Ch 3               |

| 11/14/2012 | Edits to pin descriptions.                                                            | Ch 3               |

| 12/17/2012 | Clarify Trap, RTI and System Status operation                                         | Ch 4, Ch 11, Ch 12 |

| 08/06/2013 | Added int_req_en bus, nmi_addr bus to MPU version                                     | Ch 3, Ch 4         |

| 01/16/2015 | Fixed typo in MLT instruction encoding                                                | 104                |

## Introduction

This book documents the operation of the Y90 microprocessor. The Y90 design is supplied in Verilog HDL and can be implemented in any technology supported by a logic synthesis tool that accepts Verilog HDL. Included in the design package is a test bench that exercises all instructions, flag settings, and representative data patterns. The test patterns should achieve at least 95% fault coverage.

The Y90 CPU was designed in a clean-room environment and is an upgrade of the Zilog Z80 and Z180 microprocessors. Only publicly available documentation was used to create this design so there may be minor differences where the public documentation is misleading or lacking. The instruction execution times are not identical between the two designs. The Y90 CPU operates with a consistent two-clock-cycle machine cycle, while the Z80 and Z180 microprocessors use machine cycles that vary from three to seven clock cycles.

The Y90 design, depending on the version, may not implement all of the instructions, features or operating modes of the Z80 architecture. The specific differences are covered in the various appendices.

This document should always be used as the final word on the operation of the Y90 CPU, but it is useful to refer to the Zilog documentation if the description given here is too cryptic. The Z80 architecture is over thirty years old, so it is assumed that it is already at least somewhat familiar to the reader.

The Y90 CPU is accompanied by full design documentation, in the form of a large spreadsheet, which describes nearly every facet of the internal operation of the processor. This provides knowledgeable users the opportunity to customize the design for unique application requirements.

The Y90 design is available in three versions: the Y90 CPU consists of the processor only, while the Y90 MPU surrounds the processor with a number of modules to support operation with an RTOS. This includes a memory management unit, an interrupt controller, a DMA request controller, a watch-dog timer, real-time interrupt for time slicing, and various fault monitors. The third version, called the Y90-180, contains the peripheral functions present in the original Zilog Z180. This version of the design is described in a separate document.

### Features

- \* Fully functional synthesizable Verilog HDL version of the Z80 CPU or Z180 CPU

- \* Vendor and technology independent

- \* Software compatible with several industry-standard processors

- \* 189 instructions (more with optional modules)

- \* Eight addressing modes

- \* 64K byte (up to 256M byte with optional paged MMU) memory addressing capability

- \* Separate 64K byte I/O address space

- \* 16 bit ALU with bit, byte and BCD operations

- \* Powerful vectored interrupt capability with separate interrupt vector input bus

- \* Static, fully synchronous design uses no 3-state buses

- \* Uniform 2 clock-cycle machine cycle

- \* Memory interface matches common FPGA and ASIC memory timing

- \* Separate I/O bus, compatible with AMBA Peripheral Bus

- \* Illegal instruction detection, optional write-protect and execute-protect

- \* State machines include optional illegal state detection

- \* Full design documentation included

- \* Verilog simulation and test suite included

- \* Optional modules (interrupt, bus control, system status, real-time interrupt)

Shown below are the registers visible to the programmer. The main registers have both a primary and an alternate version. The primary register set consists of A, F, B, C, D, E, H, and L, while the alternate register set consists of A', F', B', C', D', E', H', and L'. At any given time only one bank is active, and care must be used when switching between banks, as there is no way for the programmer to check which bank is active. The accumulator, A, is the destination for all 8-bit arithmetic and logic operations, while the Flag register F contains the flag results of arithmetic and logic operations. The other general-purpose registers can be paired, BC or DE or HL, to form 16-bit registers. There are two index registers, IX and IY, used for indexed addressing mode. The I register holds the upper eight bits of the interrupt vector table address for use in Interrupt Mode 2. The R register is left over from the original Z80 architecture, where it was used to hold a refresh address for DRAMs. In the Y90 it is just another general purpose register. The Stack pointer, SP, holds the address of the stack, and the Program Counter, PC, holds the address of the currently executing instruction.

| Α  | F |  |  |

|----|---|--|--|

| В  | С |  |  |

| D  | Ε |  |  |

| Н  | L |  |  |

| IX |   |  |  |

| IY |   |  |  |

Main Register Bank

| А' | F' |

|----|----|

| В' | C' |

| D' | Е' |

| Н' | L' |

I R

| SP |  |

|----|--|

| PC |  |

Alternate Register Bank

Special Function Registers

# **Pin Descriptions**

The Y90 design does not attempt to match the signals or timing present on either the Z80 microprocessor or the Z180 microprocessor. Rather, the interfaces and signals are optimized for use in either an ASIC or an FPGA.

Memory and I/O use separate address and data buses in addition to the separate control signals. The memory bus is designed to match typical ASIC and FPGA memory timing, although it can be used with stand-alone memory devices just as easily. A separate interrupt vector bus is provided for use with an interrupt controller. If desired, this interrupt vector bus can be tied to either the memory or I/O input bus for operation more closely resembling that of the original Z80 and Z180.

The interface signals for the Y90 CPU are detailed below. Note that all inputs except the two resets are sampled by the rising edge of the clock and all outputs change in response to the rising edge of the clock.

**clearb** (input, active-Low) The Master (test) Reset signal is used to initialize all of the flip-flops that are not initialized by the user reset signal. Most user-visible registers are not affected by the user reset, so this signal allows full initialization for testing and simulation. This is an asynchronous signal that should be used for Power-On Reset.

clkc (input, active-High) The CPU Clock connects to all flip-flops in the design.

- dma\_ack (output, active-High) The DMA Acknowledge signal is activated to indicate that the processor has halted to allow another bus master to use the bus. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out, mem\_data\_out, mem\_tran, nmiack\_tran, reti\_tran and t1 signals are all inactive (Low) during this time. The processor will signal dma\_ack while in the Halt or Sleep state without de-asserting the halt\_tran or sleep\_tran signals. Interrupts are not sampled while the dma\_ack signal is active, so the exit from a coincident Halt or Sleep state will be deferred until the dma\_ack signal is no longer active.

- dma\_req (input, active-High) The DMA Request signal requests that the processor halt to allow another bus master to transfer data on the bus. The processor only

releases the bus between instructions, rather than between individual bus transactions.

- **en\_prftch** (input, active-High). The Enable Prefetch signal enables the prefetch operation. Although the prefetch mode can be changed dynamically, it is recommended that this signal be tied either High or Low. The prefetch mechanism increases performance by prefetching an opcode byte during any address calculation time. Only the prefix byte (0xCB, 0xDD, 0xED or 0xFD) of a multi-byte instruction can actually be used after being prefetched.

- fault\_detect (output, active-High) The Fault Detect output is activated when an illegal state is detected in the main state machine. The main state machine uses a modified one-hot encoding, so the parity of a valid state is always even. Whenever the main state has odd parity an upset has occurred and this output will be activated.

- halt\_tran (output, active-High) The Halt Transaction signal is activated by the Halt instruction. While in the Halt state the CPU freezes and waits for an interrupt. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out, mem\_data\_out, mem\_tran, nmiack\_tran, reti\_tran and t1 signals are all inactive (Low) during this time.

- **iack\_tran** (output, active-High) The Interrupt Acknowledge Transaction signal is activated to identify an interrupt acknowledge bus transaction for an enabled Maskable Interrupt request. During an interrupt acknowledge the interrupt vector data bus is sampled, although the sampled value is only used in Interrupt Mode 0 or 2 with a maskable interrupt request.

- **inst2\_trap** (output, active-High) The Instruction Byte 2 Trap signal is activated during an interrupt acknowledge bus transaction if the interrupt acknowledge is due to the fetch of an illegal instruction during in the second byte of a two-byte opcode. This information can be used, along with the PC value written to the stack during the interrupt acknowledge sequence, to pinpoint the location of the illegal instruction.

- **inst3\_trap** (output, active-High) The Instruction Byte 3 Trap signal is activated during an interrupt acknowledge bus transaction if the interrupt acknowledge is due to the fetch of an illegal instruction during in the second byte of a three-byte opcode. This information can be used, along with the PC value written to the stack during the interrupt acknowledge sequence, to pinpoint the location of the illegal instruction.

- int\_req (input, active-High) The Interrupt Request signal is the maskable interrupt request. Maskable interrupts can be enabled and disabled under program con-

trol. This interrupt request is not latched, so it should remain active until an interrupt acknowledge transaction occurs.

- io\_addr\_out (output, 16-bit bus) The I/O Address Output bus carries the address of the I/ O port during an I/O transaction. To save power, this bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **io\_data\_in** (input, 8-bit bus) The I/O Data Input bus is sampled during the various I/O input instructions. A separate bus allows peripherals to be connected without loading the memory data bus.

- **io\_data\_out** (output, 8-bit bus) The I/O Data Output bus carries the output data for I/O output instructions. To save power, this bus holds the current value until the next I/O transaction or until the **dma\_ack** signal is activated.

- **io\_read** (output, active-High) The I/O Read signal indicates the direction of data transfer during I/O transactions. High signals read and Low signals write. This signal is valid only during I/O transactions, and is held Low at all other times.

- **io\_strobe** (output, active-High) The I/O Strobe signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for I/O transactions.

- io\_tran (output, active-High) The I/O Transaction signal is activated for all I/O transactions.

- **ivec\_data\_in** (input, 8-bit bus) The Interrupt Vector Data Input bus is sampled during interrupt acknowledge transactions. If the interrupt acknowledge was for a maskable interrupt and the CPU is in Interrupt Mode 2, this vector is used as a pointer in the interrupt vector table to find the starting address of the interrupt service routine. In Interrupt Mode 0 the vector is a one-byte RST instruction.

- **ivec\_rd** (output, active-High) The Interrupt Vector Read signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for interrupt acknowledge transactions.

- mem\_addr\_out (output, 16-bit bus) The Memory Address Output bus carries the address during memory read and write transactions. This bus is driven with all zeros while the dma\_ack signal is active.

- **mem\_data\_in** (input, 8-bit bus) The Memory Data Input bus is sampled during memory read transactions. A separate bus allows peripherals to be connected without loading the memory data bus.

- mem\_data\_out (output, 8-bit bus) The Memory Data Output bus carries the output data for memory write transactions. This bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **mem\_rd** (output, active-High) The Memory Read signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for memory read transactions.

- mem\_tran (output, active-High) The Memory Transaction signal is activated for memory read and write transactions. The mem\_tran signal is active during the Halt state but is inactive during the Sleep state and while the dma\_ack signal is active.

- **mem\_wr** (output, active-High) The Memory Write signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for memory write transactions.

- **nmiack\_tran** (output, active-High) The NMI Acknowledge Transaction signal is activated to identify an interrupt acknowledge bus transaction for a Non-Maskable Interrupt request.

- nmi\_req (input, active-High) The Non-Maskable Interrupt Request signal unconditionally interrupts the CPU. This request is internally latched, so that it can be as short as one clock cycle wide.

- **resetb** (input, active-Low) The User Reset signal is used to initialize all state flip-flops and some user registers (the I, R, PC and SP registers). This is an asynchronous signal.

- **reti\_tran** (output, active-High) The Return From Interrupt transaction signal is activated immediately after the second stack read transaction during the Return From Interrupt (RETI) instruction. This signal may be used by an external interrupt controller to re-enable interrupts, for example.

- sleep\_tran (output, active-High) The Sleep Transaction signal is activated by the Sleep

instruction. While in the Sleep state the CPU freezes and waits for an interrupt. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out,

mem\_data\_out, mem\_tran, nmiack\_tran, reti\_tran and t1 signals are all

inactive (Low) during this time.

- **t1** (output, active-High) The T1 signal is active during the first clock cycle of a bus transaction. This signal is inactive during the Halt and Sleep states.

wait\_req (input, active-High) The Wait Request signal temporarily halts the CPU, usually

to wait for memory access time to be met. The wait request is not honored

while the dma\_ack, halt\_tran or sleep\_tran signals are active.

The interface signals for the Y90 MPU are detailed below. Many signals are common to the two versions, but this version adds a significant number of system-level features.

**clearb** (input, active-Low) The Master (test) Reset signal is used to initialize all of the flip-flops that are not initialized by the user reset signal. Most user-visible registers are not affected by the user reset, so this signal allows full initialization for testing and simulation. This is an asynchronous signal that should be used for Power-On Reset.

clkc (input, active-High) The CPU Clock connects to all flip-flops in the design.

- dma\_ack\_bus (output, 8-bit bus, active-High) This bus is composed of eight individual DMA Acknowledge signals, only one of which will be active at a time. A dma\_ack\_bus signal is activated to indicate that the processor has halted to allow another bus master to use the bus. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out, mem\_data\_out, mem\_tran, nmiack\_tran, reti\_tran and t1 signals are all inactive (Low) during this time. The processor can activate a dma\_ack\_bus signal while in the Halt or Sleep state without de-asserting the halt\_tran or sleep\_tran signals. Interrupts are not sampled while a dma\_ack\_bus signal is active, so the exit from a coincident Halt or Sleep state will be deferred until no dma\_ack\_bus signal is active.

- **dma\_req\_bus** (input, 8-bit bus, active-High) This bus is composed of eight individual DMA Request signals. A DMA Request signal requests that the processor halt to allow another bus master to transfer data on the bus. The processor only releases the bus between instructions, rather than between individual bus transactions.

- drq\_act\_lim (input, 5-bit value) The DMA Request Active Limit value sets the limit for the amount of time that a DMA may control the bus. The clock cycle limit is sixteen times this value, and a zero value disables the limit check. This value can be either static or controlled by an external I/O port.

- drq\_idl\_lim (input, 5-bit value) The DMA Request Idle Limit value sets the minimum amount of time that the processor will execute between granting the bus for DMA. The clock cycle limit is sixteen times this value, and a zero value dis-

ables this function. This value can be either static or controlled by an external I/O port.

- **drq\_timeout** (output, active-High) The DMA Request Time-out signal is activated for one clock cycle whenever the clock cycle limit for DMA control of the bus is reached. External logic may use this information to accumulate performance information, or as a DMA fault indicator.

- **en\_prftch** (input, active-High). The Enable Prefetch signal enables the prefetch operation. Although the prefetch mode can be changed dynamically, it is recommended that this signal be tied either High or Low. The prefetch mechanism increases performance by prefetching an opcode byte during any address calculation time. Only the prefix byte (0xCB, 0xDD, 0xED or 0xFD) of a multi-byte instruction can actually be used after being prefetched.

- exec\_inh (input, active-High) The Execute Inhibit signal is sampled during the t1 time of fetch transactions for the first byte of an instruction. A trap is generated if this signal is sampled active at this time. This is accomplished by jamming an 0xC7 (RST 0) on the data bus into the CPU in response to the instruction fetch. Because only the fetch of the first byte of an instruction samples the exec\_inh signal, a multi-byte instruction that starts in an execute-enabled region will execute properly, but if the next in-line instruction is in an execute-protected region it will cause a trap. The execute-inhibit function works identically with or without prefetch being enabled.

- ext\_stat\_bus (input, 8-bit bus, active-High) This bus is composed of eight individual External Status signals. The state of this bus is sampled during the t1 time of the instruction that reads the System Status Block. These signals will typically be used to report on the health of other parts of the system. Since the ext\_stat\_bus is only sampled for the read of the System Status Block, any transient conditions that contribute to this status must be latched externally.

- ext\_stat\_rd (output, active-High) The External Status Read signal is activated when the System Status Block has been read. This signal can be used to clear any latches associated with signals contributing to the ext\_stat\_bus status.

- fatal\_detect (output, active-High) The Fatal Detect output is activated whenever an unrecoverable error is detected, and remains active until the next Reset. There are only two unrecoverable errors: First, when the exec\_inh signal is activated for an instruction fetch in Page 0. Second, when the wr\_inh signal is activated during a stack write. Both circumstances will lead to an infinite loop of traps. The fatal\_detect signal forces a reset of the device to prevent this infinite loop.

- fault\_detect (output, active-High) The Fault Detect output is activated when an illegal state is detected in the main state machine. The main state machine uses a modified one-hot encoding, so the parity of a valid state is always even. Whenever the main state has odd parity an upset has occurred and this output will be activated. The fault\_detect signal forces a reset of the device.

- halt\_tran (output, active-High) The Halt Transaction signal is activated by the Halt instruction. While in the Halt state the CPU freezes and waits for an interrupt. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out, mem\_data\_out, mem\_tran, nmiack\_tran, reti\_tran and t1 signals are all inactive (Low) during this time.

- iack\_tran (output, active-High) The Interrupt Acknowledge Transaction signal is activated to identify an interrupt acknowledge bus transaction. An interrupt acknowledge occurs in response to an enabled Maskable Interrupt request. During an interrupt acknowledge the interrupt controller supplies an interrupt vector for the maskable interrupt.

- iack\_wait\_lim (input, 5-bit value) The Interrupt Acknowledge Wait Limit value sets the limit for the number of Wait states during an interrupt acknowledge transaction. This value is used directly, and a zero value disables the limit check. This value can be either static or controlled by an external I/O port.

- int\_ack\_bus (output, 16-bit bus, active-High) This bus is composed of sixteen individual Interrupt Acknowledge signals. One int\_ack\_bus signal is activated during the interrupt acknowledge transaction to indicate exactly which interrupt request is being acknowledged. The active int\_ack\_bus signal can be used to clear the interrupt condition if desired.

- int\_req\_bus (input, 16-bit bus, active-High) This bus is composed of sixteen individual Interrupt Request signals. The Interrupt Request signal is the maskable interrupt request, and is enabled using the corresponding Interrupt Enable signal. Maskable interrupts are globally enabled and disabled under program control. This interrupt request is latched, so it does not need to remain active until an interrupt acknowledge transaction occurs. Each interrupt request latch is cleared automatically by the corresponding Interrupt Acknowledge signal.

- int\_req\_en (input, 16-bit bus, active-High) This bus is composed of sixteen individual Interrupt Enable signals. The Interrupt Enable signals provide a way to control the Maskable Interrupt requests via external hardware. These signals also provide a means to clear the interrupt request latches outside of the normal Interrupt Acknowledge clear, by temporarily disabling the Interrupt Request.

- io\_addr\_out (output, 16-bit bus) The I/O Address Output bus carries the address of the I/ O port during an I/O transaction. To save power, this bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **io\_data\_in** (input, 8-bit bus) The I/O Data Input bus is sampled during the various I/O input instructions. A separate bus allows peripherals to be connected without loading the memory data bus.

- **io\_data\_out** (output, 8-bit bus) The I/O Data Output bus carries the output data for I/O output instructions. To save power, this bus holds the current value until the next I/O transaction or until the **dma\_ack** signal is activated.

- **io\_read** (output, active-High) The I/O Read signal indicates the direction of data transfer during I/O transactions. High signals read and Low signals write. This signal is valid only during I/O transactions, and is held Low at all other times.

- **io\_strobe** (output, active-High) The I/O Strobe signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for I/O transactions.

- io\_tran (output, active-High) The I/O Transaction signal is activated for all I/O transactions.

- **io\_wait\_lim** (input, 5-bit value) The I/O Transaction Wait Limit value sets the limit for the number of Wait states during an I/O transaction. This value is used directly, and a zero value disables the limit check. This value can be either static or controlled by an external I/O port.

- **ivec\_offset** (input, 3-bit value) The Interrupt Vector Offset value is used to create the interrupt vector generated by the interrupt controller. In interrupt mode 2 this value is the three most-significant bits of the interrupt vector. In Interrupt Mode 0 this value selects which RST instruction to return during the interrupt acknowledge (0x0 is RST 0, 0x1 is RST 8, and so on). This value can be either static (the typical case), controlled by an external I/O port, or modified by the pending interrupt.

- mem\_addr\_out (output, 16-bit bus) The Memory Address Output bus carries the address during memory read and write transactions. This bus is driven with all zeros while the dma\_ack signal is active.

- **mem\_data\_in** (input, 8-bit bus) The Memory Data Input bus is sampled during memory read transactions. A separate bus allows peripherals to be connected without loading the memory data bus.

- mem\_data\_out (output, 8-bit bus) The Memory Data Output bus carries the output data for memory write transactions. This bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **mem\_rd** (output, active-High) The Memory Read signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for memory read transactions.

- mem\_tran (output, active-High) The Memory Transaction signal is activated for memory read and write transactions. The mem\_tran signal is active during the Halt state but is inactive during the Sleep state and while the dma\_ack signal is active.

- **mem\_wait\_lim** (input, 5-bit value) The Memory Transaction Wait Limit value sets the limit for the number of Wait states during a memory transaction. This value is used directly, and a zero value disables the limit check. This value can be either static or controlled by an external I/O port.

- **mem\_wr** (output, active-High) The Memory Write signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for memory write transactions.

- **nmiack\_tran** (output, active-High) The NMI Acknowledge Transaction signal is activated to identify an interrupt acknowledge bus transaction for a Non-Maskable Interrupt request.

- nmi\_addr (input, 16-bit bus) The Non-Maskable Interrupt Address bus provides the logical address of the NMI service routine. The original Z80/Z180 vectored an NMI request to address 0x0066, so this address should be supplied on this bus if compatibility is required.

- nmi\_req (input, active-High) The Non-Maskable Interrupt Request signal unconditionally interrupts the CPU. This request is internally latched, so that it can be as short as one clock cycle wide.

- ref\_clock (input, asynchronous) The Reference Clock signal provides an external time reference for an operating system. The Real Time Interval is automatically synchronized to this signal. If this signal is not present the rti\_default value is used to set the period for the rti\_pulse signal. If the ref\_clock signal is lost, the last automatically-generated value continues.

- **reset\_bus** (input, 2-bit bus, asynchronous edge-triggered) This bus consists of two independent Reset Request signals. Each of these signals is digitally filtered to detect a transition. A valid transition on either signal (where the level change persists for at least eleven clock cycles) causes a User Reset.

- resetb (output, active-Low) The User Reset signal is generated in the System Status block

from the various possible reset sources (reset\_bus, fatal\_detect, fault\_detect

and wdt\_timeout). This signal is synchronous with the falling edge of clkc

and is guaranteed to be at least three clock cycles wide.

- rti\_default (input, 24-bit value) The Real Time Interval Default value sets the period for the rti\_pulse signal in the case there is no ref\_clock or when the automatic rti\_pulse generation is disabled. This value will be used until two valid ref\_clock transitions have been recognized, at which time the automaticallygenerated period will be used.

- rti\_divisor (input, 7-bit value) The Real Time Interval Divisor value sets the number of rti\_pulse signals during one period of the ref\_clock signal. This value is used directly, and a zero value disables the automatic generation of the rti\_pulse signal.

- rti\_pulse (output, active-High) The Real Time Interval Pulse signal is active for one clock cycle at the Real Time Interval rate.

- rti\_synced (output, active-High) The Real Time Interval Synced signal is active while the automatic rti\_pulse generation is active.

- sleep\_tran (output, active-High) The Sleep Transaction signal is activated by the Sleep

instruction. While in the Sleep state the CPU freezes and waits for an interrupt. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out,

mem\_data\_out, mem\_tran, nmiack\_tran, reti\_tran and t1 signals are all

inactive (Low) during this time.

- **t1** (output, active-High) The T1 signal is active during the first clock cycle of a bus transaction. This signal is inactive during the Halt and Sleep states. It is also inactive while **dma\_ack** is active.

- wait\_iack (input, active-High) The Interrupt Acknowledge Wait Request signal temporarily halts the processor during interrupt acknowledge transactions. This signal is sampled only during interrupt acknowledge transactions.

- wait\_io (input, active-High) The I/O Wait Request signal temporarily halts the processor during I/O transactions. This signal is sampled only during I/O transactions.

- wait\_mem (input, active-High) The Memory Wait Request signal temporarily halts the processor during memory transactions. This signal is sampled only during memory transactions.

- **wait\_timeout** (output, active-High) The Wait Request Time-out signal is activated whenever the clock cycle limit for Wait states is met. External logic may use this information to accumulate performance information, or as a fault indicator.

- wdt\_lim (input, 8-bit value) The Watch-Dog Timer Limit value sets the time-out period, in multiples of 2^20 clock cycles, for the Watch-Dog Timer. This value can be either static or controlled by an external I/O port. A value of "n" selects "n+1" multiples of 2^20 clock cycles for the time-out period. This value is sampled by the WDRES instruction.

- wr\_inh (input, active-High) The Write Inhibit signal is sampled during the t1 time of all memory write transactions, and if active the mem\_wr signal is suppressed during the transaction. A trap is also generated. This is accomplished by jamming an 0xC7 (RST 0) on the data bus into the CPU in response to the next instruction fetch.

# **External Timing**

The Y90 CPU uses a uniform two-clock-cycle machine cycle. This consistent timing simplifies the design of logic external to the CPU makes it easier to track the state of the CPU.

The memory interface timing and signals are designed to make it easy to interface to standard ASIC and FPGA memories. It uses separate read and write strobes.

The I/O interface is very close to the AMBA Peripheral Bus (APB) to allow connection to APB peripherals with a minimum of logic. It uses a single strobe with a separate direction control. The only difference relative to the APB is the setup time for the write data. In the APB the write data is setup one clock before the strobe; in this interface the write data changes coincident with the leading edge of the strobe. In most cases this will not be a problem.

The separate interrupt vector bus provides an easy way to connect to the optional interrupt controller. The interrupt vector bus is used for Mode 0 and Mode 2 maskable interrupts, so if these modes are not used the vector input bus can be tied to ground and the vector strobe output ignored.

In the diagrams below only the relevant signals are shown for each transaction. All other signals are either inactive or hold the previous value. Note that only one of the transaction identifiers (mem\_tran, io\_tran, iack\_tran, nmiack\_tran, reti\_tran, halt\_tran and sleep\_tran) can be active at a time. If all are inactive, an idle bus transaction (usually for address calculation) is in progress. If prefetch is enabled most address calculation idle transactions are replaced by memory transactions. The dma\_ack signal also indicates that the bus is idle, in response to the dma\_req signal. The dma\_ack signal can be active while either halt\_tran or sleep\_tran is active.

The **wait\_req** input is only sampled for memory, I/O and interrupt acknowledge transactions and is ignored in all other cases. Wait states will disrupt the two-clock-cycle machine cycle rule. If this feature is important but wait states must be used, two wait states per transaction is recommended. If memory access time is an issue it might be better to stretch the first clock cycle of a transaction rather than add Wait states. The uniform two-clock machine cycle makes it relatively straightforward to do this.

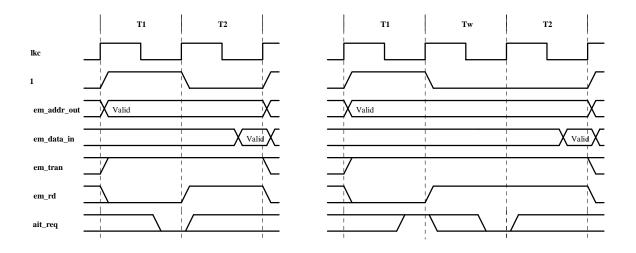

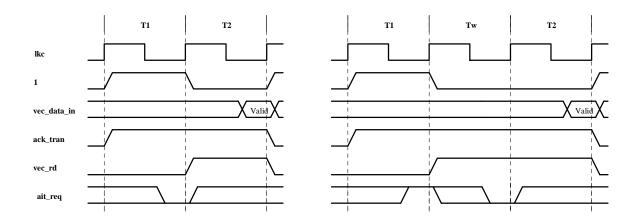

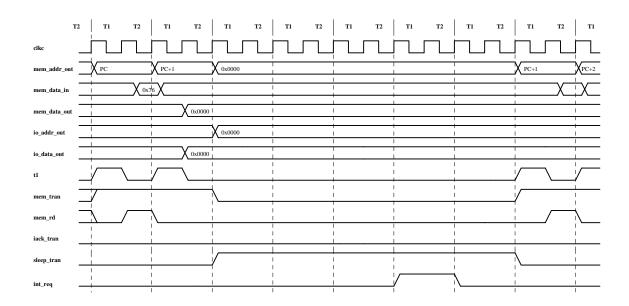

#### **Memory Read**

The figure below shows the memory read transaction, without Wait states and with one Wait state. Memory read transactions are used for both instruction and data fetch. There is no separate instruction/data status indicator, although this status exists internally if it is needed.

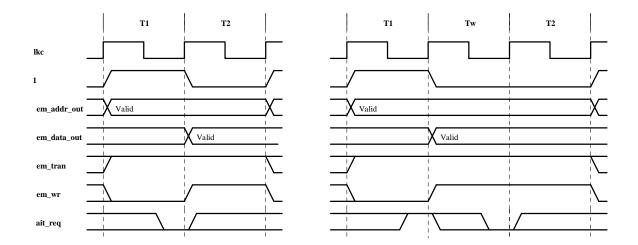

#### **Memory Write**

The figure below shows the memory write transaction, without Wait states and with one Wait state.

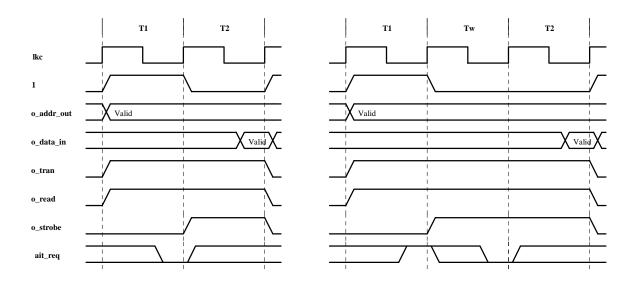

#### I/O Read

The figure below shows an I/O read transaction, without Wait states and with one Wait state.

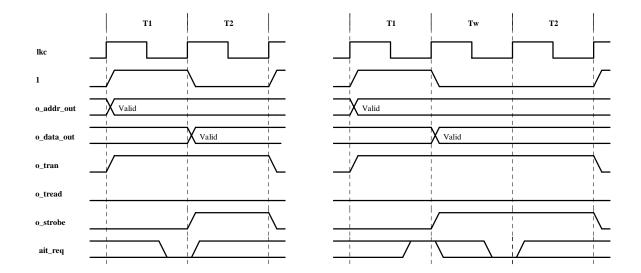

#### I/O Write

The figure below shows an I/O write transaction, without Wait states and with one Wait state.

#### **Interrupt Acknowledge**

The figure below shows the interrupt acknowledge transaction, without Wait states and with one Wait state.

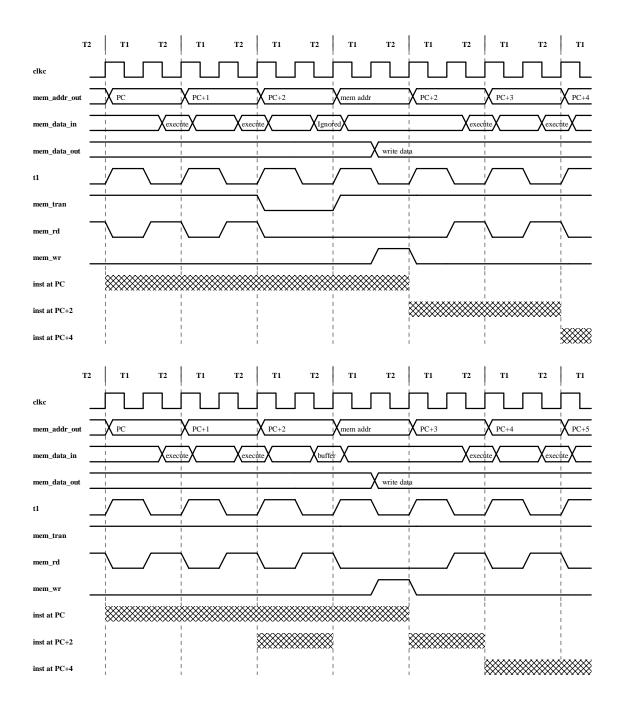

#### Prefetch

The figure below shows a typical instruction (a memory write) without the prefetch enabled and with the prefetch enabled. The prefetch logic uses address calculation machine cycles to look at the next opcode byte. If this opcode byte is one of the "prefix" bytes (0xCB, 0xDD, 0xED or 0xFD) the logic buffers this byte and will not re-fetch it when the current instruction completes. Only these four prefix bytes will be buffered, even though there are other multi-byte opcodes. Attempting to prefetch for every multi-byyte opcode would be significantly more complicated, with marginal performance improvement.

In practice, enabling the prefetch can improve execution time by about 5%, although this obviously depends on the exact code being executed. If Wait states are being used prefetch may not provide any performance gain, because of the Wait states added when prefetching bytes that may later be discarded.

Note that even though an instruction may execute faster when the prefetch is enabled, this instruction will still complete at the same time. However, the next instruction (the one with the first byte prefetched) will complete earlier. This is shown in the diagrams below.

The prefetch can be enabled and disabled on the fly, because the **en\_prftch** signal is sampled during the **t1** time of the fetch of the first byte of an instruction.

If **exec\_inh** is sampled active during the prefetch the byte is ignored. This causes the byte to be fetched normally at the end of the current instruction and the normal execute inhibit operation (substitution of RST 0) to commence.

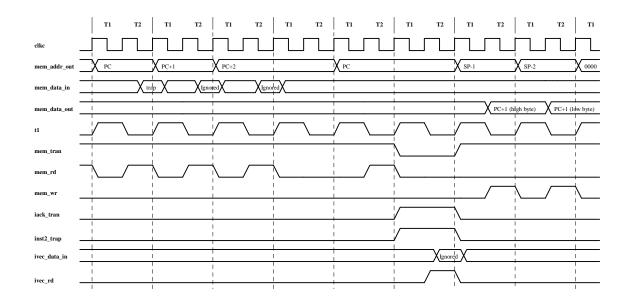

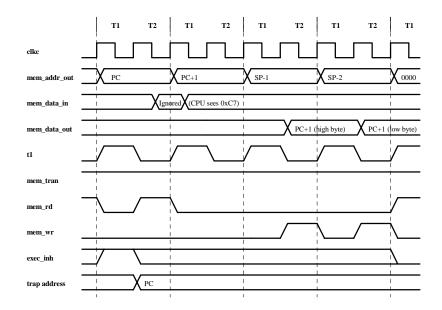

#### **Illegal Instruction (2nd byte) Trap**

The timing of an undefined second byte opcode trap is shown below. The fetch of the undefined opcode is followed by three machine cycles that flush the pipeline and rewind the Program Counter, an interrupt acknowledge with the **inst2\_trap** signal active, and two writes to push the PC of the undefined opcode to the stack. The processor then jumps to location 0x0000 and starts fetching instructions.

In the case of the Y90 CPU the **inst2\_trap** information should be latched outside the CPU to distinguish this case from both the **inst3\_trap** case and the normal reset case. The start of the illegal instruction in this case is the stacked PC value minus one.

The Y90 MPU latches the **inst2\_trap** information as well as both the logical and physical address of the offending byte. This information is available in the System Status Block.

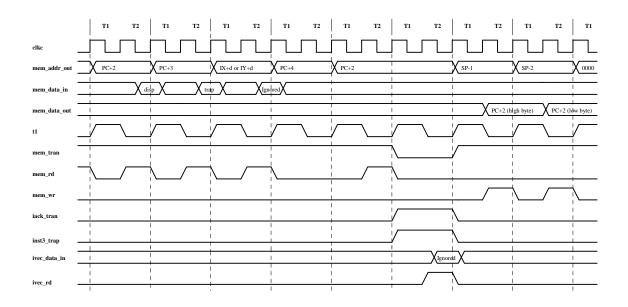

#### **Illegal Instruction (3rd byte) Trap**

The timing of an undefined third byte opcode trap is shown below. The fetch of the undefined opcode is followed by the normal Read cycle (all three-byte instructions use indexed addressing), two machine cycles that flush the pipeline and rewind the Program Counter, an interrupt acknowledge with the **inst3\_trap** signal active, and two writes to push the PC of the undefined opcode to the stack. The processor then jumps to location 0x0000 and starts fetching instructions.

In the case of the Y90 CPU the **inst3\_trap** information should be latched outside the CPU to distinguish this case from both the **inst2\_trap** case and the normal reset case. The start of the illegal instruction in this case is the stacked PC value minus two.

The Y90 MPU latches the **inst3\_trap** information as well as both the logical and physical address of the offending byte. This information is available in the System Status Block.

#### **Execute Inhibit Trap**

The timing of an Execute Inhibit trap is shown below. The fetch of the first byte of an opcode in an execute-protected page causes the CPU to execute an RST 0 instruction in place of the offending instruction. This means there is no interrupt acknowledge transaction associated with the Execute Inhibit trap. Software should use the address latched in the System Status Block to determine the source of the trap, because the stack contents point to the byte after the one that caused the trap.

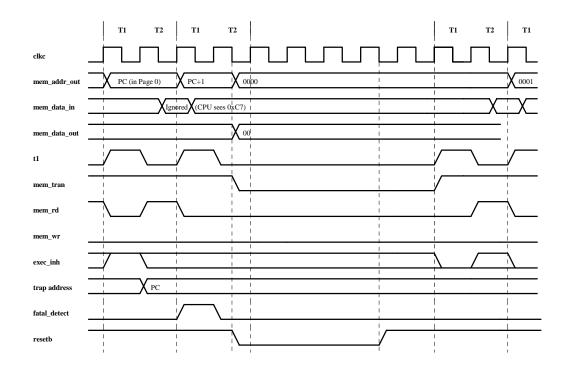

#### **Execute Inhibit Trap & Fatal Error**

The **exec\_inh** signal should never be active for an address is Page 0. This will lead to a fatal error condition because the response to the trap is to jump to address 0x0000, leading to an infinite loop of traps. The Y90-MPU activates the **fatal\_detect** signal in the case of an Execute Inhibit trap in Page 0, updates the System Status Block and generates the **resetb** signal. The timing of the **fatal\_detect** signal is shown in the diagram below.

It is assumed here that the reset will clear whatever condition lead to signalling **exec\_inh** during a Page 0 access. If this is not the case an infinite loop of traps can still result.

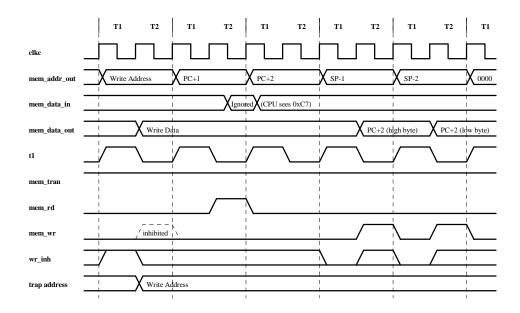

#### Write Protect Trap

The timing of a Write Protect trap is shown below. The attempt to write to a write-protected page causes the CPU to execute an RST 0 instruction in place of the next instruction. This means there is no interrupt acknowledge transaction associated with the Write Protect trap. Software should use the address latched in the System Status Block to determine the source of the trap, because the stack contents point to an address in the instruction after the one that caused the trap.

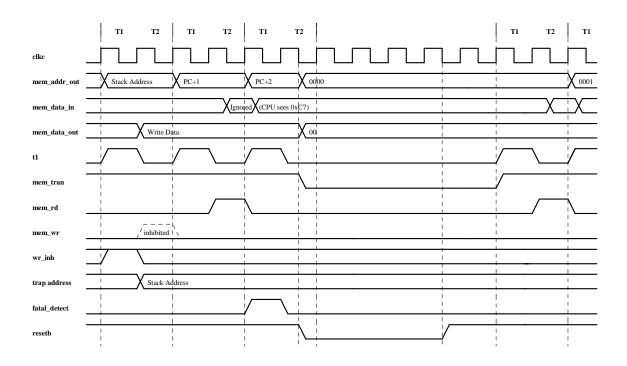

#### Write Protect Trap & Fatal Error

The **wr\_inh** signal should never be active for a stack write. This will lead to a fatal error condition because the response to the trap is to push an address to the stack and jump to address 0x0000, leading to an infinite loop of traps. The Y90-MPU activates the **fatal\_detect** signal in the case of a Write Protect trap during a stack write, updates the System Status Block and generates the **resetb** signal. The timing of the **fatal\_detect** signal is shown in the diagram below.

It is assumed here that the reset will clear whatever condition lead to signalling **wr\_inh** during a stack write. If this is not the case an infinite loop of traps can still result.

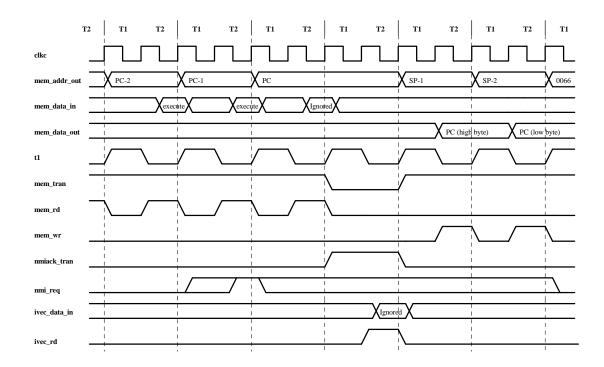

#### **Non-maskable Interrupt**

The timing of a non-maskable interrupt acknowledge transaction is shown below. The **nmi\_req** input cannot be masked by software. This input must be sampled active by a rising edge of **clkc** to be recognized by the processor, but does not need to remain active until the interrupt acknowledge transaction. In fact, to prevent an endless loop of acknowledges, the **nmi\_req** input must be de-asserted before the start of the fetch of the first instruction of the service routine. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, and two writes to push the contents of the program counter onto the stack. Execution then begins at the address provided on the **nmi\_addr** bus (shown as 0x0066 in the figure) with an instruction to properly restore the state of the interrupt enable flag prior to the non-maskable interrupt.

#### **Interrupt Mode 0**

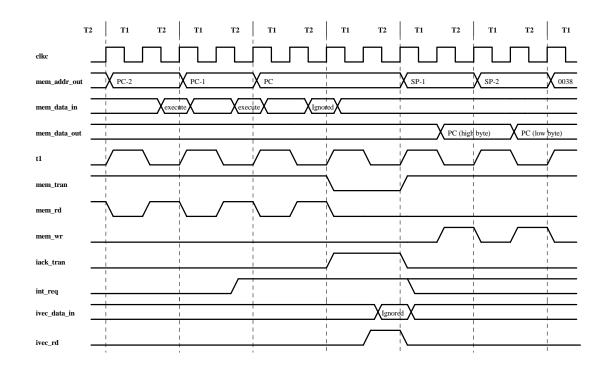

The timing of a Mode 0 maskable interrupt acknowledge is shown below. The **int\_req** signal needs to remain active until the interrupt acknowledge transaction. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, and two writes to push the contents of the program counter onto the stack. Execution then begins at the restart address specified by the RST instruction fetched during the interrupt acknowledge with an instruction fetch.

The use of an RST instruction is enforced by the hardware, which only uses bits 5-3 of the **ivec\_data\_in** bus to create one of the eight possible RST instructions.

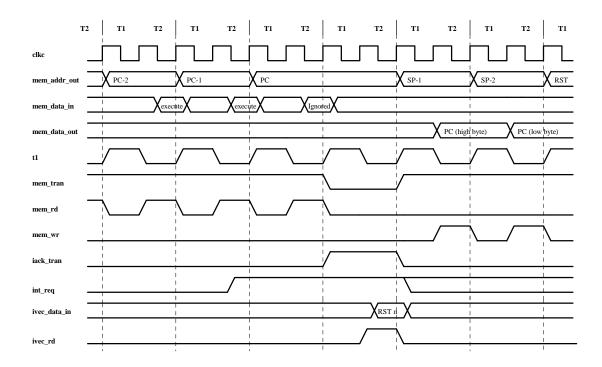

## **Interrupt Mode 1**

The timing of a Mode 1 interrupt acknowledge cycle is shown below. The **int\_req** input needs to remain active until the interrupt acknowledge transaction. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, and two writes to push the contents of the program counter onto the stack. Execution then begins at address 0x0038 with an instruction fetch.

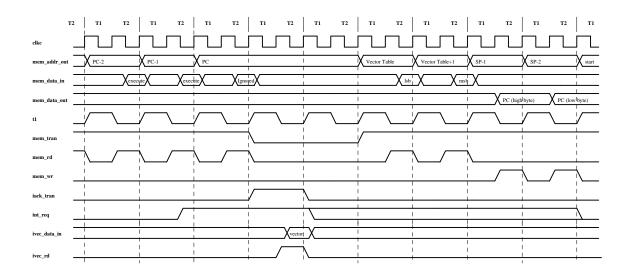

### **Interrupt Mode 2**

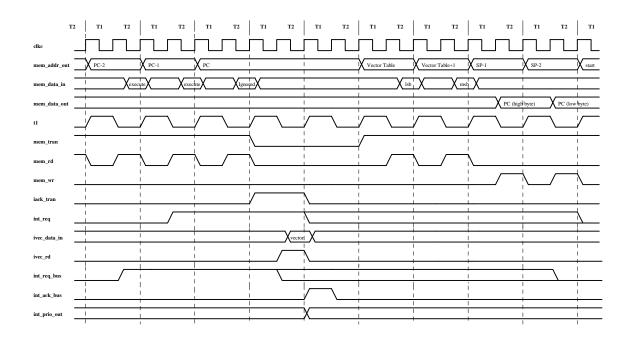

The timing of a Mode 2 maskable interrupt acknowledge is shown below. The **int\_req** input needs to remain active until the interrupt acknowledge transaction. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, an address calculation cycle, two reads of the interrupt vector table and two writes to push the contents of the program counter onto the stack. The processor automatically jumps to the address fetched from the interrupt vector table for the service routine. The upper eight bits of the interrupt vector table starting address are held in the I register in the processor. Note that the vector must be an even number. That is, the least significant bit of the vector must be a zero.

The interrupt controller in the Y90 MPU necessarily samples the **int\_req\_bus** inputs, and then goes into the edge-detect latch, which changes the timing slightly. The diagram below illustrates this change for Interrupt Mode 2. Also shown is the timing of the **int\_ack\_bus** and the **int\_prio\_out** signals.

Although Interrupt Mode 2 is the preferred mode for use with the interrupt controller, the design allows the use of any interrupt mode. In Interrupt Mode 0 or 1 it will be necessary to use the **int\_ack\_bus** signals to externally latch the information about which interrupt is being acknowledged. This is because Interrupt Modes 0 and 1 will branch to a common interrupt service routine, rather than the individual routines possible in Interrupt Mode 2.

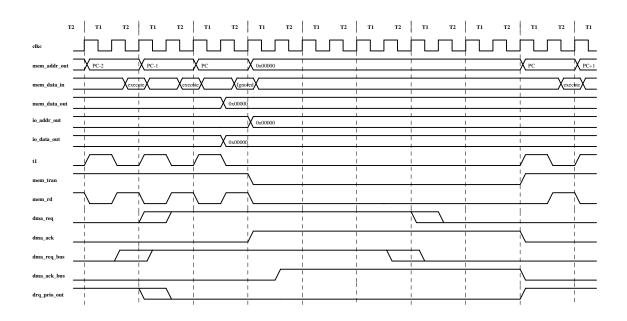

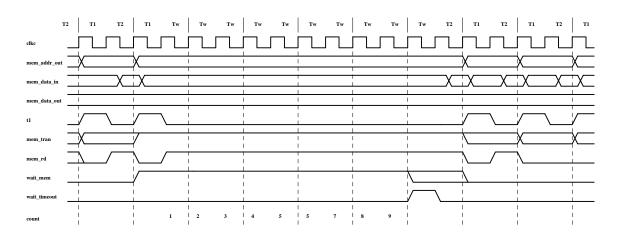

# **DMA Request/Acknowledge**

The timing of a DMA request and acknowledge is shown below. Note that like an interrupt, the **dma\_req** signal is only sampled at the end of instructions. This guarantees that all instructions are atomic.

The delay from the **dma\_req** signal to the **dma\_ack** signal is always at least one bus cycle, irrespective of whether the processor is running, in the Halt state or in the Sleep state. This implies that it is more efficient to transfer multiple bytes each time that the **dma\_req** signal is activated.

The **dma\_req** signal can be asserted during the Halt or Sleep states. In this case the active **dma\_req** signal will take precedence over **int\_req** or **nmi\_req** and inhibit either of these signals from causing an exit from the Halt or Sleep state. Once the **dma\_req** signal is deasserted any pending or future interrupt request will cause the exit from the Halt or Sleep state.

| T2            | T1 T2 | T1 T2     | T1 T2       | T1 T2     | T1 T2       | T1 T2       | T1 T2       | T1 T2      | T1 T2     | TI         |

|---------------|-------|-----------|-------------|-----------|-------------|-------------|-------------|------------|-----------|------------|

| clkc -        |       |           |             |           |             | ļ           |             |            |           | Ţ,         |

| mem_addr_out  | PC-2  | PC-1      | <b>Х</b> рс | X 0x00000 | <br> <br>   | <br> <br>   | <br>        | <br> <br>  | РС        | PC+1       |

| mem_data_in   | Xexe  |           | ute XIgno   | edX       | I<br>I<br>I | I<br>I<br>I | I<br>I<br>I | I<br> <br> | Xexe      |            |

| mem_data_out  |       | <br>      | 0x00000     |           | I<br> <br>  | 1           | I<br>I<br>I | <br>       | <br>      |            |

| io_addr_out   |       | 1<br>     |             | 0x00000   | <br> <br>   | <br> <br>   | <br> <br>   | <br> <br>  | <br>      | +          |

| io_data_out   |       | 1         | 0x00000     |           | +<br> <br>  | <br> <br>   | <br> <br>   | <br> <br>  | <br> <br> | +          |

| ťi -          | _/    |           | /           | 1         | 1<br>1      | <br>        | 1<br>1      | <br>       |           | /          |

| -<br>mem_tran |       | <br> <br> | <br>        | \         | <br>        |             | I           | <br>       |           | 1          |

| mem_rd        |       |           |             | \         | <br> <br>   | I<br>I      | 1<br> <br>  | 1<br> <br> |           | <u>ن</u> _ |

| dma_req       |       |           | <br> <br>   | <br> <br> | <br> <br>   | <br> <br>   |             | <br>       | 1         |            |

| dma_ack       |       | <br> <br> |             | /         | <br> <br>   |             |             |            | \         |            |

|               | 1     | 1         | 1           |           |             |             |             |            |           | 1          |

The DMA request controller in the Y90 MPU necessarily samples the **dma\_req\_bus** inputs, which changes the timing slightly. The diagram below illustrates this change. Also shown is the timing of the **dma\_ack\_bus** and the **dma\_prio\_out** signals. In particular, note that the leading edge of the **dma\_ack\_bus** signals are delayed by one clock cycle from the normal **dma\_ack** timing. The timing of the trailing edge of these signals is not affected.

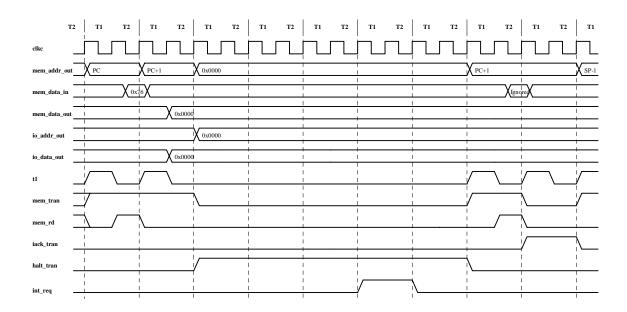

# Halt state

The Halt state is entered when the HALT instruction is executed, as shown below. In the Halt state the processor freezes, for an unlimited number of two clock cycle machine cycles, with the **halt\_tran** output active. The only way to exit the Halt state is with either an interrupt (either **nmi\_req** or **int\_req**) or via reset. Note that **int\_req** can only be used to exit the Halt mode if interrupts are enabled when the HALT instruction is executed. The timing for exiting the Halt state with an interrupt is also shown below.

If the Halt state is exited by an interrupt, the processor will resume instruction execution (after the interrupt service routine) at the address of the instruction following the HALT instruction. The minimum width of the **halt\_tran** signal is two clock cycles.

The Halt state in this design is slightly different from that in the Z80 or Z180 microprocessors. In those designs the processor continues to fetch the Halt instruction during the Halt state, leading to continued power dissipation. Since this operation requires the special step of "rewinding" the PC, no attempt was made to match this operation. Rather, the Halt state and the Sleep state are essentially identical, reducing the power consumption to a minimum by minimizing the number of signals that are transitioning during these states.

The Halt state differs from the Sleep state only for the case where interrupts are disabled. In the Halt state, if interrupts are disabled only the **nmi\_req** or a reset (from any of the various sources) will cause an exit from this state. In the Sleep state if interrupts are disabled a rising edge on the **int\_req** will force an exit from the Sleep state, with execution continuing with the instruction following the SLP instruction.

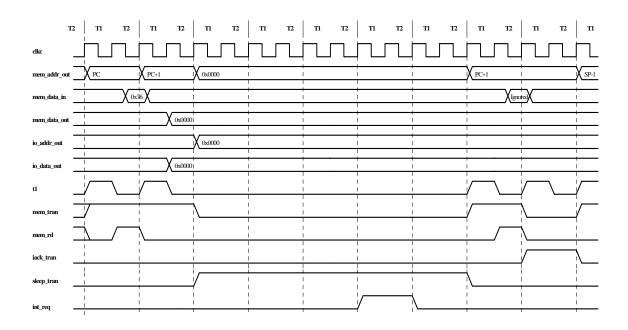

### **Sleep state**

The Sleep state is entered when the SLP instruction is executed, as shown below. In the Sleep state the processor freezes, for an unlimited number of two clock cycle machine cycles, with the **sleep\_tran** output active. The only way to exit the Sleep state is with either an interrupt (either **nmi\_req** or **int\_req**) or via reset. The **int\_req** signal can be used to exit the Sleep mode irrespective of whether or not interrupts are enabled when the SLP instruction is executed.

The timing for exiting the Sleep state with an enabled interrupt or non-maskable interrupt is shown below. In this case the processor will resume instruction execution (after the interrupt service routine) at the address of the instruction following the SLP instruction.

In the case where the Sleep state exit is caused by a maskable interrupt while interrupts are disabled the processor merely resumes execution at the address of the instruction following the SLP instruction, without going through an interrupt service routine. Note that the minimum width of the **sleep\_tran** signal is two clock cycles.

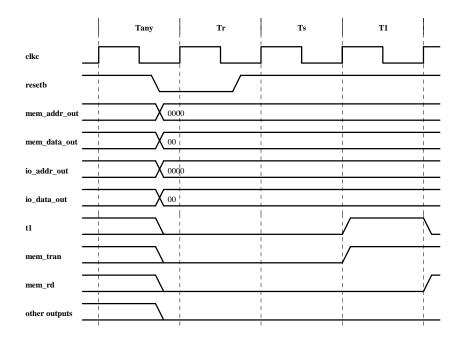

### Reset

The Reset state is entered immediately when the **resetb** signal goes Low, independent of the current state, and this state continues until the first rising edge of **clkc** after the **resetb** signal is de-asserted. At this rising edge there is a one clock cycle transient state to set up the internal pipeline controls, and on the next clock the processor begins fetching the first instruction from address 0x0000.

Software starting at location 0x0000 must be able to distinguish between reset, execution of an RST 0 instruction, a trap, or watch-dog time-out. All of these cases cause the Program Counter to be reset to 0x0000. In the case of the Y90 MPU this information is available in the System Status Block.

The minimum width of the **resetb** signal is set by the flip-flops used in the design. The setup time for the **resetb** signal to the rising edge of the **clkc** signal is likewise determined by the flip-flops used in the design.

The **clearb** signal has the same timing requirements as the **resetb** signal. The **clearb** signal should only be used in the power-on case, and only affects those flip-flops not affected by the **resetb** signal.

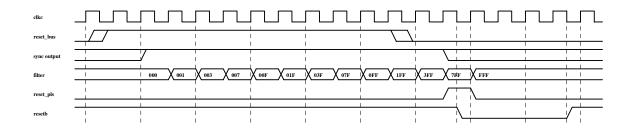

In the case of the Y90 MPU the **resetb** signal is an output, generated from the **reset\_bus** input signals or internal error conditions. The **reset\_bus** input signals are synchronized and filtered to generate the **resetb** signal synchronous with the falling edge of the **clkc** signal.

A transition, of either polarity, on either **reset\_bus** signal, will generate the **resetb** signal. But this change-of-state on a **reset\_bus** signal must persist for at least ten clock cycles for the **resetb** signal to be generated. Any pulse shorter than ten clock cycles will not pass the digital filter. The timing for the generation of the **resetb** signal is shown in the diagram below.

# **Base Instruction Set**

This chapter presents the assembly language syntax, addressing modes, flag settings, binary encoding, and execution time for the base Y90 instruction set. The entire instruction set is presented in alphabetical order.

The assembly language syntax is identical to that used by the original Zilog assembler. Different assembler programs may or may not use identical syntax. The syntax is presented generically at the beginning of each instruction, with the details presented for each addressing mode later in each entry.

The operation of each instruction is specified in a format similar to Verilog HDL for minimum ambiguity, but no descriptive text or examples are included.

The effect of the instruction on each flag is listed, with a brief description. Normally the flags are updated by the main operation of the instruction, but for some complex instructions different flags may be affected by different parts of the instruction. This is specified in the description. The flags are organized as below in the F (Flag) register:

| S | Z | U5 | Н | U3 | P/V | Ν | С |

|---|---|----|---|----|-----|---|---|

|---|---|----|---|----|-----|---|---|

These flags have the following meanings:

| Flag | Meaning                                                                                    |

|------|--------------------------------------------------------------------------------------------|

| S    | Sign (a copy of the MSB of the result).                                                    |

| Z    | Zero (indicating that the result was zero).                                                |

| U5   | Unused Bit 5 (an unused Flag register bit).                                                |

| Н    | Half-Carry (carry out of the lower nibble, used for BCD math).                             |

| U3   | Unused Bit 3 (an unused Flag register bit).                                                |

| P/V  | Parity/Overflow (parity of the result, or arithmetic overflow; depends on the instruction) |

| Ν    | Negative (add/subtract flag, necessary for BCD math)                                       |

| С    | Carry (arithmetic carry, or shift linkage bit)                                             |

Fields in the instruction are listed using shortcuts for common fields. These shortcuts should be self-explanatory in most cases, but will be detailed here for completeness.

The most common field in the instruction specifies a CPU register, employing the following encoding:

| rrr | <b>Register Selected</b> |

|-----|--------------------------|

| 000 | В                        |

| 001 | С                        |

| 010 | D                        |

| 011 | Е                        |

| 100 | Н                        |

| 101 | L                        |

| 111 | A (Accumulator)          |

Word registers are similarly encoded, although the exact encoding depends on the instruction:

| dd, ss, tt, xx or yy | dd, ss Register | tt Register | xx Register | yy Register |

|----------------------|-----------------|-------------|-------------|-------------|

| 00                   | BC              | BC          | BC          | BC          |

| 01                   | DE              | DE          | DE          | DE          |

| 10                   | HL              | HL          | IX          | IY          |

| 11                   | SP              | AF          | SP          | SP          |

The execution time for instructions is always a multiple of two clocks. Any number in parentheses is the execution time when the prefetch is enabled, via the **en\_prftch** signal into the core. When enabled, the prefetch operation uses any address calculation time to look at the first byte of the next instruction. If this instruction byte can be pre-decoded the byte will be buffered for use when the current instruction finishes. This results in the execution time in parentheses. Only instructions that require more than one machine cycle to execute can be pre-decoded.

| ADC A, src | src: R, IM, IR, X                                                                                                                                                                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | A <= A + src + CF                                                                                                                                                                                                                                                                                                                                      |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set if arithmetic carry out of bit 3; cleared otherwise.</li> <li>P/V: Set if arithmetic overflow; cleared otherwise.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit 7; cleared otherwise.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax                | Encoding | Clocks |

|---------------------|--------------------------------|----------|--------|

| R:                  | ADC A, r                       | 10001rrr | 2      |

| IM:                 | ADC A, n                       | 11001110 | 4      |

|                     |                                | n        |        |

| IR:                 | ADC A, (HL)                    | 10001110 | 6 (4)  |

| X:                  | ADC A, (IX+d) or ADC A, (IY+d) | 11y11101 | 10 (8) |

|                     |                                | 10001110 |        |

|                     |                                | d        |        |

1. The **rrr** field uses the standard register select encoding

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

| ADC HL, src         | src: RR                                                                                                                                                                                                                                                                         |                                                         |        |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------|--|--|

| Operation:          | HL <= HL + src + CF                                                                                                                                                                                                                                                             |                                                         |        |  |  |

| Flags:              | <ul> <li>S: Set if result is negative; cleared</li> <li>Z: Set if result is zero; cleared othe</li> <li>H: Set if arithmetic carry out of bit</li> <li>P/V: Set if arithmetic overflow; cleared.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit</li> </ul> | erwise.<br>t 11; cleared otherwise.<br>eared otherwise. |        |  |  |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                                                                                                                                                 | Encoding                                                | Clocks |  |  |

| RR:                 | ADC HL, ss                                                                                                                                                                                                                                                                      | 11101101<br>01ss1010                                    | 4      |  |  |

|                     |                                                                                                                                                                                                                                                                                 |                                                         |        |  |  |

1. The **ss** field uses the standard word register encoding.

# ADD

Add

| ADD A, src | src: R, IM, IR, X                                                                                                                                                                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | A <= A + src                                                                                                                                                                                                                                                                                                                                           |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set if arithmetic carry out of bit 3; cleared otherwise.</li> <li>P/V: Set if arithmetic overflow; cleared otherwise.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit 7; cleared otherwise.</li> </ul> |

| A, r                       |                                         |         |

|----------------------------|-----------------------------------------|---------|

|                            | 10000rrr                                | 2       |

| A, n                       | 11000110                                | 4       |

| L                          | n                                       |         |

| A, (HL)                    | 10000110                                | 6 (4)   |

| A, (IX+d) or ADD A, (IY+d) | 11y11101                                | 10 (8)  |

|                            |                                         | _       |

|                            | A, n A, (HL) A, (IX+d) or ADD A, (IY+d) | A, (HL) |

Notes:

1. The  ${\bf rrr}$  field uses the standard register select encoding.

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

| ADC dst, src        |                                                                                                                                                                                                     | dst: HL, IX, IY<br>src: RR |        |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|

| Operation:          | dst <= dst + src                                                                                                                                                                                    |                            |        |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Set if arithmetic carry out of R</li> <li>P/V: Unaffected.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of R</li> </ul> |                            |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                                                                     | Encoding                   | Clocks |

| RR:                 | ADD HL, ss                                                                                                                                                                                          | 00ss1001                   | 2      |

|                     | ADC IX, xx                                                                                                                                                                                          | 11011101<br>01xx1001       | 4      |

|                     | ADC IY, yy                                                                                                                                                                                          | 11111101<br>01yy1001       | 4      |

1. The ss, xx and yy fields use the standard word register select encodings.

| AND A, src | src: R, IM, IR, X                                                                                                                                                                                                                                 |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operation: | A <= A & src                                                                                                                                                                                                                                      |  |  |  |

| Flags:     | <ul> <li>Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set.</li> <li>P/V: Set if parity of result even; cleared otherwise.</li> <li>N: Cleared.</li> <li>C: Cleared.</li> </ul> |  |  |  |

| Addressing<br>Modes | Assembly Syntax                | Encoding | Clocks |

|---------------------|--------------------------------|----------|--------|

| R:                  | AND A, r                       | 10100rrr | 2      |

| IM:                 | AND A, n                       | 11100110 | 4      |

|                     |                                | n        |        |

| IR:                 | AND A, (HL)                    | 10100110 | 6 (4)  |

| X:                  | AND A, (IX+d) or AND A, (IY+d) | 11y11101 | 10 (8) |

|                     |                                | 10100110 |        |

|                     |                                | d        |        |

1. The **rrr** field uses the standard register select encoding.

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

# BIT

Bit Test

| BIT b, src | src: R, IR, X                                                      |

|------------|--------------------------------------------------------------------|

| Operation: | $Z \leq -src[b]$                                                   |

| Flags:     | S: Unaffected.<br>Z: Set if tested bit is zero; cleared otherwise. |

|            | H: Set.                                                            |

|            | P/V: Unaffected.                                                   |

|            | N: Cleared.                                                        |

|            | C: Unaffected.                                                     |

|            |                                                                    |

|            |                                                                    |

| Addressing<br>Modes | Assembly Syntax                | Encoding  | Clocks |

|---------------------|--------------------------------|-----------|--------|

| R:                  | BIT b, r                       | 11001011  | 4      |

|                     |                                | 01bbbrrr  |        |

| IR:                 | BIT b, (HL)                    | 10100110  | 8 (6)  |

|                     |                                | 01bbb1110 |        |

| X:                  | BIT b, (IX+d) or BIT b, (IY+d) | 11y11101  | 10     |

|                     |                                | 11001011  |        |

|                     |                                | d         |        |

|                     |                                | 01bbb110  |        |

Notes:

1. The **rrr** field uses the standard register select encoding.

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY.

- 3. The **bbb** field uses normal binary encoding.

- 4. For the original Z80, the  ${\bf S}$  and  ${\bf C}$  flags are undefined.

### CALL Call Subroutine

| CALL dst            |                                                                                                                                                              | dst: DA            |        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|

| Operation:          | SP <= SP - 2<br>(SP) <= PC<br>PC <= dst                                                                                                                      |                    |        |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |                    |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding           | Clocks |

| DA:                 | CALL mn                                                                                                                                                      | 11001101<br>n<br>m | 10     |

### CALL Conditional Call Subroutine

| CALL cc, dst        |                                                                                                                                                              | dst: DA |               |                           |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|---------------------------|

| Operation:          | if (cc = true) begin<br>SP <= SP - 2<br>(SP) <= PC<br>PC <= dst<br>end                                                                                       |         |               |                           |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |         |               |                           |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              |         | Encoding      | Clocks                    |

| DA:                 | CALL cc, mn                                                                                                                                                  |         | 11fff100<br>n | 10/6<br>(taken/not taken) |

| <b>Notes:</b><br>1. | Mnemonic Encoding (fff)                                                                                                                                      | Meaning | Flag case     |                           |

| 1. | Mnemonic | Encoding (fff) | Meaning     | Flag case        |

|----|----------|----------------|-------------|------------------|

|    | NZ       | 000            | Non-zero    | $\mathbf{Z} = 0$ |

|    | Ζ        | 001            | Zero        | Z = 1            |

|    | NC       | 010            | Non-carry   | $\mathbf{C} = 0$ |

|    | С        | 011            | Carry       | C = 1            |

|    | PO       | 100            | Parity Odd  | P/V = 0          |