## **Async/HDLC Port**

### **Technical Manual**

Systemyde International Corporation

#### Disclaimer

Systemyde International Corporation reserves the right to make changes at any time, without notice, to improve design or performance and provide the best product possible. Systemyde International Corporation makes no warrant for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make any commitment to update the information contained herein.

Systemyde International Corporation products are not authorized for use in life support devices or systems unless a specific written agreement pertaining to such use is executed between the manufacturer and the President of Systemyde International Corporation. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents, copyrights or other rights of third parties. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Systemyde International Corporation. All trademarks are trademarks of their respective companies.

Every effort has been made to ensure the accuracy of the information contain herein. If you find errors or inconsistencies please bring them to our attention. In all cases, however, the Verilog HDL source code for the hdlc\_top design defines "proper operation".

Copyright © 2010, Systemyde International Corporation. All rights reserved.

## Index

| Features                  |    |

|---------------------------|----|

| Bus Interface             | 5  |

| Async/HDLC Receiver       |    |

| Interface                 | 21 |

| Async/HDLC Transmitter    |    |

| Interface                 |    |

| Digital Phase-locked Loop |    |

| Interface                 |    |

| IRDA Encode/Decode        |    |

| Interface                 |    |

| Encoder/Decoder           | 41 |

| Interface                 | 43 |

| Top Level Verilog         |    |

|                           |    |

## **Revision History**

Date Description

Page(s)

### Features

### hdlc\_top

#### General:

- 4 byte FIFOs for both receive and transmit

- Provision for 8-, 16- or 32-bit bus interface

- Provision for expanded FIFO depth

- Bus interface module (Rabbit 4000 compatible) easily replaced with custom interface

- Bus interface module includes interrupt and DMA requests

- Bus interface module includes 15-bit Baud Rate Generator

- FIFO overrun and underrun reporting

#### Async mode

- 7 or 8 bits/character

- Optional Even, Odd, Mark or Space parity generation and checking

- Optional 9th bit for Address/Data multiprocessor operation

- 16x or 8x oversampling

- Flase start bit rejection

- Optional IRDA encode and decode

#### HDLC mode

- Automatic Flag generation and checking

- Automatic Abort generation and checking

- Automatic zero-insertion and deletion

- Automatic CRC generation and checking

- 16- or 32-bit CRC polynomial

- Flag Search command for receiver to stop frame reception

- Send Abort command for transmitter to interrupt frame transmission

- Abort-on-underrun option for transmitter

- Optional DPLL for clock recovery

- Optional IRDA encode and decode

- Optional data encode/decode: NRZ, NRZI, Biphase-Level, Biphase-Mark/Space

- Received frame status (with byte count) eliminates real-time checking of frame status

- Frame status strobe to implement external frame status FIFO

### Bus Interface rab\_if

The following register set is included in the **rab\_if** module, which is the default Rabbit 4000-compatible bus interface. This bus interface can be used as-is, modified to suit your own requirements, or completely replaced. In any case, all of the serial features will still be available.

This bus interface is uses a byte-wide data bus and a 4-bit address bus, with separate read and write strobes. Timing on the bus interface is similar to that used in the industry-standard APB bus.

This interface provides input multiplexers for the serial data and clocks, combined interrupt requests and separate receive and transmit DMA requests. Also included in a baud rate generator.

#### Registers

| Register Name                     | Mnemonic | I/O address | R/W | Reset    |

|-----------------------------------|----------|-------------|-----|----------|

| Serial Port Data Register         | SDR      | 0x8         | R/W | XXXXXXXX |

| Serial Port Address Register      | SAR      | 0x9         | W   | XXXXXXXX |

| Serial Port Long Stop Register    | SLR      | 0xA         | W   | XXXXXXXX |

| Serial Port Status Register       | SSR      | 0xB         | R   | 0xx00000 |

| Serial Port Control Register      | SCR      | 0xC         | R/W | 00000000 |

| Serial Port Extended Register     | SER      | 0xD         | R/W | 00000000 |

| Serial Port Divider Low Register  | SDLR     | 0xE         | R/W | XXXXXXXX |

| Serial Port Divider High Register | SDHR     | 0xF         | R/W | 0xxxxxxx |

#### **Register Descriptions**

|                                                                    | Serial Port | Data Register                               | (SDR)       | (Address = 0x8) |

|--------------------------------------------------------------------|-------------|---------------------------------------------|-------------|-----------------|

| Bit(s)                                                             | Value       |                                             | Description |                 |

| 7:0                                                                | Read        | Returns the contents of the receive buffer. |             |                 |

| Write Loads the transmit buffer with a data byte for transmission. |             | nsmission.                                  |             |                 |

| 5      | Serial Port A | ddress Register (SAR) (Address = 0x9)                                                                                                                                                                                               |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit(s) | Value         | Description                                                                                                                                                                                                                         |

| 7:0    | Read          | Returns the contents of the receive buffer.                                                                                                                                                                                         |

|        | Write         | Loads the transmit buffer with an address byte, marked with a "zero" address bit, for transmission. In HDLC mode, the last byte of a frame must be written to this register to enable subsequent CRC and closing Flag transmission. |

| S      | erial Port L | ong Stop Register                           | (SLR)                 | (Address = 0xA)                  |

|--------|--------------|---------------------------------------------|-----------------------|----------------------------------|

| Bit(s) | Value        |                                             | Description           |                                  |

| 7:0    | Read         | Returns the contents of th                  | e receive buffer.     |                                  |

|        | Write        | Loads the transmit buffer for transmission. | with an address byte, | marked with a "one" address bit, |

| Serial Port Status Register(SSR)(Address = 0xB) |       |                                                                                                                                                                                                                                                         |                              | (Address = 0xB)                                                       |

|-------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------|

| Bit(s)                                          | Value | Description (Async mode only)                                                                                                                                                                                                                           |                              |                                                                       |

| 7                                               | 0     | The receive data regis                                                                                                                                                                                                                                  | ter is empty                 |                                                                       |

|                                                 | 1     | •                                                                                                                                                                                                                                                       |                              | Port will request an interrupt n the receive buffer is empty.         |

| 6                                               | 0     | The byte in the receiv                                                                                                                                                                                                                                  | e buffer is data, received w | vith a valid Stop bit.                                                |

|                                                 | 1     | -                                                                                                                                                                                                                                                       |                              | byte with a framing error. If an uffer is all zeros, this is a Break. |

| 5                                               | 0     | The receive buffer wa                                                                                                                                                                                                                                   | s not overrun.               |                                                                       |

|                                                 | 1     | The receive buffer wa                                                                                                                                                                                                                                   | s overrun. This bit is clear | ed by reading the receive buffer.                                     |

| 4                                               | 0     | The byte in the receiv                                                                                                                                                                                                                                  | e buffer has no parity error | r (or was not checked for parity).                                    |

|                                                 | 1     | The byte in the receiv                                                                                                                                                                                                                                  | e buffer had a parity error. |                                                                       |

| 3                                               | 0     | The transmit buffer is                                                                                                                                                                                                                                  | empty.                       |                                                                       |

|                                                 | 1     | The transmit buffer is not empty. The Serial Port will request an interrupt whe<br>the transmitter takes a byte from the transmit buffer. Transmit interrupts are<br>cleared when the transmit buffer is written, or any value is written to this regis |                              | ffer. Transmit interrupts are                                         |

| 2                                               | 0     | The transmitter is idle                                                                                                                                                                                                                                 | ·.                           |                                                                       |

|                                                 | 1     | clears this bit, which o                                                                                                                                                                                                                                |                              | s generated when the transmitter<br>ter is ready to start sending     |

| 1:0                                             | 00    | These bits are read/wr                                                                                                                                                                                                                                  | rite but are always ignored  | in async mode.                                                        |

|        | Serial Port | Status Register(SSR)(Address = 0xB)                                                                                                                                                                                                                                                                                                         |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit(s) | Value       | Description (HDLC mode only)                                                                                                                                                                                                                                                                                                                |

| 7      | 0           | The receive data register is empty                                                                                                                                                                                                                                                                                                          |

|        | 1           | There is a byte in the receive buffer. The Serial Port will request an interrupt while this bit is set. The interrupt is cleared when the receive buffer is empty.                                                                                                                                                                          |

| 6,4    | 00          | The byte in the receive buffer is data.                                                                                                                                                                                                                                                                                                     |

|        | 01          | The byte in the receive buffer was followed by an Abort.                                                                                                                                                                                                                                                                                    |

|        | 10          | The byte in the receive buffer is the last in the frame, with valid CRC.                                                                                                                                                                                                                                                                    |

|        | 11          | The byte in the receive buffer is the last in the frame, with a CRC error.                                                                                                                                                                                                                                                                  |

| 5      | 0           | The receive buffer was not overrun.                                                                                                                                                                                                                                                                                                         |

|        | 1           | The receive buffer was overrun. This bit is cleared by reading the receive buffer.                                                                                                                                                                                                                                                          |

| 3      | 0           | The transmit buffer is empty.                                                                                                                                                                                                                                                                                                               |

|        | 1           | The transmit buffer is not empty. The Serial Port will request an interrupt when<br>the transmitter takes a byte from the transmit buffer, unless the byte is marked as<br>the last in the frame. Transmit interrupts are cleared when the transmit buffer is<br>written, or any value (which will be ignored) is written to this register. |

| 2:1    | 00          | Transmit interrupt due to buffer empty condition.                                                                                                                                                                                                                                                                                           |

|        | 01          | Transmitter finished sending CRC. An interrupt is generated at the end of CRC transmission. Data written in response to this interrupt will cause only one Flag to be transmitted between frames, and no interrupt will be generated by this Flag.                                                                                          |

|        | 10          | Transmitter finished sending an Abort. An interrupt is generated at the end of an Abort transmission.                                                                                                                                                                                                                                       |

|        | 11          | The transmitter finished sending a closing Flag. Data written in response to this interrupt will cause at least two Flags to be transmitted between frames.                                                                                                                                                                                 |

| 0      | 0           | The byte in the receiver buffer is 8 bits.                                                                                                                                                                                                                                                                                                  |

|        | 1           | The byte in the receiver buffer is less than 8 bits.                                                                                                                                                                                                                                                                                        |

| S      | Serial Port | Control Register(SCR)(Address = 0xC)                                                                                                                                                                      |  |

|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit(s) | Value       | Description                                                                                                                                                                                               |  |

| 7:6    | 00          | No operation. These bits are ignored in the Async mode.                                                                                                                                                   |  |

|        | 01          | In HDLC mode, force receiver in Flag Search mode.                                                                                                                                                         |  |

|        | 10          | No operation.                                                                                                                                                                                             |  |

|        | 11          | In HDLC mode, transmit an Abort pattern.                                                                                                                                                                  |  |

| 5:4    | 00          | Input bus bit 2 is used for data (and optional clock) input.                                                                                                                                              |  |

|        | 01          | Input bus bit 1 is used for data (and optional clock) input.                                                                                                                                              |  |

|        | 10          | Input bus bit 0 is used for data (and optional clock) input.                                                                                                                                              |  |

|        | 11          | Disable the receiver data input. Clocks from clock input bus bit 0.                                                                                                                                       |  |

| 3:2    | 00          | Async mode with 8 bits per character.                                                                                                                                                                     |  |

|        | 01          | Async mode with 7 bits per character. In this mode the most significant bit of a byte is ignored for transmit, and is always zero in receive data.                                                        |  |

|        | 10          | HDLC mode with external clock. The external clocks are supplied via external inputs.                                                                                                                      |  |

|        | 11          | HDLC mode with internal clock. The clock is 16X the data rate, and the DPLL is used to recover the receive clock. If necessary, the receiver and transmitter clocks can be output via parallel port pins. |  |

| 1:0    | 00          | The Serial Port interrupt is disabled.                                                                                                                                                                    |  |

|        | 01          | The Serial Port uses Interrupt Priority 1.                                                                                                                                                                |  |

|        | 10          | The Serial Port uses Interrupt Priority 2.                                                                                                                                                                |  |

|        | 11          | The Serial Port uses Interrupt Priority 3.                                                                                                                                                                |  |

| S      | Serial Port Extended Register(SER)(Address = 0xD) |                                                                                                                                                           |  |  |

|--------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit(s) | Value                                             | Description (Async mode only)                                                                                                                             |  |  |

| 7:5    | 000                                               | Disable parity generation and checking.                                                                                                                   |  |  |

|        | 001                                               | This bit combination is reserved and should not be used.                                                                                                  |  |  |

|        | 010                                               | This bit combination is reserved and should not be used.                                                                                                  |  |  |

|        | 011                                               | This bit combination is reserved and should not be used.                                                                                                  |  |  |

|        | 100                                               | Enable parity generation and checking with even parity.                                                                                                   |  |  |

|        | 101                                               | Enable parity generation and checking with odd parity.                                                                                                    |  |  |

|        | 110                                               | Enable parity generation and checking with Space (always zero) parity.                                                                                    |  |  |

|        | 111                                               | Enable parity generation and checking with Mark (always one) parity.                                                                                      |  |  |

| 4      | 0                                                 | Normal async data encoding.                                                                                                                               |  |  |

|        | 1                                                 | Enable RZI coding (3/16ths bit cell IRDA-compliant).                                                                                                      |  |  |

| 3      | 0                                                 | Normal Break operation. This option should be selected when address bits are expected.                                                                    |  |  |

|        | 1                                                 | Fast Break termination. At the end of Break a dummy character is written to the buffer, and the receiver can start character assembly after one bit time. |  |  |

| 2      | 0                                                 | Async clock is 16X data rate.                                                                                                                             |  |  |

|        | 1                                                 | Async clock is 8X data rate.                                                                                                                              |  |  |

| 1      | 0                                                 | Continue character assembly during Break to allow timing the Break condition.                                                                             |  |  |

|        | 1                                                 | Inhibit character assembly during Break. One character (all zeros, with framing error) at start and one character (garbage) at completion.                |  |  |

| 0      |                                                   | This bit is ignored in async mode.                                                                                                                        |  |  |

| S                                                            | erial Port <b>E</b> | Extended Register (SER) (Address = 0xD)                                                                                  |  |

|--------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Bit(s)                                                       | Value               | Description (HDLC mode only)                                                                                             |  |

| 7:5 000 NRZ data encoding for HDLC receiver and transmitter. |                     | NRZ data encoding for HDLC receiver and transmitter.                                                                     |  |

|                                                              | 010                 | NRZI data encoding for HDLC receiver and transmitter.                                                                    |  |

|                                                              | 100                 | Biphase-Level (Manchester) data encoding for HDLC receiver and transmitter.                                              |  |

|                                                              | 110                 | Biphase-Space data encoding for HDLC receiver and transmitter.                                                           |  |

|                                                              | 111                 | Biphase-Mark data encoding for HDLC receiver and transmitter.                                                            |  |

| 4                                                            | 0                   | Normal HDLC data encoding.                                                                                               |  |

|                                                              | 1                   | Enable RZI coding (1/4th bit cell IRDA-compliant). This mode can only be used with internal clock and NRZ data encoding. |  |

| 3                                                            | 0                   | Idle line condition is Flags.                                                                                            |  |

|                                                              | 1                   | Idle line condition is all ones.                                                                                         |  |

| 2                                                            | 0                   | Transmit Flag on underrun.                                                                                               |  |

|                                                              | 1                   | Transmit Abort on underrun.                                                                                              |  |

| 1                                                            | 0                   | Separate HDLC external recieve and transmit clocks.                                                                      |  |

|                                                              | 1                   | Combined HDLC external and transmit clock, from transmit clock pin.                                                      |  |

| 0                                                            |                     | This bit is ignored in HDLC mode.                                                                                        |  |

| Ser    | Serial Port Divider Low Register |   | (SDLR)      | (Address = 0xE)                                             |

|--------|----------------------------------|---|-------------|-------------------------------------------------------------|

| Bit(s) | Value                            |   | Description |                                                             |

| 7:0    |                                  | e | U           | al clock for this channel. This ponding SDHR is set to one. |

| Ser    | ial Port Div | der High Register (SDHR) (Address = 0xF)                                                                                                                         |

|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit(s) | Value        | Description                                                                                                                                                      |

| 7      | 0            | Disable the serial port divider, and use the external timer input to clock the seria port.                                                                       |

|        | 1            | Enable the serial port divider, and use its output to clock the serial port. The serial port divider counts modulo $n+1$ and is clocked by the peripheral clock. |

| 6:0    |              | Seven MSBs of the divider that generates the serial clock for this channel.                                                                                      |

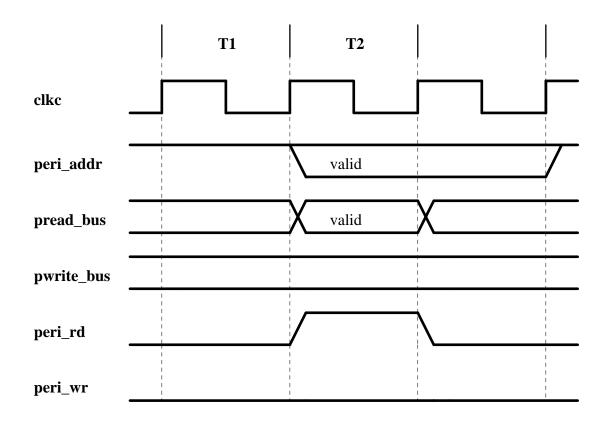

#### **Read Transaction**

Read transactions two clock cycles in length. The timing shown below is for the standard version that uses gated clocks for the control register write. If flip-flops are to be used for the control registers the peri\_addr signals need one clock setup time instead of the one clock hold time shown.

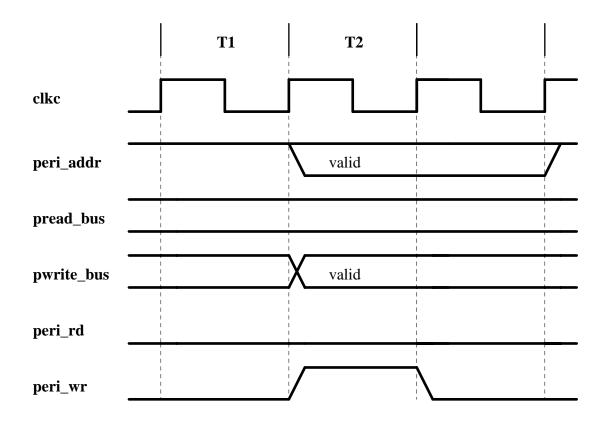

#### Write Transaction

Write transactions two clock cycles in length. The timing shown below is for the standard version that uses gated clocks for the control register write. If flip-flops are to be used for the control registers the peri\_addr and pwrite\_bus signal need one clock setup time instead of the one clock hold time shown.

#### **Top level interface**

The Verilog code below shows the top-level interface when using the default bus interface.

```

module hdlc_top (dreq_rxx, dreq_txx, dreq2_txx, serx_iclk, serx_int, serx_rbus, serx_txd,

sreq_rxx, clkp, peri_addr, pwrite_bus, resetb, rt_sync, serx_rclki,

serx_rd, serx_rxdi, serx_tclki, serx_test, serx_wr);

input

clkp;

/* main peripheral clock

*/

resetb;

/* internal reset

*/

input

rt_sync; /* receiver/transmitter clock enable

serx_rd; /* serial port peripheral read strobe

serx_test; /* serial port x test mode

*/

input

*/

input

*/

input

serx_wr;

*/

/* serial port peripheral write strobe

input

*/

input [2:0] serx_rclki; /* serial port external receive clock (hdlc mode only)

/* receiver data input

input [2:0] serx_rxdi;

*/

input [2:0] serx_tclki;

/* serial port external transmit clock (hdlc mode only)

*/

input

[3:0] peri_addr;

/* internal peripheral address bus

*/

[7:0] pwrite_bus; /* internal peripheral write bus

dreq_rxx; /* dma request for receiver

*/

input

*/

dreq_rxx;  /* dma request for receiver

dreq_txx;  /* dma request for transmitter

output

*/

*/

*/

output

output

/* transmitter data output

output

serx_txd;

*/

output

sreq_rxx;

/* special dma request

output [1:0] serx_iclk; /* serial port clock outputs (hdlc mode only)

*/

output [3:1] serx_int; /* serial port interrupt request

output [7:0] serx_rbus; /* serial port peripheral read bus

*/

```

## **Async/HDLC Receiver**

### hdlc\_rx

The **hdlc\_rx** module is the async/hdlc receiver. This receiver contains four bytes of buffering, which allows for connection to an 8-, 16- or 32-bit bus or external FIFO. Buffer-full signals for each byte in the buffer, along with byte, word and long read strobes simplify the interface to an external bus or FIFO. Status is buffered along with each byte, and a separate HDLC frame status output bus allows frame status to be buffered separately from the data.

In Async mode the clock can be either sixteen (the default) or eight times the data rate. In HDLC mode the clock is sixteen times the data rate. Thus the maximum data rate is the peripheral clock frequency divided by eight in Async mode and divided by sixteen in HDLC mode. With the external clock option in HDLC mode the maximum rate for the bit rate is **clkp**/5 because of the synchronization logic in the clock and data paths.

In Async mode the port can send and receive seven or eight bits and has the option of recognizing an additional address bit. A status bit distinguishes normal data from "address" data. This status bit is set to one if a "zero" address bit is received. In non-address bit applications, this indicates a framing error. This status bit can also indicate a received break, if the accompanying data is all zeros (this is the definition of break).

HDLC mode encapsulates data within opening and closing Flags, and sixteen or thirty-two bits of CRC precedes the closing Flag. All information between the opening and closing Flag is "zero-stuffed". That is, if five consecutive ones occur, independent of byte boundaries, a zero is automatically inserted by the transmitter and automatically deleted by the receiver. This allows a Flag byte (07Eh) to be unique within the serial bit stream.

Both the CCITT polynomial  $(x^{16}+x^{12}+x^5+1)$  and Ethernet polynomial  $(x^{32}+x^{26}+x^{23}+x^{22}+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x^1+1)$  are available, with the generator and checker preset to all ones.

Receive operation is essentially automatic. Each byte is marked with status to indicate end-of-frame, short frame and CRC error, and a separate frame status is available with the overall status for the frame. This makes it possible to transfer all of the data in a received fram without checking the status byte-by-byte. This frame status, which includes a byte count, remains valid until the end of the next received frame.

The receiver automatically synchronizes on Flag bytes and presets the CRC checker appropriately. If the current receive frame is not needed (because of an address mismatch, for example) a Flag Search command is available. This command forces the receiver to ignore the incoming data stream until another Flag is received.

Not separate receive interrupt signal is generated by the receiver. Rather, external logic can use **bufr-full** status and **bufr\_add** (EOF) status to create a receive interrupt.

The receiver can receive frames of any bit length. If the last "byte" in the frame is not eight bits, the receiver sets a status flag that is buffered along with this last byte. Software can then use the table below to determine the number of valid data bits in this last "byte". Note that the receiver transfers all bits between the opening and closing Flags, except for the inserted zeros, to the receive data buffer.

| Last byte bit pattern | Valid data bits |  |  |

|-----------------------|-----------------|--|--|

| bbbbbbb0              | 7               |  |  |

| bbbbbb01              | 6               |  |  |

| bbbbb011              | 5               |  |  |

| bbbb0111              | 4               |  |  |

| bbb01111              | 3               |  |  |

| bb011111              | 2               |  |  |

| b0111111              | 1               |  |  |

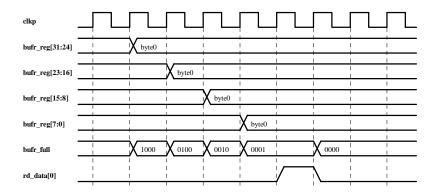

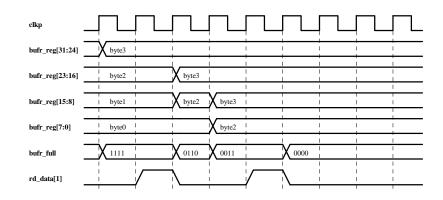

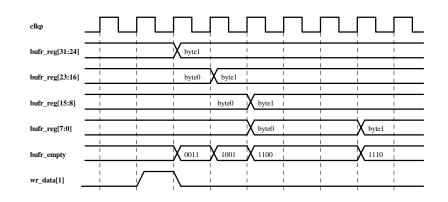

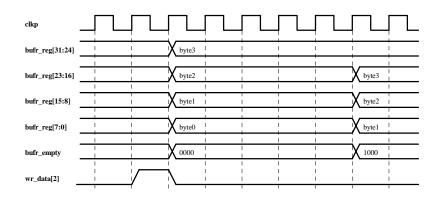

As mentioned previously, data flows through the buffer. The diagram below shows a byte being written to the buffer by the receiver and then rippling through before being read. Note that the **rd\_data** signal can be one clock cycle earlier. It is shown delayed for clarity.

The diagram below shows a byte being written to the buffer, filling the buffer. The buffer is then emptied using four byte reads. Byte reads can have as little as one clock cycle between successive reads.

The diagram below shows a byte being written to the buffer, filling the buffer. The buffer is then emptied using two word reads. Word reads can have as little as one clock cycle between successive reads.

The diagram below shows a byte being written to the buffer, filling the buffer. The buffer is then emptied using a long read.

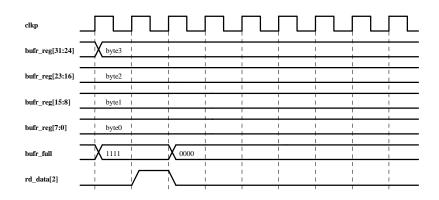

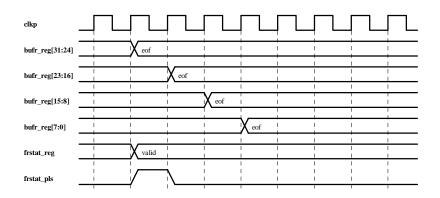

The diagram below shows the timing for the write of the last byte in an HDLC frame and the frame status update.

#### Interface

The interface signals for the **hdlc\_rx** module are detailed below. All inputs except for the reset are sampled by the rising edge of the clock and all outputs change in response to the rising edge of the clock.

- **asyn\_fast** (input, active-High) The Async Fast control signal selects the clock divide ratio for Async mode and is ignored in HDLC mode. Low selects divide-by-16, while High selects divide-by-8.

- **bits7** (input, active-High) The 7 Bits/Character control signal selects the number of data bits per character for Async mode and is ignored in HDLC mode. Low selects 8 data bits/character, while High selects 7 data bits/character.

- brk\_fast (input, active-High) The Fast Break control signal selects the timing at the end of a received Break condition in Async mode and is ignored in HDLC mode. Low enables the receiver to internally force the Break to terminate on a byte boundary, while High enables the receiver to terminate the Break on any bit boundary. Selecting the byte boundary termination can lead to a lost character in the case when a Break does not end on a byte boundary and is immediately followed by data, so the brk\_fast signal should usually be High.

- **brk\_spec** (input, active-High) The Special Break control signal selects the receiver operation during a received Break condition in Async mode and is ignored in HDLC mode. Low enables the receiver to assemble bytes and transfer them to the buffer during the Break condition, while High disables character assembly during the Break. Enabling character assembly during Break allows the duration of the Break condition to be calculated by counting the number of characters transferred.

- **bufr\_add** (output, 4-bit bus) The Address Tag bits accompany data in the data buffer, tagging each byte with the state of any corresponding Address bit (the first bit following the last data bit or the parity bit) in Async mode and marking the last byte in a frame (when High) in HDLC mode.

- **bufr\_bit** (output, 4-bit bus) The Unaligned Data Tag bits accompany data in the data buffer, indicating if the last byte in a frame does not contain eight bits. This bit is only valid for the data marked as the last in an HDLC frame. Low signals that the last data contains eight valid bits, while High signals that less than eight bits are valid. The table below shows which bits are valid in the buffer.

| Last byte bit pattern | Valid data bits |  |  |

|-----------------------|-----------------|--|--|

| bbbbbbb0              | 7               |  |  |

| bbbbbb01              | 6               |  |  |

| bbbbb011              | 5               |  |  |

| bbbb0111              | 4               |  |  |

| bbb01111              | 3               |  |  |

| bb011111              | 2               |  |  |

| b0111111              | 1               |  |  |

- **bufr\_crc** (output, 4-bit bus) The CRC Tag bits accompany data in the data buffer, tagging each byte with the result of the parity check (if any) in Async mode and the result of the CRC calculation in HDLC mode. Low signals no error and High signals error. For HDLC this bit should only be used for the byte tagged as the last in the frame.

- bufr\_full (output, 4-bit bus) The Full Tag bits accompany data in the data buffer, tagging each byte as full or empty. Low signals empty and High signals full. Note that data ripples through the buffer. Refer to the timing diagrams below for details. These bits should be used to create interrupt requests DMA requests, and write signals for an external FIFO.

- **bufr\_ovr** (output, 4-bit bus) The Overrun Tag bits accompany data in the data buffer, tagging each byte with the buffer overrun status. This status will be set when the receiver writes to the buffer when the buffer is full, resulting in the loss of data.

- bufr\_reg (output, 32-bit bus) This is the receive data buffer. Bytes ripple through the FIFO from most-significant byte to least-significant byte. A Byte read removes the bufr\_reg[7:0] from the buffer, while moving any other bytes in the buffer one byte to the right. A Word read removes the bufr\_reg[15:0] from the buffer while moving the remaining bytes one byte to the right. These bytes will move one more byte to the right on the next clock cycle. A Long read removes all four bytes from the buffer.

clkp (input, active-High) The Peripheral Clock connects to all flip-flops in the module.

crc32\_en (input, active-High) The CRC32 Enable control signal selects the CRC polynomial to use in HDLC mode and is ignored in Async mode. Low selects the CCITT polynomial (x<sup>16</sup>+x<sup>12</sup>+x<sup>5</sup>+1), while High selects the Ethernet polynomial (x<sup>32</sup>+x<sup>26</sup>+x<sup>23</sup>+x<sup>22</sup>+x<sup>16</sup>+x<sup>12</sup>+x<sup>11</sup>+x<sup>10</sup>+x<sup>8</sup>+x<sup>7</sup>+x<sup>5</sup>+x<sup>4</sup>+x<sup>2</sup>+x<sup>1</sup>+1).

- **frstat\_pls** (output, active-High) The Frame Status Pulse signal goes High for one clock cycle at the end of a received frame to indicate that the frame status bus is valid. This pulse can be used to write the frame status to a status FIFO is necessary.

- **frstat\_reg** (output, 18-bit bus) The Frame Status bus holds the status information for the most-recently received frame, and is valid until the end of the next frame. Bit 17 is set if there was an overrun anywhere during the frame. Bit 16 is set if the frame ended with an Abort. Bit 15 is set if the frame had a CRC error. Bit 14 is set if the last byte in the frame is not a full eight bits. Bits 13-0 contain the byte count for the frame. This is the number of bytes written to the FIFO by the receiver, which will also be the number of bytes read from the FIFO in the absense of an overrun.

- hdlc\_mode (input, active-High) The HDLC Mode control signal selects the operating mode for the receiver. Low selects Async, while High selects HDLC.

- par\_en (input, active-High). The Enable Parity control signal enables the parity checker in Async mode and is ignored in HDLC mode. Parity checking automatically adds one bit to the selected charater length. Low disables parity checking and High enables parity checking.

- par\_sel (input, 2-bit bus) The Parity Select signals select the type of parity to check for in Async mode and are ignored in HDLC mode. Bit combination 00 selects even parity, 01 selects odd parity, 10 selects Space (always zero) parity and 11 selects Mark (always High) parity. These signals are ignored if parity is not enabled.

- rd\_data (input, 3-bit bus) The Read Data signals remove data from the buffer. Only one

rd\_data signal may be active at a time, and then only for one clock cycle.

Because the data ripples through the buffer only byte reads every clock cycle are supported. Word reads can occur no faster than every other clock cycle, and long reads must obviously wait for the entire buffer to fill. Bit 0 is the byte read strobe, bit 1 is the word read strobe, and bit 2 is the long read strobe.

- **resetb** (input, active-Low) The Master Reset signal is used to initialize most of the flipflops in the design.

- rx\_hunt (input, active-High) The Enter Hunt signal is used to force the receiver to halt frame assembly and wait for a Flag in HDLC mode and is not used in Async mode. This signal should be active (High) for one clock cycle, and is usually used to halt reception in the case of an address mismatch.

- **rx\_sync** (input, active-High) The Receive Sync signal is the "clock" for the receiver. This signal is active at the data rate for HDLC mode and at 8x or 16x the data rate

in Async mode. If High all the time, the HDLC data rate is the **clkp** rate and the Async data rate is either **clkp**/16 or **clkp**/8. Internally the **rx\_sync** signal is used as a clock-enable for flip-flops operating at the data rate.

- rxd\_asyn (input) The Async Receive Data signal is the data input in Async mode and is ignored in HDLC mode. The rxd\_asyn signal is sampled in the center of the bit cell in both 8x and 16x mode.

- rxd\_syn (input) The Synchronous Receive Data signal is the data input in HDLC mode and is ignored in Async mode. The rxd\_syn signal is sampled whenever the rx\_sync signal is active. A separate data input for HDLC is used to allow for an external data decoder in the signal path.

- serx\_test (input, active-High) The Serial Test signal is used only for testing, and modifies the frame length counter to allow shorter test times. Low is normal mode and High is test mode.

## **Async/HDLC Transmitter**

### hdlc\_tx

The **hdlc\_tx** module is the Async/HDLC transmitter. This transmitter contains four bytes of buffering, which allows for connection to an 8-, 16- or 32-bit bus or external FIFO. Buffer-empty signals for each byte in the buffer, along with byte, word and long write strobes simplify the interface to an external bus or FIFO. Status is buffered along with each byte, to carry address/data information in Async mode and End-of-Frame information in HDLC mode.

In Async mode the clock can be either sixteen (the default) or eight times the data rate. In HDLC mode the clock is sixteen times the data rate. Thus the maximum data rate is the peripheral clock frequency divided by eight in Async mode and divided by sixteen in HDLC mode. With the external clock option in HDLC mode the maximum rate for the bit rate is **clkp**/5 because of the synchronization logic in the clock and data paths.

In Async mode the port can send and receive seven or eight bits and has the option of appending and recognizing an additional address bit. On transmit, the address bit is automatically appended to the data when the data is tagged with special status signals. Writing the data with **tag\_addr** signal active appends a "zero" address bit to the data, while writing the data with the **tag\_long** signal active appends an "one" address bit to the data. The address bit is followed by a normal stop bit. This status information is buffer along with the data.

HDLC mode encapsulates data within opening and closing Flags, and sixteen or thirty-two bits of CRC precedes the closing Flag. All information between the opening and closing Flag is "zero-stuffed". That is, if five consecutive ones occur, independent of byte boundaries, a zero is automatically inserted by the transmitter and automatically deleted by the receiver. This allows a Flag byte (07Eh) to be unique within the serial bit stream.

Both the CCITT polynomial  $(x^{16}+x^{12}+x^5+1)$  and Ethernet polynomial  $(x^{32}+x^{26}+x^{23}+x^{22}+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x^1+1)$  are available, with the generator preset to all ones.

Transmit operation is essentially automatic. In the transmitter, the CRC generator is preset and the opening Flag is transmitted automatically after the first byte is written to the transmitter buffer, and CRC and the closing flag are transmitted after the byte that is written to the buffer with the **tag\_addr** signal active. If no CRC is required, writing the last byte of the frame with the **tag\_long** signal active automatically appends a closing flag after the tagged byte. If the transmitter underflows, either an Abort or a Flag will be transmitted, under program control.

A command is available to send the Abort pattern (seven consecutive ones) if a transmit frame needs to be aborted prematurely. The Abort command takes effect on the next byte boundary, and causes the transmission of an FEh (a zero followed by seven ones), after which the transmitter will send the idle line condition. The Abort command also purges the transmit FIFO. The idle line condition may be either Flags or all ones.

An interrupt is generated every time a byte is removed from the transmitter buffer. The transmitter also generates an interrupt at the end of CRC transmission, at the end of the transmission of an Abort sequence, and at the end of the transmission of a closing Flag.

The transmitter is not capable of sending an arbitrary number of bits, but only a multiple of bytes. Thus and idle line will always be a multiply of eight bit times, irrespective of whether using Mark idle or Flag idle.

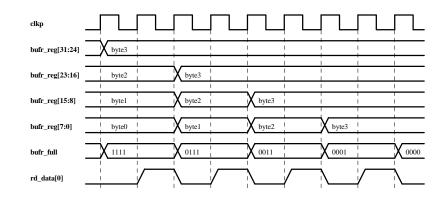

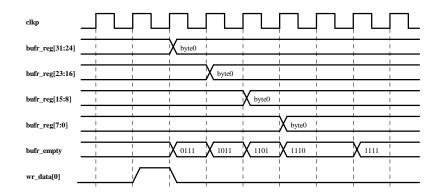

As mentioned previously, data ripples through the buffer. The diagram below shows a byte being written to the buffer and then rippling through before being taken by the transmitter. Date can be removed from the buffer by the transmitter as soon as one clock cycle after entering the least-significant byte of the buffer.

The diagram below shows word data being written to the buffer and rippling through before the first byte is taken by the transmitter.

The diagram below shows long data being written to the buffer and then the first byte being taken by the transmitter.

#### Interface

The interface signals for the **hdlc\_tx** module are detailed below. All inputs except for the reset are sampled by the rising edge of the clock and all outputs except for the transmit data change in response to the rising edge of the clock.

- **asyn\_fast** (input, active-High) The Async Fast control signal selects the clock divide ratio for Async mode and is ignored in HDLC mode. Low selects divide-by-16, while High selects divide-by-8.

- **bits7** (input, active-High) The 7 Bits/Character control signal selects the number of data bits per character for Async mode and is ignored in HDLC mode. Low selects 8 data bits/character, while High selects 7 data bits/character.

- **bufr\_empty** (input, 4-bit bus) The Empty Tag bits accompany data in the data buffer, tagging each byte as full or empty. Low signals full and High signals empty. Note that data ripples through the buffer. Refer to the timing diagrams below for details. These bits should be used to create interrupt requests DMA requests, and read signals for an external FIFO.

clkp (input, active-High) The Peripheral Clock connects to all flip-flops in the module.

- **clr\_int** (input, active-High) The Clear Interrupt signal is used to clear the **txint\_reg** status when no further data is to be written. This signal should go active for one clock cycle to clear the transmit interrupt.

- crc32\_en (input, active-High) The CRC32 Enable control signal selects the CRC polynomial to use in HDLC mode and is ignored in Async mode. Low selects the CCITT polynomial (x<sup>16</sup>+x<sup>12</sup>+x<sup>5</sup>+1), while High selects the Ethernet polynomial (x<sup>32</sup>+x<sup>26</sup>+x<sup>23</sup>+x<sup>22</sup>+x<sup>16</sup>+x<sup>12</sup>+x<sup>11</sup>+x<sup>10</sup>+x<sup>8</sup>+x<sup>7</sup>+x<sup>5</sup>+x<sup>4</sup>+x<sup>2</sup>+x<sup>1</sup>+1).

- hdlc\_mode (input, active-High) The HDLC Mode control signal selects the operating mode for the transmitter. Low selects Async, while High selects HDLC.

- **irda\_mode** (input, active-High) The IRDA Mode control signal enables special operation for the transmitter in HDLC mode and is ignored in Async mode. Low selects normal mode, with one opening Flag in a frame, while High selects the special case of two opening flags in a frame.

- mrk\_idl (input, active-High) The Mark Idle control signal enables special operation for the transmitter in HDLC mode and is ignored in Async mode. Low selects

normal mode, with continuous Flags transmitted between frames, while High selects the special case of continuous ones transmitted between frames.

- par\_en (input, active-High). The Enable Parity control signal enables the parity generatorer in Async mode and is ignored in HDLC mode. Parity generation automatically adds one bit to the selected charater length. Low disables parity generation and High enables parity generation.

- par\_sel (input, 2-bit bus) The Parity Select signals select the type of parity to generate in Async mode and are ignored in HDLC mode. Bit combination 00 selects even parity, 01 selects odd parity, 10 selects Space (always zero) parity and 11 selects Mark (always High) parity. These signals are ignored if parity is not enabled.

- pwrite\_bus (input, 32-bit bus) This is the data for the transmit data buffer. Bytes ripple through the FIFO from most-significant byte to least-significant byte. A Byte write transfer pwrite\_bus[7:0] the msbyte of the buffer, which then ripples to the right. A Word write pwrite\_bus[15:0] the two msbytes of the buffer which then ripple to the right. A Long write fills all four bytes of the buffer. The right-most byte of the buffer is transmitted first.

- **resetb** (input, active-Low) The Master Reset signal is used to initialize most of the flipflops in the design.

- **serx\_tsync** (output, active-High) The Serial Tx Sync signal is active for one clock cycle at the start of each transmit bit. This signal is used by an IRDA encoder to trigger the monostable multivibrator that does the IRDA encoding.

- tag\_addr (input, 4-bit bus) The Address Tag bits accompany data in the data buffer, marking a byte to be transmitted with a Zero between the last data bit or the parity bit and the Stop bit in Async mode and marking the last byte in a frame in HDLC mode. Low has no effect, while High marks the byte as "address" or "EOF".

- **tag\_long** (input, 4-bit bus) The Long Stop Tag bits accompany data in the data buffer, marking a byte to be transmitted with a One between the last data bit or the parity bit and the Stop bit in Async mode. These signal are not used in HDLC mode. Low has not effect, while High markes the byte as "data". When not sending an address/data bit, these signals may be tied High to always send two stop bits in Async mode.

- tx\_abrt (input, active-High) The Transmit Abort signal is used to force the transmitter to halt frame transmission and send a Abort (0x7F) in HDLC mode and is not used in Async mode. This signal should be active (High) for one clock cycle,

and is usually used to halt transmission because of some higher-level protocol error.

tx\_data (output) The Transmit Data signal is the serial output from the transmitter.

- tx\_status (output, 2-bit bus) The Transmit Status signals reports the state of the transmitter. In Async mode only bit 1 is used: Low signals that the transmitter is idle and High signals that the transmitter is sending a byte. In HDLC mode bit combination 00 signals that the transmit interrupt is due to a buffer empty condition; bit combination 01 signals that the CRC transmission is complete; bit combination 10 signals that the Abort transmission is complete; and bit combination 11 signals that transmission of the closing Flag is complete. The txint\_reg signal is set by any change on tx\_status.

- tx\_sync (input, active-High) The Transmit Sync signal is the "clock" for the transmitter. This signal is active at the data rate for HDLC mode and at 8x or 16x the data rate in Async mode. If High all the time, the HDLC data rate is the clkp rate and the Async data rate is either clkp/16 or clkp/8. Internally the tx\_sync signal is used as a clock-enable for flip-flops operating at the data rate.

- txint\_reg (output, active-High) The Transmit Interrupt signal is setwhenever a byte is removed from the transmit buffer, and when there is any change of state on a tx\_status signal. The normal response to a transmit interrupt is to write more data to the buffer, but tha interrupt can also be cleared via the clr\_int signal if no data is being transferred to the buffer.

- **urun\_abrt** (input, active-High). The Underrun Abort control signal is ignored in Async mode and is used in HDLC mode to enable the transmitter to automatically send an Abort if the transmitter underruns.

- wr\_data (input, 3-bit bus) The Write Data signals load data to the buffer. Only one wr\_data signal may be active at a time, and then only for one clock cycle. Because the data ripples through the buffer only byte reads every clock cycle are supported. Word reads can occur no faster than every other clock cycle, and long reads must obviously wait for the entire buffer to fill. Bit 0 is the byte write strobe, bit 1 is the word write strobe, and bit 2 is the long write strobe.

# **Digital Phase-locked Loop**

### dpll\_top

The **dpll\_top** module is a digital phase-locked loop (DPLL) to recover the clock from an encoded HDLC serial data stream. It is clocked at 16x the bit rate, and generates a clock enable suitable for decoding the receive data. A fixed /16 clock enable output suitable for clocking the transmit data is also provided.

The DPLL is just a divide-by-16 counter that uses the timing of the transitions on the receive data stream to adjust its count. The DPLL adjusts the count so that the output of the DPLL will be properly placed in the bit cells to sample the receive data.

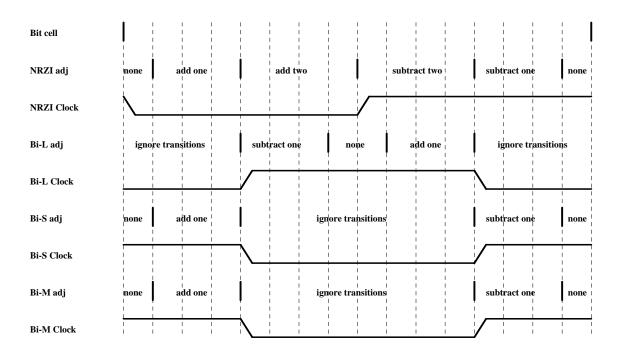

To work properly, then, transitions are required in the receive data stream. NRZ data encoding does not guarantee transitions in all cases (a long string of zeros for example), but other data encodings do. NRZI guarantees transitions because of the HDLC inserted zeros, and the Biphase encodings all have at least one transition per bit cell.

The DPLL counter normally counts by sixteen, but if a transition occurs earlier or later than expected the count will be modified during the next count cycle. If the transition occurs earlier than expected, it means that the bit cell boundaries are early with respect to the DPLL-tracked bit cell boundaries, so the count is shortened, either by one or two counts. If the transition occurs later than expected, it means that the bit cell boundaries are late with respect to the DPLL-tracked bit cell boundaries, so the count is lengthened, either by one or two counts. The decision to adjust by one or by two depends on how far off the DPLLtracked bit cell boundaries are. This tracking allows for minor differences in the transmit and receive clock frequencies.

With NRZ and NRZI data encoding, the DPLL counter runs continuously, and adjusts after every receive data transition. Since NRZ encoding does not guarantee a minimum density of transitions, the difference between the sending data rate and the DPLL output clock rate must be very small, and depends on the longest possible run of zeros in the received frame. NRZI encoding guarantees at least one transition every six bits (with the inserted zeros). Since the DPLL can adjust by two counts every bit cell, the maximum difference between the sending data rate and the DPLL output clock rate is 1/48 (~2%).

With Biphase data encoding (either -Level, -Mark or -Space), the DPLL runs only as long as transitions are present in the receive data stream. Two consecutive missed transitions causes the DPLL to halt operation and wait for the next available transition. This mode of operation is necessary because it is possible for the DPLL to lock onto the optional transi-

tions in the receive data stream. Since they are optional, they will eventually not be present and the DPLL can attempt to lock onto the required transitions. Since the DPLL can adjust by one count every bit cell, the maximum difference between the sending data rate and the DPLL output clock rate is 1/16 (~6%).

With Biphase data encoding the DPLL is designed to work in multiple-access conditions where there may not be Flags on an idle line. The DPLL will properly generate an output clock based on the first transition in the leading zero of an opening Flag. Similarly, only the completion of the closing Flag is necessary for the DPLL to provide the extra two clocks to the receiver to properly assemble the data. In Biphase-Level mode, this means the transition that defines the last zero of the closing Flag. In Biphase-Mark and Biphase-Space modes this means the transition that defines the end of the last zero of the closing Flag.

The figure below shows the adjustment ranges and output clock for the different modes of operation of the DPLL. Each mode of operation will be described in turn.

With NRZ and NRZI encoding all transitions occur on bit-cell boundaries and the data should be sampled in the middle of the bit cell. If a transition occurs after the expected bit-cell boundary (but before the midpoint) the DPLL needs to lengthen the count to line up the bit-cell boundaries. This corresponds to the "add one" and "add two" regions shown. If a transition occurs before the bit cell boundary (but after the midpoint) the DPLL needs to shorten the count to line up the bit-cell boundaries. This corresponds to the "subtract one"

and "subtract two" regions shown. The DPLL makes no adjustment if the bit-cell boundaries are lined up within one count of the divide-by-sixteen counter. The regions that adjust the count by two allow the DPLL to synchronize faster to the data stream when starting up.

With Biphase-Level encoding there is a guaranteed "clock" transition at the center of every bit cell and optional "data" transitions at the bit cell boundaries. The DPLL only uses the clock transitions to track the bit cell boundaries, by ignoring all transitions occurring outside a window around the center of the bit cell. This window is half a bit-cell wide. Additionally, because the clock transitions are guaranteed, the DPLL requires that they always be present. If no transition is found in the window around the center of the bit cell for two successive bit cells the DPLL is not in lock and immediately enters the search mode. Search mode assumes that the next transition seen is a clock transition and immediately synchronizes to this transition. No clock output is provided to the receiver during the search operation. Decoding Biphase-Level data requires that the data be sampled at either the quarter or three-quarter point in the bit cell. The DPLL here uses the quarter point to sample the data.

Biphase-Mark and Biphase-Space encoding are identical as far as the DPLL is concerned, and are similar to Biphase-Level. The primary difference is the placement of the clock and data transitions. With these encodings the clock transitions are at the bit-cell boundary and the data transitions are at the center of the bit cell, and the DPLL operation is adjusted accordingly. Decoding Biphase-Mark or Biphase-Space encoding requires that the data be sampled by both edges of the recovered receive clock.

#### Interface

The interface signals for the **dpll\_top** module are detailed below. All inputs except for the reset are sampled by the rising edge of the clock and all outputs change in response to the rising edge of the clock.

clkp (input, active-High) The Peripheral Clock connects to all flip-flops in the module.

**dec\_mode** (input, 3-bit bus) The Decode Mode bus selects the type of data encoding that the DPLL will expect for the serial data according to the table below. Any bit combinations not shown are invalid.

| dec_mode | Data encoding |  |  |

|----------|---------------|--|--|

| 000      | NRZ           |  |  |

| 010      | NRZI          |  |  |

| 100      | Biphase-Level |  |  |

| 110      | Biphase-Space |  |  |

| 111      | Biphase-Mark  |  |  |

- dpll\_en (input, active-High) The DPLL Enable control signal enables the DPLL. While disabled the dpll\_rxmain, dpll\_rxmid, dpll\_txmain and dpll\_txmid signals are all Low. The dpll\_tclk signal holds the last value and the dpll\_rclk signal is Low unless the dec\_mode is selecting biphase-mark or biphase-space.

- **dpll\_rclk** (output) The DPLL Receive Clock is a square wave (in the absense of adjustments) sutiable for external use with the receive data. Refer to the table below for the phase of this signal relative to the bit cell.

- **dpll\_rxmain** (output) The DPLL Main Rx Clock is a one clock cycle pulse at the appropriate main sampling point for the receive data. This corresponds to the rising edge of the **dpll\_rclk** signal. The table below shows the location within the bit cell for the various dpll output signals.

| dec_mode | Data encoding | dpll_rxmain | dpll_rxmid | dpll_txmain | dpll_txmid |

|----------|---------------|-------------|------------|-------------|------------|

| 000      | NRZ           | center      | none       | boundary    | center     |

| 010      | NRZI          | center      | none       | boundary    | center     |

| 100      | Biphase-Level | 1/4 point   | none       | boundary    | center     |

| 110      | Biphase-Space | 3/4 point   | 1/4 point  | boundary    | center     |

| 111      | Biphase-Mark  | 3/4 point   | 1/4 point  | boundary    | center     |

- **dpll\_rxmid** (output) The DPLL Middle Rx Clock is a one clock cycle pulse at the appropriate main sampling point for the receive data with Biphase-Space and Biphase-Mark encoding. These encoding methods require two samples of the data per bit cell to decode.

- **dpll\_tclk** (output) The DPLL Transmit Clock is a square wave sutiable for external use with the transmit data.

- **dpll\_txmain** (output) The DPLL Main Tx Clock is a one clock cycle pulse at the falling edge of the transmit clock for use by the transmitter.

- **dpll\_txmid** (output) The DPLL Middle Tx Clock is a one clock cycle pulse at the rising edge of the transmit clock for use by the transmitter.

- **resetb** (input, active-Low) The Master Reset signal is used to initialize most of the flipflops in the design.

- serx\_rxd (input) The Serial Receive Data signal is the encoded serial data input.

- tr\_sync (input, active-High) The Transmit/Receive Sync signal is the "clock" for the DPLL. This signal is pulses High for one clock cycle at 16x the data rate. If High all the time, data rate is the clkp rate divided by 16.

# **IRDA Encode/Decode**

### irda\_top

The **irda\_top** module decodes IRDA receive data into NRZ and encodes NRZ transmit data into IRDA transmit data. It is clocked at 16x the bit rate when used with HDLC and either 8x or 16x the bit rate for Async. Enabling the IRDA-compliant encode/decode modifies the transmitter in HDLC mode so that there are always two opening Flags transmitted.

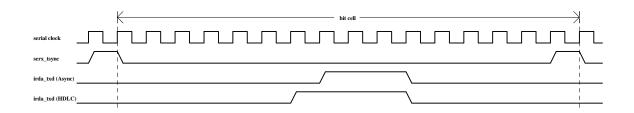

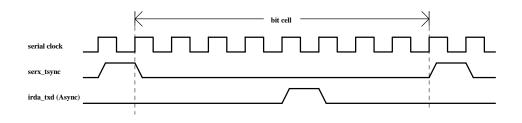

The IRDA encoder sends an active-High pulse for a zero and no pulse for a one. In the asynchronous 16x mode this pulse is 3/16ths of a bit cell wide, while in the asynchronous 8x mode it is 1/8th of a bit cell wide. In HDLC mode the pulse is 1/4th of a bit cell wide. The diagram below shows the details of the timing for 16x Async and HDLC. Note that the encoded introduces a few **clkp** cycles of delay into the signal.

The diagrams below shows the details of the timing for the 8x Async case.

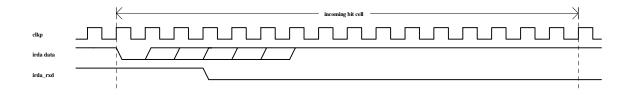

The IRDA decoder watches for active-Low pulses, which are stretched to one bit time wide to recreate the normal NRZ serial waveform for the receiver. The diagram below

shows the details of the timing for the receive data. The relative timing is identical for Async (8x and 16x) and HDLC modes.

#### Interface

The interface signals for the **irda\_top** module are detailed below. All inputs except for the reset are sampled by the rising edge of the clock and all outputs change in response to the rising edge of the clock.

- **asyn\_fast** (input, active-High) The Async Fast control signal selects the clock divide ratio for Async mode and is ignored in HDLC mode. Low selects divide-by-16, while High selects divide-by-8.

- clkp (input, active-High) The Peripheral Clock connects to all flip-flops in the module.

- hdlc\_mode (input, active-High) The HDLC Mode control signal selects the operating mode for the encoder and decoder. Low selects Async, while High selects HDLC.

- **irda\_mode** (input, active-High) The IRDA Mode control signal enables the encoder and decoder. Low disables the encoder and decoder while High enables them both.

- irda\_rxd (output) The IRDA Receive Data signal is the decoded receive data.

- irda\_txd (output) The IRDA Transmit Data signal is the encoded transmit data.

- **resetb** (input, active-Low) The Master Reset signal is used to initialize most of the flipflops in the design.

- serx\_rdat (input) The Serial Receive Data signal is the encoded serial data input.

- **serx\_tsync** (input, active-High) The Serial Tx Sync signal is active for one clock cycle at the start of each transmit bit. This signal is used by the encoder to trigger the monostable multivibrator that does the IRDA encoding.

- tr\_sync (input, active-High) The Transmit/Receive Sync signal is the "clock" for the encoder/decoder. This signal is pulses High for one clock cycle at 16x the data rate. If High all the time, data rate is the clkp rate divided by 16.

- tx\_data (input) The Transmit Data signal is the serial output from the transmitter.

## **Encoder/Decoder**

### endec\_top

The **endec\_top** module encodes and decodes the serial data. It also contains the synchronization logic required for the serial data and clock signal to cross into the **clkp** clock domain.

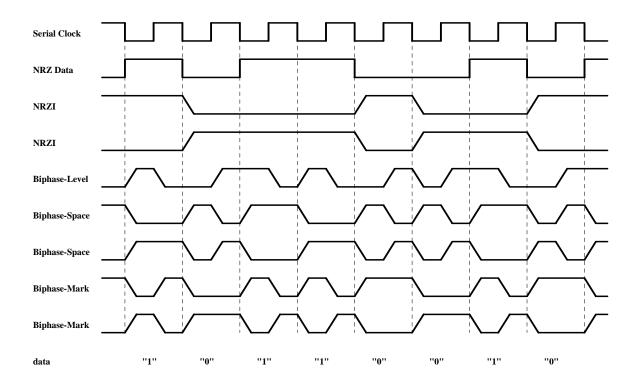

Several types of data encoding are available in the HDLC mode. In addition to the normal NRZ, they are NRZI, Biphase-Level (Manchester), Biphase-Space (FM0) and Biphase-Mark (FM1). Examples of these encodings are shown in the Figure below. Note that in NRZI, Biphase-Space and Biphase-Mark the signal level does not convey information. Rather it is the placement of the transitions that determine the data. In Biphase-Level it is the polarity of the transition that determines the data.

The serial clock signals from outside the hdlc\_top module are all synchronized to the clkp clock domain in the **endec\_top** module. These signals are the external receive clock

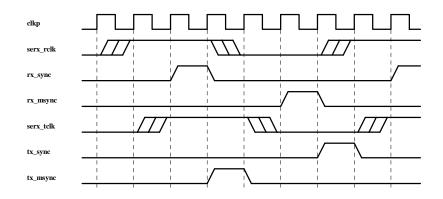

(**serx\_rclk**) and the external transmit clock (**serx\_tclk**). The diagram below shows the timing for the synchronizers. Because of this synchronization, the data rate when using data encoding and decoding is limited to **clkp**/4 for synchronous serial clocks and **clkp**/5 for asynchronous serial clocks.

The tranmsit data out of the **endec\_top** module in the case of HDLC mode with an external clock uses the actual external transmit clock (**serx\_tclk**) to time the transmit data. However the decoder, in the same case, does not use the external clock to sample the receive data. This can be done externally to **hdlc\_top** if an edge-synchronous sampling point for the receive data is required.

#### Interface

The interface signals for the **endec\_top** module are detailed below. All inputs except for the reset are sampled by the rising edge of the clock and almost all outputs change in response to the rising edge of the clock.

clkp (input, active-High) The Peripheral Clock connects to all flip-flops in the module.

- comclk\_en (input, active-High) The Common Clock Enable control signal enables the receive clock to be sourced from the transmit clock input (HDLC mode with external clock). Low enables the receive clock to be sourced from the serx\_rclk signal, while High enables the receive clock to be sources from the serx\_tclk signal.

- **dec\_mode** (input, 3-bit bus) The Decode Mode bus selects the type of data encoding expected for the serial receive data, according to the table below. Any bit combinations not shown are invalid.

| dec_mode | Data encoding |  |  |  |

|----------|---------------|--|--|--|

| 000      | NRZ           |  |  |  |

| 010      | NRZI          |  |  |  |

| 100      | Biphase-Level |  |  |  |

| 110      | Biphase-Space |  |  |  |

| 111      | Biphase-Mark  |  |  |  |