# HP-41 MAXX

Every effort has been made to ensure the accuracy of the information contained herein. If you find errors or inconsistencies please bring them to our attention.

Copyright © 2023, Systemyde International Corporation. All rights reserved.

#### Notice:

"HP-41C", "HP-41CV", "HP-41CX" and "HP" are registered trademarks of Hewlett-Packard, Inc. All uses of these terms in this document are to be construed as adjectives, whether or not the noun "calculator", "CPU" or "device" are actually present.

#### Acknowledgements:

**Ángel Martin** provided the functions to use Expanded memory, the CPYBNK function and several figures in this manual. He also reviewed multiple versions of this manual and did beta testing on the module.

**Sylvain Côté** provided several figures used in this manual and introduced the module to the world with a presentation at HHC 2022. He also reviewed multiple versions of this manual and did beta testing on the module.

**Robert Prosperi** reviewed early versions of this manual and suggested including the HP-IL Code Copy functions.

Screenshots are taken from Warren Furlow's V41 program.

## **Table of Contents**

| 1. | READ THIS FIRST                                                  | 6  |

|----|------------------------------------------------------------------|----|

| 2. | Introduction                                                     | 7  |

| 3. | HP-41 MAXX Configurations                                        | 8  |

| 4. | MAXX Software Overview                                           | 16 |

| 5. | MAXX Status Functions                                            | 17 |

|    | MXST? (MAXX Hardware Status?)                                    |    |

|    | <b>QRST?</b> (QROM Status?)                                      |    |

| 6. | Expanded Memory Block Functions                                  | 20 |

|    | <b>ST&gt;YM</b> (Move Status Block to Expanded Memory)           | 22 |

|    | <b>ST&lt;&gt;YM</b> (Exchange Status Block with Expanded Memory) | 23 |

|    | YM>ST (Move Expanded Memory to Status Block)                     |    |

|    | <b>MM&gt;YM</b> (Move Main Memory to Expanded Memory)            | 23 |

|    | MM<>YM (Exchange Main Memory with Expanded Memory)               | 23 |

|    | <b>YM&gt;MM</b> (Move Expanded Memory to Main Memory)            | 23 |

|    | XM>YM (Move Extended Memory to Expanded Memory)                  | 24 |

|    | XM<>YM (Exchange Extended Memory with Expanded Memory)           |    |

|    | YM>XM (Move Expanded Memory to Extended Memory)                  | 24 |

|    | YM<>YM (Exchange Expanded Memory Blocks)                         | 24 |

|    | YMCLR (Clear Expanded Memory)                                    | 24 |

| 7. | Expanded Register Functions                                      | 25 |

|    | YARC (Expanded Register Alpha Recall)                            | 31 |

|    | YAST (Expanded Register Alpha Store)                             |    |

|    | <b>YDSE</b> (Expanded Register Decrement, Skip If Equal)         |    |

|    | YISG (Expanded Register Increment, Skip If Greater)              | 32 |

|    | YRCL (Expanded Register Recall)                                  | 32 |

|    | YRC+ (Expanded Register Recall and Add)                          | 32 |

|    | YRC- (Expanded Register Recall and Subtract)                     | 32 |

|    | <b>YRC*</b> (Expanded Register Recall and Multiply)              | 32 |

|    | <b>YRC/</b> (Expanded Register Recall and Divide)                | 33 |

| <b>YSTO</b> (Expanded Register Store)                               | 33 |

|---------------------------------------------------------------------|----|

| <b>YST+</b> (Expanded Register Store with Add)                      | 33 |

| <b>YST-</b> (Expanded Register Store with Subtract)                 | 33 |

| <b>YST</b> * (Expanded Register Store with Multiply)                | 33 |

| <b>YST/</b> (Expanded Register Store with Divide)                   | 33 |

| YVEW (Expanded Register View)                                       | 34 |

| <b>YX</b> <> (Expanded Register Exchange with X-register)           | 34 |

| 8. Expanded Register Block Functions                                | 35 |

| <b>YRGMOV</b> (Move Expanded Register Block)                        | 35 |

| YRGSWP (Exchange Expanded Register Blocks)                          |    |

| CLYRG (Clear Expanded Register Block)                               | 35 |

| <b>CLYRGX</b> (Clear Expanded Register Block by X-register)         | 36 |

| A<>YRG (Exchange Alpha Register with Expanded Register Block)       | 36 |

| <b>ST&lt;&gt;YRG</b> (Exchange Stack with Expanded Register Block)  |    |

| 9. QROM Functions                                                   | 37 |

| <b>QRABY</b> (QROM Set Address/Bank by Y-register)                  | 38 |

| QRCLR (QROM Clear)                                                  |    |

| QRINI (QROM Initialize)                                             |    |

| QRRE (QROM Read Enable)                                             |    |

| QRRO (QROM Read-Only)                                               |    |

| QRRP (QROM Read Protect)                                            |    |

| <b>QRRWE</b> (QROM Read and Write Enable)                           |    |

| <b>QRRWD</b> (QROM Read and Write Disable)                          |    |

| <b>QRWE</b> (QROM Write Enable)                                     |    |

| QRWO (QROM Write-Only)                                              |    |

| <b>QRWP</b> (QROM Write Protect)                                    |    |

| 10. Instruction Memory Functions                                    | 41 |

| -                                                                   |    |

| AH>XD (Hex Address/Data to Decimal Address/Data)                    |    |

| AHPEEK (Instruction Memory Read using Hex Address/Data)             |    |

| AHPOKE (Instruction Memory Write using Hex Address/Data)            |    |

| XD>AH (Decimal Address/Data to Hex Address/Data)                    |    |

| <b>XDPEEK</b> (Instruction Memory Read using Decimal Address/Data)  |    |

| <b>XDPOKE</b> (Instruction Memory Write using Decimal Address/Data) | 43 |

| 11. Code Copy Functions                                             | 44 |

| CPYBNK (Copy Bank)                                                  | 44 |

| 12. | HP-IL Code Copy Functions                       |    |

|-----|-------------------------------------------------|----|

|     | RDEIL (Load ROM Page via HP-IL, ERAMCO format)  |    |

|     | RDHIL (Load ROM Page via HP-IL, HEPAX format)   | 47 |

|     | WREIL (Store ROM Page via HP-IL, ERAMCO format) | 47 |

|     | WRHIL (Store ROM Page via HP-IL, HEPAX format)  | 47 |

| 13. | Error Messages                                  |    |

| 14. | Function XROM Numbers                           |    |

| 15. | QROM Loading Examples                           |    |

| 16. | Internal Details                                | 53 |

|     | Hardware Control Register                       | 54 |

|     | QROM Control Registers                          | 55 |

|     | Scratch x Registers                             |    |

|     | Translate Input Register                        |    |

|     | Five Bytes Register                             | 57 |

|     | Four Words Register                             | 57 |

|     | Indirect Data Register                          | 59 |

|     | ROM Control Register                            | 59 |

|     | Indirect Address Register                       | 59 |

|     | Expanded Register Access                        | 60 |

| 17. | Revision History                                | 61 |

## **READ THIS FIRST**

### When First Inserting the HP-41 MAXX Module

The HP-41 MAXX module uses a Field-Programmable Gate Array (FPGA) to implement all of the logic and memory in the module. An FPGA must be loaded with the logic and memory contents at power-up, and until this process is complete the FPGA outputs are undefined. This undefined state can sometimes cause the bus drivers in the MAXX module to drive the HP-41 bus.

One particular bus signal (ISA) is used to wake up the HP-41 processor if driven while the HP-41 is off. (This is how the button on Wand works and how the Time Module displays the time continuously.) If this happens the HP-41 may wake up and then lock up when the HP-41 MAXX module is inserted into the calculator.

To clear this condition, first try pressing **ON** several times. If this doesn't work remove the batteries and then press **ON** several times before re-inserting the batteries. Insert the batteries, wait a few seconds, and then turn on the calculator. It may take a few tries for this to work, but once the calculator starts responding everything should be fine.

### Neither QROM memory nor Expanded memory is initialized!

QROM blocks and Expanded memory are implemented using RAM, and are not initialized at power-up. The random data in a QROM block will almost certainly crash the calculator if the QROM block is enabled for reads prior to being initialized or loaded with actual data. Similarly, the random data in Expanded memory will likely cause problems if transferred to main memory. Here is the recommended initialization sequence to start up a calculator after first inserting the HP-41 MAXX module:

| ← ON    | Force a Memory Clear condition, which will initialize Main memory. |

|---------|--------------------------------------------------------------------|

| QRINI   | Clear all of QROM.                                                 |

| YMCLR 1 | Clear Expanded memory block 1.                                     |

| YMCLR 2 | Clear Expanded memory block 2.                                     |

| YMCLR 3 | Clear Expanded memory block 3.                                     |

|         | Finally, initialize the Time module with the time and date.        |

### All HP-41 MAXX memory is volatile!

All of the RAM in the HP-41 MAXX module is volatile and will lose its contents when power is removed.

### Introduction

The HP-41 MAXX module is designed to expand an HP-41C, CV or CX calculator to the maximum capabilities envisioned for an HP-41 system. The HP-41 MAXX module implements all of these 41C modules in a single physical module:

- Four Memory modules (82106A)

- X-Functions/Memory module (82180A)

- Two X-Memory modules (82181A)

- Time module (82182A)

This module automatically scans the system every time the calculator is turned on and only activates those features not detected in the system. So for a bare-bones HP-41C all of these features will be activated, while for a HP-41CX only the two X-Memory modules will be activated. Any combination of features between these two extremes will be automatically recognized by the HP-41 MAXX module.

But the HP-41 MAXX module goes even further, adding these advanced features that were never part of the original HP-41 ecosystem:

- Three pages (each containing 1024 registers) of Expanded memory

- Twelve pages (each containing 4Kx10 bits) of RAM for instruction memory

Expanded memory (also referred to as Y-memory or Y-registers) was first introduced with the 41CL and consists of three blocks containing 1024 registers each. All three blocks can be used as a backup or alternate set of main 41C registers, with functions to easily move groups of registers between blocks. One of these blocks can be used as 1024 individual Y-registers, with a full complement of register functions.

There are twelve pages of RAM dedicated to holding code, to allow module images to be copied to RAM for editing or other purposes. Each page of this QROM (Quasi-ROM) can be assigned to any available page address (4 or 6 through 15) and to any Bank within that page. Historically, this functionality has also been referred to as MLDL memory, and this RAM can also function as HEPAX memory. Each page can be write-protected using the HEPAX write-protection mechanism.

## **HP-41 MAXX Configurations**

The HP-41 MAXX module queries the system at each power-on and only enables those features that do not conflict with the detected system. Even though a MAXX feature may be disabled because of a change in system configuration, the contents of RAM are not lost unless power is removed.

There are nine different possibilities for how a MAXX module might be combined with other modules containing register memory in a system:

| 1 | 41C  |         |       |         | + MAXX |

|---|------|---------|-------|---------|--------|

| 2 | 41C  | + MM    |       |         | + MAXX |

| 3 | 41C  | + MM x2 |       |         | + MAXX |

| 4 | 41C  | + MM x3 |       |         | + MAXX |

| 5 | 41C  | + QM    |       |         | + MAXX |

| 5 | 41CV |         |       |         | + MAXX |

|   | 41C  | + QM    | + XFN |         | + MAXX |

| 6 | 41CV |         | + XFN |         | + MAXX |

|   | 41CX |         |       |         | + MAXX |

|   | 41C  | + QM    | + XFN | + XM    | + MAXX |

| 7 | 41CV |         | + XFN | + XM    | + MAXX |

|   | 41CX |         |       | + XM    | + MAXX |

| 8 | 41C  |         | + XFN | + XM x2 | + MAXX |

| 9 | 41CV |         | + XFN | + XM x2 | + MAXX |

| 9 | 41CX |         |       | + XM x2 | + MAXX |

|   |      |         |       |         |        |

(MM is an 82106A Memory Module, QM is an 82170A Quad Memory Module, XFN is and 82180A X-Functions/Memory Module, and XM is an 82181A X-Memory Module)

Because the HP-41 MAXX requires one Port, the 41C configurations are limited to three other modules. The HP-41CV includes the full compliment of regular memory, so there are fewer possible configurations with an HP-41CV. The HP-41CX lacks only the X-Memory, which limits the possible configurations even more.

Expanded memory is separate and is always enabled, which will never create a conflict because only functions in this module are capable of accessing expanded memory. This means the MAXX module is useful even in the HP-41CX case.

The figure below shows the HP-41 register memory organization graphically with the different possibilities for how the MAXX module may auto-configure. The MAXX contributions to the memory map are shown in blue.

| 1023 | empty      | 0x3FF |   |   |   |   |   |   |   |   |   |

|------|------------|-------|---|---|---|---|---|---|---|---|---|

| 1008 | empty      | 0x3F0 |   |   |   |   |   |   |   |   |   |

| 1007 |            | 0x3EF |   |   |   |   |   |   |   |   |   |

|      |            |       |   |   |   |   |   |   |   |   |   |

|      | X-MEMORY   |       |   |   |   |   |   |   |   |   |   |

|      | (X-MEM #2) |       |   |   |   |   |   |   |   |   |   |

|      |            |       |   |   |   |   |   |   |   |   |   |

| 769  |            | 0x301 |   |   |   |   |   |   |   |   |   |

| 768  | empty      | 0x300 |   |   |   |   |   |   |   |   |   |

| 752  | empty      | 0x2F0 |   |   |   |   |   |   |   |   |   |

| 751  |            | 0x2EF |   |   |   |   |   |   |   |   |   |

|      |            |       |   |   |   |   |   |   |   |   |   |

|      | X-MEMORY   |       |   |   |   |   |   |   |   |   |   |

|      | (X-MEM #1) |       |   |   |   |   |   |   |   |   |   |

|      |            |       |   |   |   |   |   |   |   |   |   |

| 513  |            | 0x201 |   |   |   |   |   |   |   |   |   |

| 512  | empty      | 0x200 |   |   |   |   |   |   |   |   |   |

| 511  |            | 0x1FF |   |   |   |   |   |   |   |   |   |

| 448  |            | 0x1C0 |   |   |   |   |   |   |   |   |   |

| 447  |            | 0x1BF |   |   |   |   |   |   |   |   |   |

| 384  |            | 0x180 |   |   |   |   |   |   |   |   |   |

| 383  | MAIN       | 0x17F |   |   |   |   |   |   |   |   |   |

| 320  | MEMORY     | 0x140 |   |   |   |   |   |   |   |   |   |

| 319  |            | 0x13F |   |   |   |   |   |   |   |   |   |

| 256  |            | 0x100 |   |   |   |   |   |   |   |   |   |

| 255  |            | 0x0FF |   |   |   |   |   |   |   |   |   |

| 192  |            | 0x0C0 |   |   |   |   |   |   |   |   |   |

| 191  | X-MEMORY   | 0x0BF |   |   |   |   |   |   |   |   |   |

| 64   | (X-FUNS)   | 0x040 |   |   |   |   |   |   |   |   |   |

| 63   | empty      | 0x03F |   |   |   |   |   |   |   |   |   |

| 16   |            | 0x010 |   |   |   |   |   |   |   |   |   |

| 15   | STATUS     | 0x00F |   |   |   |   |   |   |   |   |   |

| 0    |            | 0x000 |   |   |   |   |   |   |   |   |   |

| DEC  | HP-41      | HEX   | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

Even though the MAXX module automatically compensates for other memory modules present in the HP-41, it really only makes sense to use the MAXX module by itself to keep as many ports as possible free for other uses

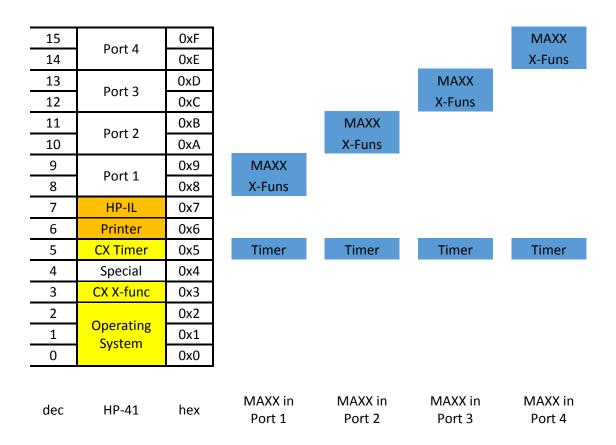

The HP-41 CPU employs a separate address space for instructions. This HP-41 Instruction Address space is organized into sixteen 4k pages, as shown in the left-hand column below. Three or four pages are used by the calculator itself and Page 5 is dedicated for use by the Time module. In addition, Page 6 is reserved for a printer and Page 7 is reserved for the HP-IL module. Page 4 was originally used only by the HP Service module, but recent advances allow it to instead be used to hold library code. Pairs of pages are available in each calculator port.

The columns in blue show the addresses that may be occupied by the HP-41 MAXX module. If the Timer is enabled it will occupy Page 5, while the MAXX and X-Functions software will occupy whichever Port is used to hold the module. The X-Functions code in the MAXX module cannot use Page 3 because only the 41CX Operating System software properly handles code in Page 3.

If the MAXX module is used in a 41CX the lower half of the Port where the module resides will be available for other uses, but the MAXX software always resides in the upper page of this Port.

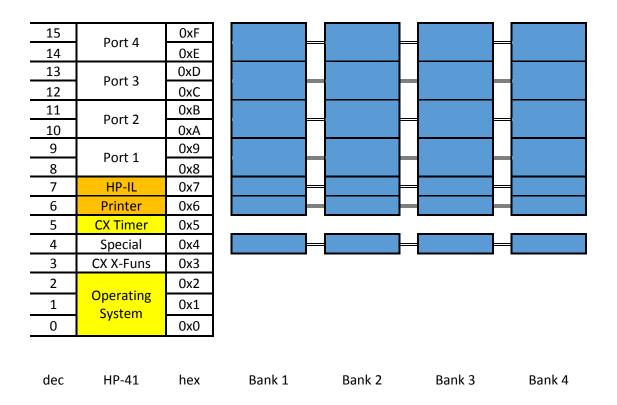

The HP-41 Instruction memory map is actually more complicated than this, because many pages have the option of up to four banks, switched under software control. Pages 4, 6 and 7 each have their own bank-control bits, and each port also has its own bank-control bits.

These bank-control bits are managed using the ENROM*x* mcode instructions. The four ENROM*x* instructions affect the bank-control bits that are linked to the address where the instruction is executed. The figure below shows this memory organization, with the double lines linking the various banks representing the bank-control bits.

The MAXX hardware decodes all four of the ENROM*x* instructions and implements all seven sets of bank-control bits.

| 15  | Dort 4              | 0xF |        |   |       |        |              |

|-----|---------------------|-----|--------|---|-------|--------|--------------|

| 14  | Port 4              | 0xE |        |   |       |        |              |

| 13  | Port 3              | 0xD |        |   |       |        |              |

| 12  | POIL 5              | 0xC |        |   |       |        |              |

| 11  | Port 2              | 0xB |        |   |       |        |              |

| 10  | Port 2              | 0xA |        |   |       |        |              |

| 9   | Dort 1              | 0x9 |        |   |       |        |              |

| 8   | Port 1              | 0x8 |        |   | Г     |        |              |

| 7   | HP-IL               | 0x7 |        |   | =     | _      |              |

| 6   | Printer             | 0x6 |        |   | -     | -      | $\mathbf{H}$ |

| 5   | CX Timer            | 0x5 |        |   |       |        |              |

| 4   | Special             | 0x4 |        | - | =     | -      |              |

| 3   | CX X-Funs           | 0x3 |        |   |       |        |              |

| 2   |                     | 0x2 |        |   |       |        |              |

| 1   | Operating<br>System | 0x1 |        |   |       |        |              |

| 0   | System              | 0x0 |        |   |       |        |              |

|     |                     |     |        |   |       |        |              |

| dec | HP-41               | hex | Bank 1 | B | ank 2 | Bank 3 | Bank 4       |

Not shown in the figure above is the special bank-switching employed by the HP-41CX. In the HP-41CX pages 3 and 5 share a bank-control bit (only banks 1 and 2 are present) to allow an expanded set of X-Functions. This bank-switching is completely independent of the bank-switching in the MAXX module.

There are twelve blocks of QROM available, but each block can be programmed to occupy any available page/bank combination. This flexibility is required to cover the various uses cases, as will be shown shortly.

Every time the calculator is turned on software checks for collisions between physical modules and QROM, and disables any QROM blocks that would conflict with a hardware module. This collision check is only done for QROM blocks that are assigned to Bank 1. Collisions are not signaled in any way, because the user should be aware of what they plugged into the calculator.

The collision check reads the first memory location in the page, and if this location contains anything other than 0x000 the page is considered occupied. Note that when QROM is initialized (via **QRINI**) or cleared (via **QRCLR**) a 0x000 is written to all page locations, and this may confuse the collision check if QROM blocks are assigned to the same page/bank combination. This is why there is also a hardware collision check between pages of QROM. This hardware collision handling will be explained later in this section.

It is important to note that nearly all of the original software that uses Library-4, as well as Library-4 itself, assumes the presence of the 41-CX version of the Operating System. This means that these modules will only work when loaded into the HP-41 MAXX QROM if the HP-41 MAXX itself is inserted into an HP-41CX. Special versions of these modules that do not require the CX Operating System are also available.

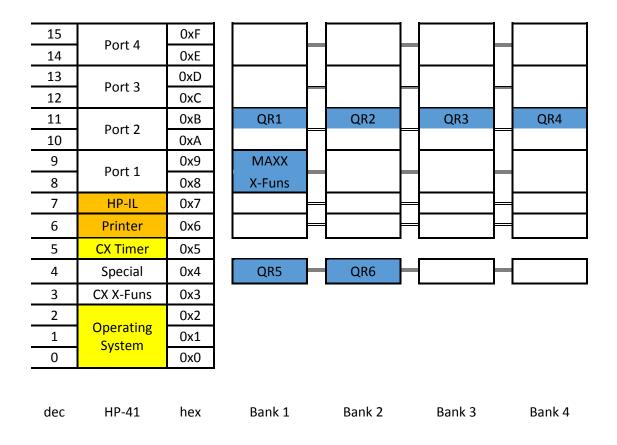

The figure below shows a simple case for the distribution of QROM blocks. In this example page 11 contains software that uses all four banks, and the fifth and sixth block of QROM are assigned to page 4, to hold library code for the 4-bank image. This still leaves six more blocks of QROM available.

The QROM programming for the figure above is as follows:

| 1 P:B:M-11:1:R | ; page 11, bank 1, read-only, active |

|----------------|--------------------------------------|

| 2 P:B:M-11:2:R | ; page 11, bank 2, read-only, active |

| 3 P:B:M-11:3:R | ; page 11, bank 3, read-only, active |

| 4 P:B:M-11:4:R | ; page 11, bank 4, read-only, active |

| 5 P:B:M- 4:1:R | ; page 4, bank 1, read-only, active  |

| 6 P:B:M- 4:2:R | ; page 4, bank 1, read-only, active  |

The figure below shows a slightly more complex case, this time with QROM blocks distributed across several different pages. Pages 11, 12, and 14 all contain code that uses two banks. The code in page 10 is not banked, so it must be programmed to ignore the state of the corresponding bank-control bits that are used by the image in page 11. The arrangement shown in Port 2 is what is used for the HP-41 Advantage Pac.

The QROM programming for the figure above is as follows:

| 1 : | P:B:M- 4:1:R | ; page 4, bank 1, read-only, active      |

|-----|--------------|------------------------------------------|

| 2   | P:B:M-10:0:R | ; page 10, not banked, read-only, active |

| 3   | P:B:M-11:1:R | ; page 11, bank 1, read-only, active     |

| 4   | P:B:M-11:2:R | ; page 11, bank 2, read-only, active     |

| 5   | P:B:M-12:1:R | ; page 12, bank 1, read-only, active     |

| 6   | P:B:M-12:2:R | ; page 12, bank 2, read-only, active     |

| 7   | P:B:M-14:1:R | ; page 14, bank 1, read-only, active     |

| 8   | P:B:M-14:2:R | ; page 14, bank 2, read-only, active     |

| 9   | P:B:M- 4:2:R | ; page 4, bank 2, read-only, active      |

This example highlights the fact that QROM blocks are completely independent, with QROM block 1 and QROM block 9 both assigned to page 4, but with different banks.

It is possible to assign QROM blocks to the same page and the same bank (as is the case after power-on) but hardware in the MAXX module automatically prioritizes accesses in these cases. This hardware priority requires some explanation, because it operates slightly differently for reads and writes.

In the case of reads, QROM blocks are prioritized from lowest number to highest number, with the lower number having the higher priority. This prioritization applies to QROM blocks assigned to the same page and bank, but only if reads are enabled. The example below shows several cases of this prioritization. In this example QROM block 2 will always be accessed when page 10 is read, independent of bank. QROM 1 would normally be higher priority, but it is not enabled for reads. QROMs 9 through 12 will never be read in this scenario because QROM 2 is programmed to be active for all banks in page 10.

| 1 P:B:M-10:0:W  | ; page 10, not banked, write-only, active |

|-----------------|-------------------------------------------|

| 2 P:B:M-10:0:R  | ; page 10, not banked, read-only, active  |

| 3 P:B:M-11:1:R  | ; page 11, bank 1, read-only, active      |

| 4 P:B:M-11:2:R  | ; page 11, bank 2, read-only, active      |

| 5 P:B:M-12:1:R  | ; page 12, bank 1, read-only, active      |

| 6 P:B:M-12:2:R  | ; page 12, bank 2, read-only, active      |

| 7 P:B:M-14:1:R  | ; page 14, bank 1, read-only, active      |

| 8 P:B:M-14:2:R  | ; page 14, bank 2, read-only, active      |

| 9 P:B:M-10:1:B  | ; page 10, bank 1, read-write, not active |

| 10 P:B:M-10:2:B | ; page 10, bank 2, read-write, not active |

| 11 P:B:M-10:3:B | ; page 10, bank 3, read-write, not active |

| 12 P:B:M-10:4:B | ; page 10, bank 4, read-write, not active |

Writes to QROM are prioritized slightly differently. The priority is still lowest number to highest number, but is broken into three sections. QROM 1-4 are in one section, QROM 5-8 are in a second section and QROM 9-12 are in the third section. The prioritization is done within each section in parallel. This was a conscious design decision, because it allows the QROM initialization function to run three times faster, by allowing three simultaneous initialization writes. This parallel write operation is only possible because each set of four QROM pages uses a separate FPGA memory instance. In the example above any write to page 10 will occur in QROM 1, with one of QROM 9-12 also being written, depending on the current bank.

### **MAXX Software Overview**

The MAXX software is located in the upper half of the Port where the MAXX module is inserted into the HP-41 calculator. The X-Functions software (if enabled) will be located in the lower half of this Port.

The MAXX software uses XROM 15, and this XROM number cannot be changed without breaking how a number of the functions in this module work. This XROM number is used by about twenty known modules, but nearly all of them are fairly obscure.

The MAXX software is divided into eight different groups, with most groups dedicated to a specific set of hardware features.

- The MAXX Status functions report the current state of the different hardware blocks in the module, grouped so that the information will fit into the HP-41 display.

- The Expanded Memory Block functions are useful when expanded memory is being used for backups or temporary storage. These functions move blocks of data between the four blocks of expanded memory.

- The Expanded Register functions treat expanded memory Block 1 as a set of 1024 expanded memory registers, with a full complement of register-oriented functions.

- The Expanded Register Block functions are analogous to similarly-named functions available for X-memory. All of these functions operate on a block of expanded registers.

- The QROM functions control the operation of the twelve 4kx10 blocks of read/write memory that are dedicated to supporting instruction memory. QROM blocks can be assigned to page addresses between 6 and 15 or to page 4.

- The Instruction Memory functions allow direct read and write of the entire instruction address space. Only the areas of the instruction address space that support write operations, and are enabled for writes, can actually be written.

- The Code Copy function provides a way to fill QROM blocks with code from another source, typically a physical module.

- The HP-IL Code Copy functions support copying of a full page of the instruction address space to or from HP-IL, using the HP-IL Module (82160A) connected to a mass storage device. Two different algorithms for packing instruction words into bytes for HP-IL transfer are available.

## **MAXX Status Functions**

The MAXX Status functions report the current state of the various pieces of hardware available in this module, grouped so that the information will fit into the HP-41 display. All of these functions return the status information to the display (in Run mode) as well as to the Alpha register.

#### MXST?

The **MXST?** (*MAXX Status?*) function returns the status of the different hardware blocks that are automatically enabled or disabled when the calculator is turned on.

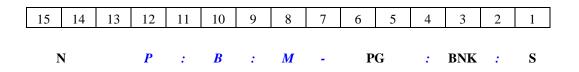

The figure below shows the formatting of the status returned in the Alpha register. The eight status identifiers (**S** in the figure) will be either E (indicating that the feature is enabled) or D (indicating that the feature is disabled.) Although this status requires sixteen locations in the Alpha register the entire status fits in the display, as shown below, because the colons do not require a separate digit in the display.

|    | ALPHA Register |    |    |    |    |    |   |   |   |   |   |   |   |   |   |

|----|----------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| 16 | 15             | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|    |                |    |    |    |    |    |   |   |   |   |   |   |   |   |   |

| T  | :              | X  | :  | M  | -  | S  | : | S | S | S | : | S | S | S | S |

Digit 10 reports the status for the Time module portion of the MAXX hardware.

Digits 8, 7 and 6 report the status for X-memory in 2-1-0 order. X-memory 2 corresponds to the second X-memory module in an HP-41. X-memory 1 corresponds to the first X-memory module in an HP-41. X-memory 0 corresponds to the memory in the X-Functions/Memory module.

Digits 4, 3, 2 and 1 report the status for main memory in 4-3-2-1 order. Each main memory module is numbered according to the Port where a physical module would reside.

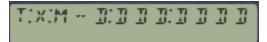

The figure below shows the formatting of the status returned in the display. This display shows that all of the MAXX hardware blocks are disabled.

#### QRST?

(Select in X-register)

The **QRST?** (*QROM Status?*) function returns the status of the selected block of QROM. The select in the X-register can range from 0 through 12. A select value of 0 selects a CAT-like operation that displays each block status one after the other.

The figure below shows the formatting of the status returned in the Alpha register. The status identifier **N** is the number (1 through 12) of the QROM block being reported. The status identifier **PG** is a decimal number (4 or 6 through 15) corresponding to the page address where this block of QROM resides. The status identifier **BNK** is a number ( $\theta$  through 4) that indicates the actual bank for this block of QROM. The status identifier **S** can be either **D** (indicating that this block of QROM is disabled), **W** (indicating that this block is enabled for reads only), **R** (indicating that this block is enabled for reads only), or **B** (indicating that this block is enabled for both reads and writes.)

Digits 15 and 14 show which block of QROM this report is for, which is also the input for this function. This number is right-justified in these two digit locations.

Digits 6 and 5 report the page address where this block of QROM has been assigned. This status is right-justified in these two digit locations.

Digit 3 reports which bank this block of QROM occupies. There are only five possibilities, as shown in the table below.

| Digit | Bank       |

|-------|------------|

| 0     | Not Banked |

| 1     | Bank 1     |

| 2     | Bank 2     |

| 3     | Bank 3     |

| 4     | Bank 4     |

Digit 1 reports the read/write status for this block of QROM.

The figure below shows the formatting of the status returned in the display. This display shows the status for block 1 of QROM, which is assigned to page 15 with banking disabled, and is disabled for both reads and writes. These are the defaults (for all twelve QROM blocks) when the MAXX module is first inserted.

During the catalog operation only the **R/S** and  $\leftarrow$  keys are available any any other key will be ignored. The **R/S** key will stop or resume the listing, and a quick double-press allows single-stepping through the listing. Backward single-step is not available. The  $\leftarrow$  key terminates the catalog operation.

## **Expanded Memory Block Functions**

The Expanded Memory Block functions are useful when Expanded memory is being used for backups or temporary storage. The three Expanded memory blocks are numbered 1, 2 and 3, while the normal HP-41 Data memory is numbered 0 for these functions. These functions operate properly on normal HP-41 Data memory independent of whether the memory is internal or external to the HP-41 MAXX module.

The HP-41 Data memory is divided into three regions: Status (STATUS), Register memory (REGISTER) and X-memory (XMEM), as shown below.

| omntv    | 0x3FF           |

|----------|-----------------|

| empty    | 0x3F0           |

|          | 0x3EF           |

| XMEM-2   |                 |

|          |                 |

|          | 0x301           |

| empty    | 0x300           |

| empty    | 0x2F0           |

|          | 0x2EF           |

| XMEM-1   |                 |

|          |                 |

|          | 0x201           |

| empty    | 0x200           |

|          | 0x1FF           |

| REGISTER |                 |

| NEOISTEN |                 |

|          | 0x0C0           |

| XMFM-0   | 0x0BF           |

|          | 0x040           |

| emntv    | 0x03F           |

| empty    | 0x010           |

| STATUS   | 0x00F           |

| 517105   | 0x000           |

|          | empty<br>XMEM-1 |

Data Memory The Status region (orange) consists of data addresses 0x000-0x03F, and contains the uservisible X, Y, Z, T and Last X registers along with the Alpha register and other registers used by the operating system. Only the lower sixteen registers are present in an HP-41, but all sixty-four registers are transferred by an ST Expanded Memory Block function.

The Register memory region (yellow) consists of the normal register and program memory of the HP-41, consisting of data addresses in the range 0x0C0-0x1FF. The MM Expanded Memory Block functions operate on this region, plus data addresses in the range 0x000-0x00F. These two blocks of register memory are the entire main memory of the HP-41.

| 1023 | empty      | 0x3FF |         |         |                       |

|------|------------|-------|---------|---------|-----------------------|

| 1008 | empty      | 0x3F0 |         |         |                       |

| 1007 |            | 0x3EF |         |         |                       |

|      | XMEM-2     |       |         |         |                       |

|      |            |       |         |         |                       |

| 769  |            | 0x301 |         |         |                       |

| 768  | empty      | 0x300 | XM      | XM      | XM                    |

| 752  | empty      | 0x2F0 |         |         |                       |

| 751  |            | 0x2EF |         |         |                       |

|      | XMEM-1     |       |         |         |                       |

|      |            |       |         |         |                       |

| 513  |            | 0x201 |         |         |                       |

| 512  | empty      | 0x200 |         |         |                       |

| 511  |            | 0x1FF |         |         |                       |

|      | REGISTER   |       | MM      | D 4 D 4 | <b>N</b> 4 <b>N</b> 4 |

|      | REGISTER   |       | IVIIVI  | MM      | MM                    |

| 192  |            | 0x0C0 |         |         |                       |

| 191  | XMEM-0     | 0x0BF | ХМ      | XM      | ХМ                    |

| 64   | XIVILIVI-0 | 0x040 | AIVI    |         |                       |

| 63   | ometu      | 0x03F |         |         |                       |

| 16   | empty      | 0x010 | ST      | ST      | ST                    |

| 15   | STATUS     | 0x00F | MM      | MM      | MM                    |

| 0    | 517105     | 0x000 |         |         |                       |

|      |            |       |         |         |                       |

|      | Main Mem   |       | Y-mem   | Y-mem   | Y-mem                 |

|      | (Block 0)  |       | Block 1 | Block 2 | Block 3               |

The X-memory region (green) consists of two disjoint sections of Data memory. The section consisting of data addresses 0x040-0x0BF is the memory normally contained in an

Extended Functions/Memory module, while the section consisting of data addresses 0x200-0x3FF is the memory normally contained in a pair of X-Memory modules. The XM Expanded Memory functions operate on this area of data memory.

All of the Expanded Memory Block functions that are programmable prompt for an Expanded memory block number in Run mode and take this number from the X-register in Program mode or when Single-Stepping. Note that because of a feature in the HP-41 operating system, these functions will also prompt for a block number when entered in a program, but then discard this block number. When the program is run or single-stepped the block number is taken from the X-register.

The one non-prompting function (**YM<>YM**) takes one block number from the X-register and the other block number from the Y-register.

| Region | Copy<br>Execution Time | Exchange<br>Execution Time | Clear<br>Execution Time |

|--------|------------------------|----------------------------|-------------------------|

| ST     | 0.3 S                  | 0.4 S                      | n/a                     |

| MM     | 1.5 S                  | 2.2 S                      | n/a                     |

| XM     | 3.0 S                  | 4.4 S                      | n/a                     |

| YM     | 4.8 S                  | 7.0 S                      | 1.2 S                   |

These functions take some amount of time to execute, as shown in the table below.

Several of the registers in the Status area are critical for HP-41 operation, and modifying these registers can easily lead to a Memory Lost condition. To help protect against this, those Expanded Memory functions that will affect the Status area require that an *OK* string be present in the Alpha register before the function will execute.

The functions that require this safeguard are: **ST**<>**YM**, **YM**>**ST**, **MM**<>**YM**, and **YM**>**MM**. In addition, the **YM**<>**YM** function also requires this safeguard if either the source or destination memory block is Expanded Memory block 0.

Whenever a function is executed that requires this safeguard the Alpha register is automatically cleared as an additional precaution against accidentally overwriting the Status area in the future.

#### ST>YM

(prompts for YM Block) OR (YM Block in X-register)

The **ST>YM** (*Copy Status to Expanded Memory*) function copies the Status section of the 41C Data memory (addresses 0x000-0x03F) to the corresponding locations in the selected block of Expanded memory.

#### ST<>YM

#### (prompts for YM Block) OR (YM Block in X-register)

The **ST<>YM** (*Exchange Status with Expanded Memory*) function exchanges the Status section of the 41C Data memory (addresses 0x000-0x03F) with the corresponding locations in the selected block of Expanded memory. This function requires the string *OK* to be present in the Alpha register as a form of verification.

#### YM>ST

#### (prompts for YM Block) OR (YM Block in X-register)

The **YM>ST** (*Copy Expanded Memory to Status*) function loads the Status section of the 41C Data memory (addresses 0x000-0x03F) from the corresponding locations in the selected block of Expanded memory. This function requires the string *OK* to be present in the Alpha register as a form of verification.

#### MM>YM

#### (prompts for YM Block) OR (YM Block in X-register)

The **MM>YM** (*Copy Main Memory to Expanded Memory*) function copies the Main memory section of the 41C Data memory (addresses 0x0C0-0x1FF) to the corresponding locations in the selected block of Expanded memory.

#### MM<>YM (prompts for YM Block) OR (YM Block in X-register)

The MM<>YM (*Exchange Main Memory with Expanded Memory*) function exchanges the Main memory section of the 41C Data memory (addresses 0x0C0-0x1FF) with the corresponding locations in the selected block of Expanded memory. This function requires the string *OK* to be present in the Alpha register as a form of verification.

#### YM>MM (prompts for YM Block) OR (YM Block in X-register)

The YM>MM (*Copy Expanded Memory to Main Memory*) function loads the Main memory section of the 41C Data memory (addresses 0x0C0-0x1FF) from the corresponding locations in the selected block of Expanded memory. This function requires the string *OK* to be present in the Alpha register as a form of verification.

#### (prompts for YM Block) OR (YM Block in X-register)

The XM>YM (*Copy Extended Memory to Expanded Memory*) function copies the X-memory section of the 41C Data memory (addresses 0x040-0x0BF and 0x200-0x3FF) to the corresponding locations in the selected block of Expanded memory.

| XM<> | ΥM |  |  |

|------|----|--|--|

#### (prompts for YM Block) OR (YM Block in X-register)

The XM<>YM (*Exchange Extended Memory with Expanded Memory*) function exchanges the X-memory section of the 41C Data memory (addresses 0x040-0x0BF and 0x200-0x3FF) with the corresponding locations in the selected block of Expanded memory. This function requires the string *OK* to be present in the Alpha register as a form of verification.

#### YM>XM

XM>YM

#### (prompts for YM Block) OR (YM Block in X-register)

The YM>XM (*Copy Expanded Memory to Extended Memory*) function loads the Xmemory section of the 41C Data memory (addresses 0x040-0x0BF and 0x200-0x3FF) from the corresponding locations in the selected block of Expanded memory. This function requires the string *OK* to be present in the Alpha register as a form of verification.

#### YM<>YM

#### (SRC in X-register, DST in Y-register)

The YM<>YM (*Exchange Expanded Memory with Expanded Memory*) function exchanges the entire contents of two Expanded memory blocks. If either the source or the destination is Block 0, which corresponds to the normal HP-41 data memory, the function requires the string *OK* to be present in the Alpha register as a form of verification.

#### YMCLR

(prompts for YM Block) OR (YM Block in X-register)

The **YMCLR** (*Clear Expanded Memory*) function writes zero to every location in the selected block of Expanded memory. For obvious reasons this function does not allow Block 0 (HP-41 data memory) to be cleared.

### **Expanded Register Functions**

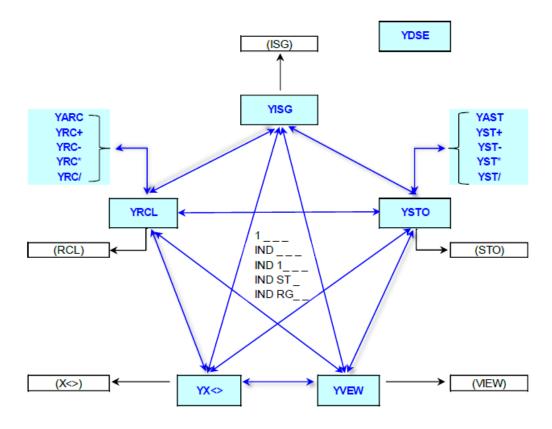

The Expanded Register functions treat Expanded memory Block 1 as a set of 1024 Expanded memory registers, with a full complement of register-oriented functions. These functions all prompt for a register number (000 to 1023) and also support indirect addressing, via expanded memory registers, normal registers, or the stack. All of these functions can be executed from the keyboard or entered in programs.

| 1023 | empty       | 0x3FF | 1023 |

|------|-------------|-------|------|

| 1008 | empty       | 0x3F0 |      |

| 1007 |             | 0x3EF |      |

|      | XM-2        |       |      |

|      | XIVI-2      |       |      |

| 769  |             | 0x301 |      |

| 768  | o no noti v | 0x300 |      |

| 752  | empty       | 0x2F0 |      |

| 751  |             | 0x2EF |      |

|      | XM-1        |       |      |

|      | XIVI-1      |       |      |

| 513  |             | 0x201 |      |

| 512  | empty       | 0x200 |      |

| 511  |             | 0x1FF |      |

|      | MAIN        |       |      |

|      | IVIAIIN     |       |      |

| 192  |             | 0x0C0 |      |

| 191  | XM-0        | 0x0BF |      |

| 64   | XIVI-U      | 0x040 |      |

| 63   | omntu       | 0x03F |      |

| 16   | empty       | 0x010 |      |

| 15   | STATUS      | 0x00F |      |

| 0    | STATUS      | 0x000 | 0    |

|      |             |       |      |

Main Mem (Block 0)

Y-registers

(Block 1)

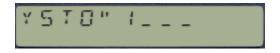

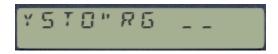

These function prompt for an expanded register number by displaying the function name, a quotation mark to remind the user that the function is not referring to regular registers, and three underscores as placeholders for the expanded register address. For example:

For all but one of these functions (the **YDSE** case) while these three underscores are displayed nearly the entire keyboard is available, allowing the user to move between functions, select indirect addressing or enter the expanded register address. Only the **USER**, **PRGM**, **XEQ** and **ENTER** keys are ignored in this case. The  $\leftarrow$  key terminates keyboard input and cancels the function.

The top two rows of keys provide a shortcut way to access expanded registers 001 through 010. The  $\Sigma$ + key enters 001, the 1/x key enters 002, and so on up to the **COS** key entering 009 and the **TAN** key entering 010. By providing three digits, these keys terminate keyboard entry and start the execution of the function.

The **STO** key changes the function to **YSTO** for most cases, even if indirect addressing has been selected. However, if the current function selection is **YSTO**, then this key switches to the regular **STO** function, and this transition is irreversible.

The **RCL** key changes the function to **YRCL** for most cases, even if indirect addressing has been selected. However, if the current function selection is **YRCL**, then this key switches to the regular **RCL** function, and this transition is irreversible.

The **SST** key changes the function to **YX**<> for most cases, even if indirect addressing has been selected. However, if the current function selection is **YX**<>, then this key switches to the regular **X**<> function, and this transition is irreversible. The **SST** key is used because the normal **X**<>**Y** key is in the second keyboard row and is dedicated to the numeric shortcut previously described.

The **CHS** key changes the function to **YISG** for most cases, even if indirect addressing has been selected. However, if the current function selection is **YISG** or **YDSE**, then this key switches to the regular **ISG** function, and this transition is irreversible. The fact that the normal **DSE** function is not available on the keyboard is why the **YDSE** function is treated slightly differently from all of the other expanded register functions as far as the keyboard operation.

The **R/S** key changes the function to **YVEW** for most cases, even if indirect addressing has been selected. However, if the current function selection is **YVEW**, then this key switches to the regular **VIEW** function, and this transition is irreversible.

The **ALPHA** key is active for the various store and recall functions (but not **YAST** or **YARC**) and is ignored in all other cases. Any store function will be changed to **YAST** and any recall function will be changed to **YARC**, even if indirect addressing has been selected.

The **EEX** key is used to create a four-digit expanded register address by prepending a **1** to the address field, as shown below. Once digit entry has begun only the numeric keys (and the  $\leftarrow$  key) are active. There are only 1024 expanded registers, so the next digit must be a 0, but this is not checked until all four digits have been entered.

The arithmetic keys (+, -, \* and ÷) will change the operation to add the selected arithmetic operation, for either store or recall. But the arithmetic keys are ignored for the **YISG**, **YDSE**, **YVEW** and **YX**<> functions. In addition, these keys will cancel the indirect addressing mode at the same time that the function is changed.

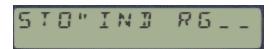

The gold **SHIFT** key changes the addressing for the function to indirect using an expanded register, as shown below. In this case the full keyboard continues to be available, and works as described here.

The radix key (.) can be used to modify the indirect addressing to use a stack register for the indirect address, as shown below.

Note that the display does not have enough room to display the entire function name in this case. The stack register is specified according to the Alpha key table below. Specifying anything other than a normal stack register (X, Y, Z, T) is not recommended for the casual user.

| Key | Stack register selection | Address |

|-----|--------------------------|---------|

| А   | Synthetic "a" register   | 0x00F   |

| В   | Synthetic "b" register   | 0x00E   |

| С   | Synthetic "c" register   | 0x00D   |

| D   | Synthetic "d" register   | 0x00C   |

| Е   | Synthetic "e" register   | 0x00B   |

| K   | Synthetic "k" register   | 0x00A   |

| L   | LASTX register           | 0x004   |

| М   | Synthetic "M" register   | 0x005   |

| Ν   | Synthetic "N" register   | 0x006   |

| 0   | Synthetic "O" register   | 0x007   |

| Р   | Synthetic "P" register   | 0x008   |

| Q   | Synthetic "Q" register   | 0x009   |

| Т   | T stack register         | 0x000   |

| Х   | X stack register         | 0x003   |

| Y   | Y stack register         | 0x002   |

| Z   | Z stack register         | 0x001   |

When Indirect addressing has been selected, pressing the radix key again changes the mode to Indirect Register, as shown below. In this case a regular register address (0 to 99) is used for the indirect address.

In either of these two cases the radix key will toggle between the two possibilities, while the  $\leftarrow$  key will return to the basic **YSTO** or **YRCL** function.

The radix key is active even when the **IND** indicator is not present, and allows operations on the entire range of stack registers.

| YST0"ST _ |  |

|-----------|--|

|-----------|--|

As before, pressing the radix key again will toggle the function to select a regular 41C register address, while the  $\leftarrow$  key will return to the basic **YSTO** or **YRCL** function.

The direct Stack and Data Register options are useful in Run mode but it doesn't make sense to use them in programs because the equivalent native 41C function requires less program space.

When entered in a Program these Expanded Register function cases will automatically be converted to the native 41C functions, as highlighted in the table below.

| Direct   | Indirect     | Data Register | Indirect Data Reg | Stack        | Indirect Stack |

|----------|--------------|---------------|-------------------|--------------|----------------|

| YSTO nnn | YSTO IND nnn | STO nn        | YSTO IND RG nn    | STO ST (nn)  | YSTO IND ST nn |

| YST+ nnn | YST+ IND nnn | ST+ nn        | YST+ IND RG nn    | ST+ ST (nn)  | YST+ IND ST nn |

| YST- nnn | YST- IND nnn | ST- nn        | YST- IND RG nn    | ST-ST (nn)   | YST- IND ST nn |

| YST* nnn | YST* IND nnn | ST* nn        | YST* IND RG nn    | ST* ST (nn)  | YST* IND ST nn |

| YST/ nnn | YST/ IND nnn | ST/ nn        | YST/ IND RG nn    | ST/ST (nn)   | YST/ IND ST nn |

| YRCL nnn | YRCL IND nnn | RCL nn        | YRCL IND RG nn    | RCL ST (nn)  | YRCL IND ST nn |

| YRC+ nnn | YRC+ IND nnn | YRC+ RG nn    | YRC+ IND RG nn    | YRC+ ST nn   | YRC+ IND ST nn |

| YRC- nnn | YRC- IND nnn | YRC- RG nn    | YRC- IND RG nn    | YRC- ST nn   | YRC- IND ST nn |

| YRC* nnn | YRC* IND nnn | YRC* RG nn    | YRC* IND RG nn    | YRC* ST nn   | YRC* IND ST nn |

| YRC/ nnn | YRC/ IND nnn | YRC/ RG nn    | YRC/ IND RG nn    | YRC/ ST nn   | YRC/ IND ST nn |

| YDSE nnn | YDSE IND nnn | DSE nn        | YDSE IND RG nn    | DSE ST (nn)  | YDSE IND ST nn |

| YISG nnn | YISG IND nnn | ISG nn        | YISG IND RG nn    | ISG ST (nn)  | YISG IND ST nn |

| YX<> nnn | YX<> IND nnn | X<> nn        | YX<> IND RG nn    | X<> ST (nn)  | YX<> IND ST nn |

| YVEW nnn | YVEW IND nnn | VIEW nn       | YVEW IND RG nn    | VIEW ST (nn) | YVEW IND ST nn |

| YARC nnn | YRCL IND nnn | ARCL nn       | YRCL IND RG nn    | ARCL ST (nn) | YRCL IND ST nn |

| YAST nnn | YSTO IND nnn | ASTO nn       | YSTO IND RG nn    | ASTO ST (nn) | YSTO IND ST nn |

In program mode the Expanded Register functions use two program lines, one for the function code and one for the Y-register number. In the case of Indirect, Register, Indirect Register, Stack and Indirect Stack, the register number is modified to indicate the special type of addressing. These modifications are shown in the table below. The modifications are managed automatically and these two program lines should not be modified by the user.

| Function | Direct | Indirect   | Data<br>Register | Indirect<br>Data Reg | Stack        | Indirect<br>Stack |

|----------|--------|------------|------------------|----------------------|--------------|-------------------|

| YSTO     | nnn    | nnn + 1024 | STO nn           | nn + 2048            | STO ST (nn)  | nn + 3072         |

| YST+     | nnn    | nnn + 1024 | ST+ nn           | nn + 2048            | ST+ ST (nn)  | nn + 3072         |

| YST-     | nnn    | nnn + 1024 | ST- nn           | nn + 2048            | ST-ST (nn)   | nn + 3072         |

| YST*     | nnn    | nnn + 1024 | ST* nn           | nn + 2048            | ST* ST (nn)  | nn + 3072         |

| YST/     | nnn    | nnn + 1024 | ST/ nn           | nn + 2048            | ST/ST (nn)   | nn + 3072         |

| YRCL     | nnn    | nnn + 1024 | RCL nn           | nn + 2048            | RCL ST (nn)  | nn + 3072         |

| YRC+     | nnn    | nnn + 1024 | nn + 2560        | nn + 2048            | YRC+ ST nn   | nn + 3072         |

| YRC-     | nnn    | nnn + 1024 | nn + 2560        | nn + 2048            | YRC- ST nn   | nn + 3072         |

| YRC*     | nnn    | nnn + 1024 | nn + 2560        | nn + 2048            | YRC* ST nn   | nn + 3072         |

| YRC/     | nnn    | nnn + 1024 | nn + 2560        | nn + 2048            | YRC/ ST nn   | nn + 3072         |

| YDSE     | nnn    | nnn + 1024 | DSE nn           | nn + 2048            | DSE ST (nn)  | nn + 3072         |

| YISG     | nnn    | nnn + 1024 | ISG nn           | nn + 2048            | ISG ST (nn)  | nn + 3072         |

| YX<>     | nnn    | nnn + 1024 | X<> nn           | nn + 2048            | X<> ST (nn)  | nn + 3072         |

| YVEW     | nnn    | nnn + 1024 | VIEW nn          | nn + 2048            | VIEW ST (nn) | nn + 3072         |

| YARC     | nnn    | nnn + 1024 | ARCL nn          | nn + 2048            | ARCL ST (nn) | nn + 3072         |

| YAST     | nnn    | nnn + 1024 | ASTO nn          | nn + 2048            | ASTO ST (nn) | nn + 3072         |

The remainder of this section describes the details of each individual Expanded Register function.

#### YARC

(prompts for YM register)

The **YARC** (*Expanded Register Alpha Recall*) function appends the contents of the selected expanded register to the Alpha register.

| YAST | (prompts for YM register) |

|------|---------------------------|

|      |                           |

The **YAST** (*Expanded Register Alpha Store*) function copies the first six characters in the Alpha register to the selected expanded register. The Alpha register is unaffected.

#### YDSE

**YISG**

(prompts for YM register)

The **YDSE** (*Expanded Register Decrement and Skip if Equal*) function operates identically to the normal HP-41C **DSE** function, except that it uses an expanded register.

#### (prompts for YM register)

The **YISG** (*Expanded Register Increment and Skip if Greater*) function operates identically to the normal HP-41C **ISG** function, except that it uses an expanded register.

| YRCL | (prompts for YM register)  |

|------|----------------------------|

|      | (prompts for finitegister) |

The **YRCL** (*Expanded Register Recall*) function copies the contents of the selected expanded register to the X-register. The stack is lifted and the expanded register is not affected.

#### YRC+

(prompts for YM register)

The **YRC+** (*Expanded Register Recall and Add*) function adds the contents of the selected expanded register to the contents of the X-register and places the result in the X-register. The stack is not lifted and the expanded register is unaffected.

(prompts for YM register)

The **YRC-** (*Expanded Register Recall and Subtract*) function subtracts the contents of the selected expanded register from the contents of the X-register and places the result in the X-register. The stack is not lifted and the expanded register is unaffected.

#### YRC\*

YRC-

(prompts for YM register)

The **YRC**\* (*Expanded Register Recall and Multiply*) function multiplies the contents of the selected expanded register with the contents of the X-register and places the result in the X-register. The stack is not lifted and the expanded register is unaffected.

#### YRC/

**YSTO**

YST+

YST-

YST\*

(prompts for YM register)

The **YRC***I* (*Expanded Register Recall and Divide*) function divides the contents of the X-register by the contents of the expanded register and places the result in the X-register. The stack is not lifted and the expanded register is unaffected.

(prompts for YM register)

The **YSTO** (*Expanded Register Store*) function copies the contents of the X-register to the selected expanded register. The X-register is not affected.

(prompts for YM register)

The **YST+** (*Expanded Register Add and Store*) function adds the contents of the X-register to the contents of the selected expanded register and stores the result in the expanded register. The X-register is unaffected.

(prompts for YM register)

The **YST-** (*Expanded Register Subtract and Store*) function subtracts the contents of the X-register from the contents of the selected expanded register and places the result in the expanded register. The X-register is unaffected.

(prompts for YM register)

The **YST**\* (*Expanded Register Multiply and Store*) function multiplies the contents of the selected expanded register by the contents of the X-register and places the result in the expanded register. The X-register is unaffected.

### YST/

(prompts for YM register)

The **YST**/ (*Expanded Register Divide and Store*) function divides the contents of the selected expanded register by the contents of the X-register and places the result in the expanded register. The X-register is unaffected.

#### **YVEW**

(prompts for YM register)

The **YVEW** (*View Expanded Register*) function recalls the contents of the selected expanded register to the display, just like the normal **VIEW** function.

#### YX<>

(prompts for YM register)

The **YX**<> (*Expanded Register Exchange with X*) function exchanges the contents of the selected expanded register with the contents of the X-register.

### **Expanded Register Block Functions**

The Expanded Register Block functions are analogous to similarly-named functions available for X-memory. All of these functions operate on a block of expanded registers.

#### YRGMOV

#### (control word in X-register)

The **YRGMOV** (*Expanded Register Block Move*) function moves the contents of one block of expanded registers to another block of expanded registers as specified by the *bbb.eeennn* control word in the X-register.

The *bbb* digits are the base address of the source expanded register block, in the range  $R_0$  through  $R_{999}$ . The *eee* digits are the base address destination expanded register block, again in the range  $R_0$  through  $R_{999}$ . The *nnn* digits are the number of registers to be copied. If *nnn* is zero a value of one used.

These two blocks can be overlapping, but only if *bbb* is greater than *eee*. This is because the transfers start at the highest address in the block and work downwards.

#### YRGSWP

(control word in X-register)

The **YRGSWP** (*Expanded Register Block Swap*) function exchanges the contents of one block of expanded registers with the contents of another block of expanded registers, as specified by the *bbb.eeennn* control word in the X-register.

The *bbb* digits are the base address of the first block of expanded registers, in the range  $R_0$  through  $R_{999}$ . The *eee* digits are the base address of the second block of expanded registers, again in the range  $R_0$  through  $R_{999}$ . *nnn* is the number of registers to be exchanged. If *nnn* is zero a value of one used.

These blocks can be overlapping, but only if *bbb* is greater than *eee*. This is because the exchanges start at the highest address in the block and work downwards.

#### CLYRG

The **CLYRG** (*Clear Expanded Register Block*) function writes zero to the entire set of expanded registers,  $R_0$  through  $R_{1023}$ .

#### CLYRGX

#### (control word in X-register)

The **CLYRGX** (*Clear Expanded Register Block by X*) function writes zeros to all of the expanded registers in the range  $R_{bbb}$  to  $R_{eee}$ , inclusive. The *bbb.eee* control word is taken from the X-register.

#### A<>YRG (prompts for base address) OR (base address in X-register)

The A<>YRG (*Exchange Alpha Register with Expanded Registers*) function exchanges the contents of the Alpha register (plus the Temporary Alpha scratch register) with five expanded registers starting at the base address.

In Run mode the function prompts for a three-digit expanded register address, with a leading **1** is entered via the **EEX** key. In Program mode or Single-stepping the base address is taken from the X-register. The base register can range from  $R_{000}$  through  $R_{1019}$ .

The table below shows the arrangement of the exchanged registers.

| Y-register         | Exchanged register      |                  |  |

|--------------------|-------------------------|------------------|--|

| I-legister         | A<>YRG                  | ST<>YRG          |  |

| R <sub>nnn+4</sub> | Alpha register 7-1      | T stack register |  |

| R <sub>nnn+3</sub> | Alpha register 14-8     | Z stack register |  |

| R <sub>nnn+2</sub> | Alpha register 21-15    | Y stack register |  |

| R <sub>nnn+1</sub> | Alpha register 28-22    | X stack register |  |

| R <sub>nnn</sub>   | Temporary Alpha scratch | L stack register |  |

#### ST<>YRG (prompts for base address) OR (base address in X-register)

The **ST<>YRG** (*Exchange Stack Registers with Expanded Registers*) function exchanges the contents of the stack registers with five expanded registers starting at the base address.

In Run mode the function prompts for a three-digit expanded register address, with a leading **1** is entered via the **EEX** key. In Program mode or Single-stepping the base address is taken from the X-register. The base register can range from  $R_{000}$  through  $R_{1019}$ .

The table under the A<>YRG function description shows the arrangement of the exchanged registers.

# **QROM Functions**

QROM consists of twelve 4kx10 blocks of read/write instruction memory. Each of these twelve blocks can be assigned to a separate page address/bank combination. QROM can be assigned to any page address between 6 and 15 or to page 4. Each QROM block can be assigned to Bank 1, 2, 3 or 4, or banked operation can be disabled for the block. Each QROM block can be enabled or disabled for reads and writes separately.

When the MAXX module is first inserted into the calculator all twelve QROM blocks are assigned to Page 15, with banked operation disabled. There is no conflict with this assignment, because all twelve QROM blocks are also disabled for both reads and writes at the same time.

QROM is normally under control of the user, but every time the calculator is turned on the physical Ports are checked for conflicts with the QROM page addresses. If a module is present coincident with a QROM page address, and the QROM block is enabled for bank 1 or banked operation is disabled, the QROM block will be automatically disabled for reads. QROM blocks are never automatically enabled for reads once the conflict is removed, so the user will need to do this.

The Port conflict check is done using the MAXX software polling point. Because the HP-41 checks for polling point code starting with Page 5 and working upward, this means that anything plugged into the HP-41 at a page address lower than that of the MAXX software will be accessed prior to the conflict check. As a result, users must disable any QROM pages with a conflicting page address lower than the MAXX module prior to plugging in a physical module. This applies mostly to the Printer and HP-IL modules, because they contain polling point code that will definitely conflict with a co-located QROM image.

When first enabling QROM pages for reads, it is important to enable the blocks in the correct order. For Banked images this means that Bank 1 should be enabled last, so that the other banks are present and ready for access when the main bank is enabled. For multipage images this means that the secondary pages should be enabled first and the primary page enabled last, for the same reason.

A QROM block that is being relocated from one page address to another page address should be disabled for reads before being moved. The page address modification operation is atomic, meaning that will be completed before there is a chance that the new addressing will be noticed by the calculator, but it is always better to be safe than sorry.

QROM blocks are implemented using RAM, and are not initialized at power-up. The random data in a QROM block will almost certainly crash the calculator if the QROM block is enabled for reads prior to being initialized or loaded with actual data.

The table below shows how the various functions affect the QROM control fields. Most of the QROM functions take the block number, in the range 1-12, from the X-register to select the QROM block to operate on. The X-register is not affected. This selection should not be confused with the HP-41 page/bank address that the QROM block is assigned to.

Global operation can be selected with a value of "0" in the X-register. Global operation applies the operation to all twelve QROM blocks at once.

| Function | Address | Bank | Write   | Read    | Global    |

|----------|---------|------|---------|---------|-----------|

|          |         |      | Enable  | Enable  | operation |

| QRABY    | Set     | Set  | -       | -       | no        |

| QRCLR    | -       | -    | -       | -       | no        |

| QRINI    | -       | -    | -       | -       | N/A       |

| QRRE     | -       | -    | -       | Set     | no        |

| QRRO     | -       | -    | Cleared | Set     | no        |

| QRRP     | -       | -    | -       | Cleared | yes       |

| QRRWE    | -       | -    | Set     | Set     | no        |

| QRRWD    | -       | -    | Cleared | Cleared | yes       |

| QRWE     | -       | -    | Set     | -       | yes       |

| QRWO     | -       | -    | Set     | Cleared | yes       |

| QRWP     | -       | -    | Cleared | -       | yes       |

#### QRABY

#### (Select in X-register; control word in Y-register)

The **QRABY** (*QROM Set Address/Bank by Y-register*) function programs the page/bank address for the selected block of QROM, using the *pp.b* control word in the Y stack register. Both the X-register and Y-register are unaffected.

The pp digits (or digit) are the page address for the selected block. QROM can be assigned to page address 4 or any page 6 through 15. The *b* digit is the bank to be occupied by the selected block and ranges from 0 to 4. The 0 case tells the control logic to ignore the bank select bits for this block of QROM.

This function only programs the page address and bank, so read or write enables must be programmed separately. This function does check whether or not the page address is already occupied, but only if unbanked or Bank 1 is selected. An error message will be generated in the case of an occupied page.

A QROM block that is being relocated from one page to another should be disabled for reads before being moved.

#### QRCLR

(Select in X-register)

The **QRCLR** (*QROM Clear*) function initializes the selected block (1 - 12) of QROM to all zeros, providing finer granularity than the **QRINI** function.

#### QRINI

The **QRINI** (*QROM Initialize*) function fills all twelve blocks of QROM with all zeros. This function should be executed when the HP-41 MAXX module is first inserted into the calculator because the QROM blocks power up containing random data.

This function requires about seven seconds to complete and the display is blank during execution.

#### QRRE

#### (Select in X-register)

The **QRRE** (*QROM Read Enable*) function enables reads for the selected block of QROM, which has the effect of inserting this block into the HP-41 address space. This function returns an error message if the page is already occupied. The write enable for the QROM block is not affected.

A QROM block must always be initialized in some way before reads of the block are enabled to prevent locking up the machine. The page address and bank used by the QROM block should also be initialized prior to enabling reads.

QRRO

(Select in X-register)

The **QRRO** (*QROM Read-Only*) function enables reads and disables writes for the selected block of QROM. With this combination the QROM acts like a normal read-only memory. This function returns an error message if the page is already occupied.

#### QRRP

(Select in X-register)

The **QRRP** (*QROM Read Protect*) function disables reads for the selected block of QROM, which has the effect of removing the memory block from the HP-41 address space

as far as instruction execution is concerned. The write enable for the memory block is unaffected, and the QROM block retains its contents. Reads are disabled by default.

**QRRWE**

**QRRWD**

The **QRRWE** (OROM Read and Write Enable) function enables both reads and writes for the selected block of QROM. With this combination the QROM acts like a normal randomaccess memory. This mode should be used when QROM blocks are being used as HEPAX memory. This function returns an error message if the page is already occupied.

The **QRRWD** (OROM Read and Write Disable) function disables both reads and writes for the selected block of QROM, which has the effect of completely removing the memory block from the HP-41 address space. The QROM block retains its contents.

**QRWE**

The **QRWE** (*QROM Write Enable*) function enables writes for the selected block of QROM. Since the QROM is part of the HP-41 instruction address space, writes are normally rare. The read enable for the selected block of QROM is not affected.

QRWO

The **QRWO** (*QROM Write-Only*) function enables writes and disables reads for the selected block of QROM. This combination is useful for when a page is being loaded with an image from HP-IL.

**QRWP**

(Select in X-register)

The **QRWP** (*QROM Write Protect*) function disables writes for the selected block of QROM. Since QROM is part of the HP-41 instruction address space, writes would normally be disabled. The read enable for the selected block of QROM is not affected.

(Select in X-register)

(Select in X-register)

(Select in X-register)

(Select in X-register)

# **Instruction Memory Functions**

The Instruction Memory functions support direct read and write of the entire instruction address space. Only the areas of the instruction address space that support write operations, and are enabled for writes, will actually be written, but the entire instruction address space can be read.

Two different methods for specifying the address and data are supported with these functions: hexadecimal in the ALPHA register and decimal in the X-register.

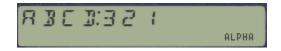

To use hexadecimal address and data the address and data must be present in the ALPHA register in a specific format. The figure below shows the formatting of the address and data fields in the ALPHA register. All seven hexadecimal digits must be present.

|           |           | A         | LPHA      | Regist | er        |           |           |

|-----------|-----------|-----------|-----------|--------|-----------|-----------|-----------|

| 8         | 7         | 6         | 5         | 4      | 3         | 2         | 1         |

|           |           |           |           |        |           |           |           |

| <b>A3</b> | <i>A2</i> | <b>A1</b> | <b>A0</b> | :      | <b>D2</b> | <b>D1</b> | <b>D0</b> |

Digits 8, 7, 6 and 5 contain the address to be read or written. Leading zeros must be present. Values can range from 0x0000 through 0xFFFF, inclusive.

Digit 4 must be a colon, used as a field separator.

Digits 3, 2 and 1 contains the read or write data. In the case of a read the data in these digits is ignored and replaced with the actual read data by the function. Leading zeros must be present. Values can range from 0x000 through 0x3FF, inclusive. The limited range is because instruction memory is only ten bits wide.

The figure below shows an example of address 0xABCD and data 0x321.

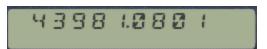

To use a decimal address and data the X-register is employed. The address field is to the left of the decimal point and the data field is to the right of the decimal point.

Leading zeros are not required for the address field, which can range from 0 through 65535, inclusive.

Leading zeros are required for the data field to make it four digits. The data field can range

from 0 through 1023, inclusive. Trailing zero digits can be omitted.

The figure below shows the decimal equivalent of the hexadecimal address/data pair shown above:

Converting between the two representations is supported by two dedicated functions, and manipulating the address or data is easy with the decimal representation.

#### AH>XD

(Address and Data in ALPHA)

The AH>XD (*Hex Address/Data to Decimal Address/Data*) function takes the properly formatted address and data in the ALPHA register and converts it to the equivalent decimal address and data in the X-register. The stack is lifted prior to writing the X-register and the ALPHA register is unaffected.

#### AHPEEK

(Address and Data in ALPHA)

The **AHPEEK** (*Instruction Memory Read using Hex Address/Data*) function reads the instruction memory specified by the address field in the ALPHA register and replaces the data field in the ALPHA register with the actual read data.

#### AHPOKE

(Address and Data in ALPHA)

The **AHPOKE** (*Instruction Memory Write using Hex Address/Data*) function writes the instruction memory specified by the address field in the ALPHA register with the data field in the ALPHA register. The ALPHA register is unaffected.

#### XD>AH

(Address and Data in X-register)

The **XD>AH** (*Decimal Address/Data to Hex Address/Data*) function takes the properly formatted address and data in the X-register and converts it to the equivalent hexadecimal address and data in the ALPHA register. The X-register is unaffected.

#### XDPEEK

#### (Address and Data in X-register)

The **XDPEEK** (*Instruction Memory Read using Decimal Address/Data*) function reads the instruction memory specified by the address field in the X-register and replaces the data field in the X-register with the actual read data.

#### **XDPOKE**

(Address and Data in X-register)

The **XDPOKE** (*Instruction Memory Write using Decimal Address/Data*) function writes the instruction memory specified by the address field in the X-register with the data field in the X-register. The X-register is unaffected.

# **Code Copy Function**

The Code Copy function provides a way to fill QROM pages with code from another source, usually a physical module.

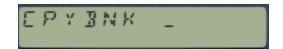

#### **CPYBNK**