8-bit Microprocessor Synthesizable Verilog HDL Model

**User Manual**

Y180-S i

#### **Disclaimer**

Systemyde International Corporation reserves the right to make changes at any time, without notice, to improve design or performance and provide the best product possible. Systemyde International Corporation makes no warrant for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make any commitment to update the information contained herein.

Systemyde International Corporation products are not authorized for use in life support devices or systems unless a specific written agreement pertaining to such use is executed between the manufacturer and the President of Systemyde International Corporation. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents, copyrights or other rights of third parties. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Systemyde International Corporation. All trademarks are trademarks of their respective companies.

Copyright 1995, 2006 Systemyde International Corporation Livermore, Ca. All rights reserved.

Systemyde International Corporation www. systemyde.com monted@systemyde.com

# **Revision History**

| Date       | Page(s)   | Description of revision                                                                                                                                                                 |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/11/2006 | 1 8       | Added two pages for this Revision History.  Corrected error in block diagram. Added FAULTB_ output, INTACKB_ output and deleted E_ output.  Corrected internal block-block connections. |

|            | 12        | Corrected typo in ED Page picture: IM 2 instruction.                                                                                                                                    |

| 10/15/2006 | 67-71     | Added Appendix 1, Single Event Upset Tolerance.                                                                                                                                         |

| 10/17/2006 | 72        | Added Appendix 2, Performance Estimates.                                                                                                                                                |

| 11/02/2006 | 67 - 76   | Expanded Appendix 1 to include simulation results, exit paths, etc. Added Appendix 3.                                                                                                   |

| 11/04/2006 | 70, 75-76 | Corrected page fault picture. Corrected tile count per final source code. Added to Appendix 3.                                                                                          |

| 01/31/2007 | 12        | Corrected mnemonic for ED-BB. Database corrections to flag control (flags being updated inappropriately).                                                                               |

| 07/16/2007 | n/a       | Database corrections to register write, alu control and flag control (interrupt acknowledge interfering with proper instruction execution).                                             |

| 03/17/2008 | n/a       | Database correction to Z flag operation (fix zero test to check both bytes for zero for word ADD, ADC and SBC instructions).                                                            |

| 07/10/2008 | n/a       | Database correction to flag operation (to s, z, and v unaffected with 16-bit add, c unaffected with byte inc and dec).                                                                  |

# **Table of Contents**

| 1 Introduction           |           | •        |          | •       |         |   |   | 6  |

|--------------------------|-----------|----------|----------|---------|---------|---|---|----|

| 2 Features               |           |          |          | •       |         |   |   | 7  |

| 3 Functional Description |           | •        | •        | •       |         |   |   | 8  |

| 3.1 Block Diagram        | ı.        | •        | •        | •       |         |   |   | 8  |

| 3.2 Register Descr       | ription   |          |          | •       |         |   |   | 9  |

| 3.3 Flags Descript       | ion .     |          |          | •       |         |   |   | 10 |

| 3.4 Instruction Ma       | ps .      |          |          | •       |         |   |   | 11 |

| 3.4.1 Main               | Code pa   | ge.      |          | •       |         |   |   | 11 |

| 3.4.2 ED C               | ode page  | · .      |          |         |         |   |   | 12 |

| 3.4.3 DD C               | Code page | e .      |          | •       |         |   |   | 13 |

| 3.4.4 FD C               | ode page  | · .      | •        | •       |         |   |   | 14 |

| 3.4.5 CB C               | ode page  | · .      |          | •       |         |   |   | 15 |

| 3.4.6 DD-C               | CB Code   | page     |          | •       |         |   |   | 16 |

| 3.4.7 FD-C               | B Code    | page     | •        | •       |         |   |   | 17 |

| 3.5 Execution Tab        | les .     |          | •        |         |         |   | • | 18 |

| 3.5.1 Exect              | ution Tab | ole conv | ention   | s .     |         |   |   | 18 |

| 3.5.2 Instru             | iction Op | code, T  | iming    | and Ope | eration |   |   | 19 |

| 3.5.3 Addr               |           |          |          |         |         |   |   | 23 |

| 3.5.4 Next               | Machine   | State    |          | •       |         |   |   | 27 |

| 4 Pin Descriptions .     |           |          |          | •       |         |   |   | 32 |

| 4.1 A_[ 15:0] (Add       | dress Bus | s) .     |          | •       |         |   |   | 33 |

| 4.2 AOEB_ (Addr          |           | *        | ole).    | •       |         |   |   | 33 |

| 4.3 BUSACKB_ (           | -         |          |          | •       |         |   |   | 33 |

| 4.4 BUSREQB_(l           |           | 7        |          | •       |         |   |   | 33 |

| 4.5 CLEARB_ (M           | _         |          |          |         |         |   |   | 33 |

| 4.6 CLK_ (Clock)         |           | *        |          |         |         |   |   | 34 |

| 4.7 CLKB_ (Clock         |           |          |          |         |         |   |   | 34 |

| 4.8 COEB_ (Contr         | ,         | ıt Enabl | e) .     |         |         |   |   | 34 |

| 4.9 DIN_[7:0] (Da        | -         |          |          |         |         |   |   | 34 |

| 4.10 DOEB_ (Data         |           |          | ) .      |         |         |   | _ | 33 |

| 4.11 DOUT_[7:0]          | -         |          |          |         |         |   |   | 35 |

| 4.12 FAULTB_ (F          |           | -        |          |         |         |   |   | 35 |

| 4.13 HALTB_ (Ha          |           | ,        |          |         |         |   | _ | 35 |

| 4.14 INTACKB_ (          |           |          | wledge   | e) .    |         |   |   | 35 |

| 4.15 INTB_ (Inter        |           |          |          |         |         |   | • | 35 |

| 4.16 IOCB (I/O C         |           | ,        |          |         |         |   | • | 36 |

| 4.17 IORQB_ (I/O         |           | ,        |          |         |         | Ī |   | 36 |

| 4.18 M1B_ (Mach          | -         | ,        |          |         |         |   | • | 36 |

| 4.19 M1E_ (Mach          | •         |          | hle)     | •       | •       | • | • | 36 |

| 4.20 MREQB_ (M           | •         |          |          | •       | •       | • | • | 36 |

| 4.21 NMIB_ (Non          | •         |          |          | anest)  | •       | • | • | 37 |

| 4.22 RDB_ (Read)         |           |          | i apt ix | quest)  | •       | • | • | 37 |

| 4.23 RESETB_ (N          |           | set)     | •        | •       | •       | • | • | 37 |

| 4.24 SLPB (Sleet         |           |          | •        | •       | •       | • | • | 37 |

# **Table of Contents (continued)**

|         | 4.25 ST_ (Status)                        |         |         |       | • | 38      |

|---------|------------------------------------------|---------|---------|-------|---|---------|

|         | 4.26 TRAPB_ (Trap)                       |         |         |       | • | 38      |

|         | 4.27 WAITB_ (Wait Request) .             |         |         |       | • | 38      |

|         | 4.28 WRB_ (Write)                        |         |         |       |   | 38      |

| 5 Bus ( |                                          |         |         |       |   | 39      |

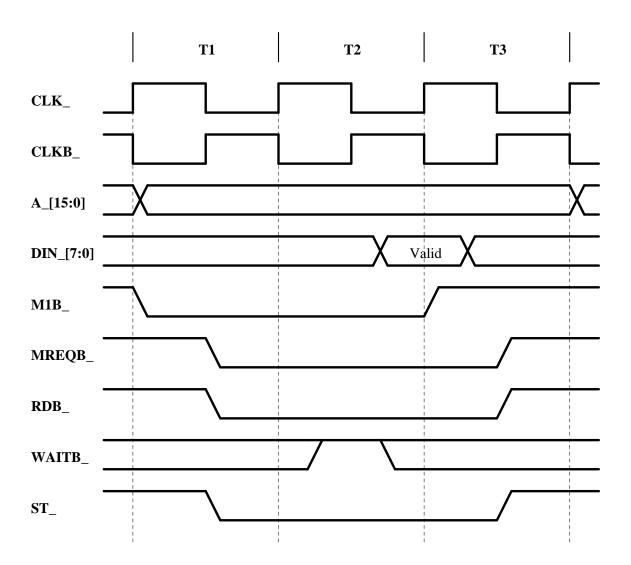

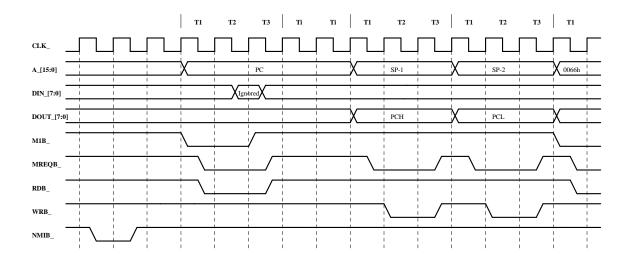

|         | 5.1 Instruction Fetch (without Wait stat | e) .    |         |       |   | 39      |

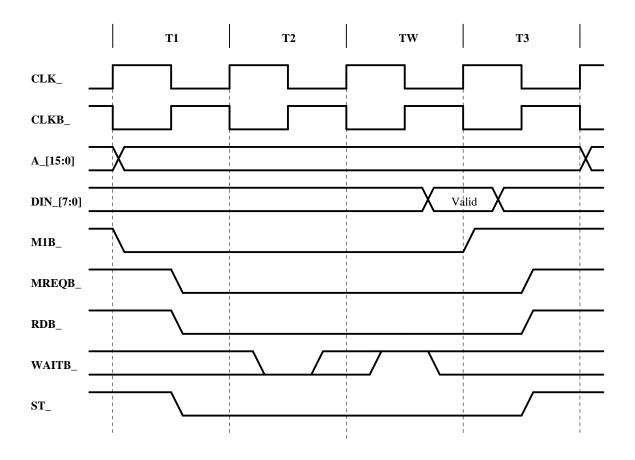

|         | 5.2 Instruction Fetch (with Wait state)  | · .     |         |       |   | 40      |

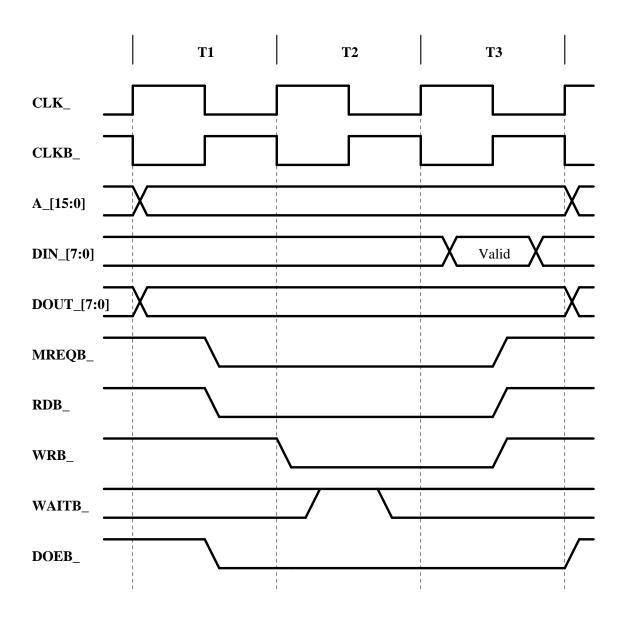

|         | 5.3 Memory Read/Write (without Wait      | state)  |         |       |   | 41      |

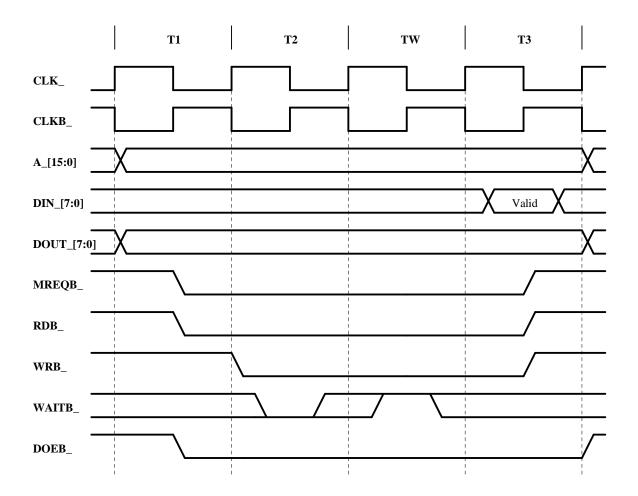

|         | 5.4 Memory Read/Write (with Wait star    |         |         |       |   | 42      |

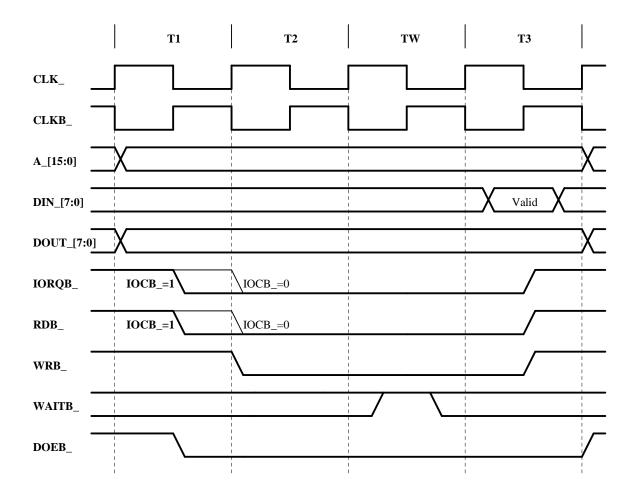

|         | 5.5 I/O Read/Write (without Wait state)  |         |         |       |   | 43      |

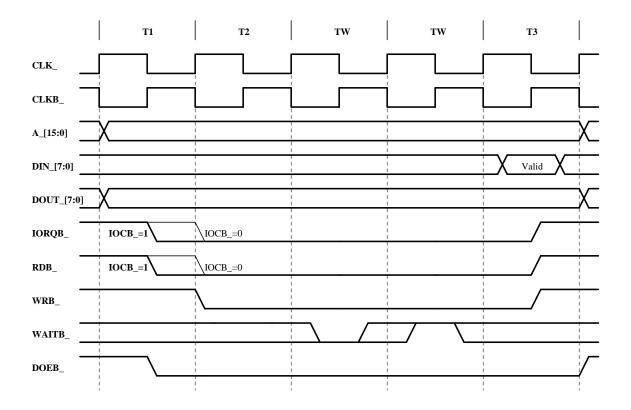

|         | 5.6 I/O Read/Write (with Wait state).    |         |         |       |   | 44      |

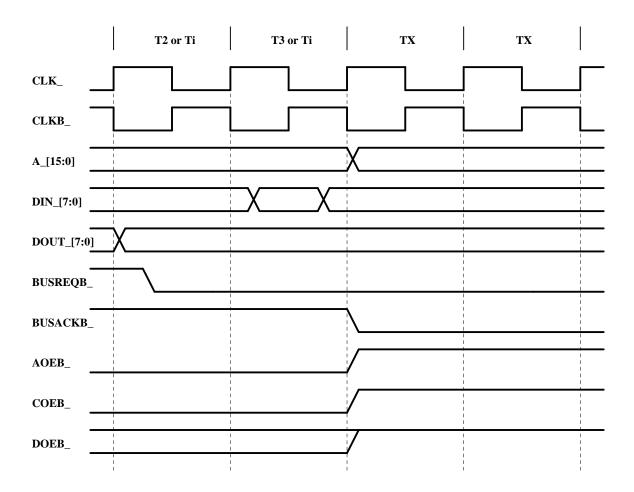

|         | 5.7 Bus Request/Acknowledge (Entry)      |         |         |       |   | 45      |

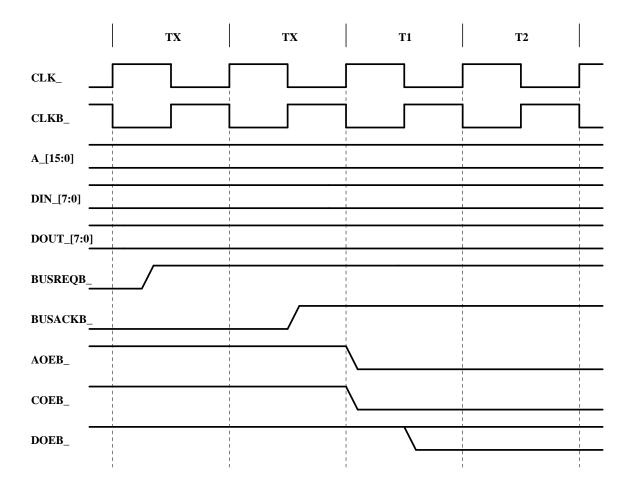

|         | 5.8 Bus Request/Acknowledge (Exit).      |         |         |       |   | 46      |

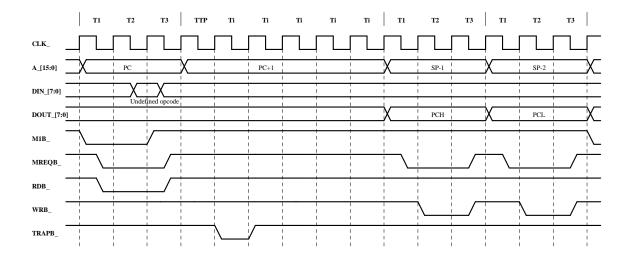

|         | 5.9 Trap (Second Opcode)                 |         |         |       |   | 47      |

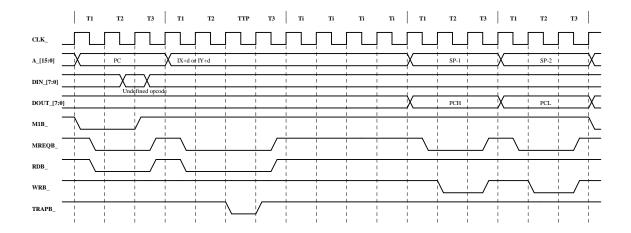

|         | 5.10 Trap (Third Opcode)                 |         |         |       |   | 48      |

|         | 5.11 Non-Maskable Interrupt Acknowle     | edge .  |         |       |   | 49      |

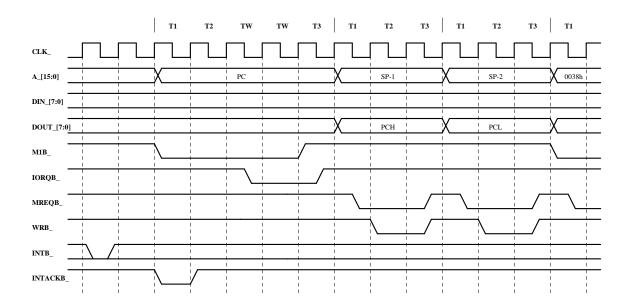

|         | 5.12 Mode 1 Interrupt Acknowledge .      |         | ,       |       |   | 50      |

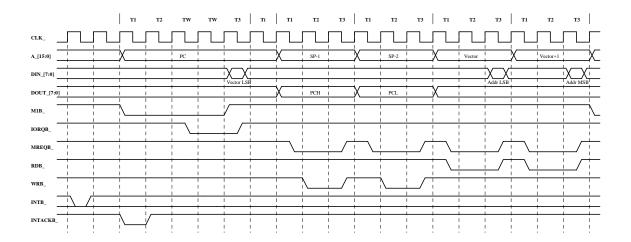

|         | 5.13 Mode 2 Interrupt Acknowledge .      |         |         |       |   | 51      |

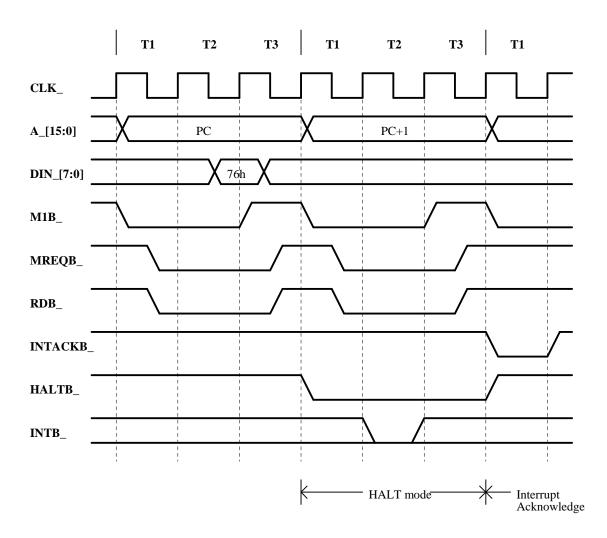

|         | 5.14 Halt (Entry and Exit)               |         |         |       |   | 52      |

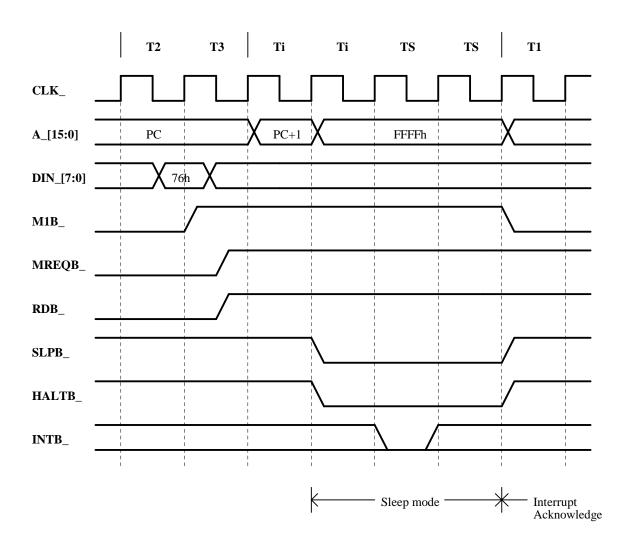

|         | 5.15 Sleep (Entry and Exit)              |         |         |       |   | 53      |

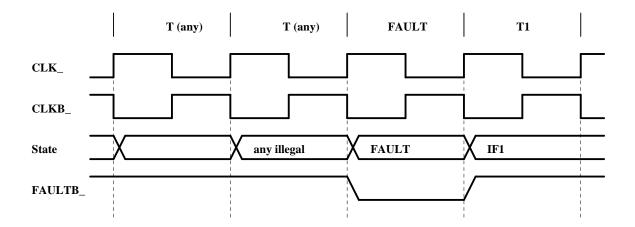

|         | 5.16 Fault Detect                        |         |         |       |   | 54      |

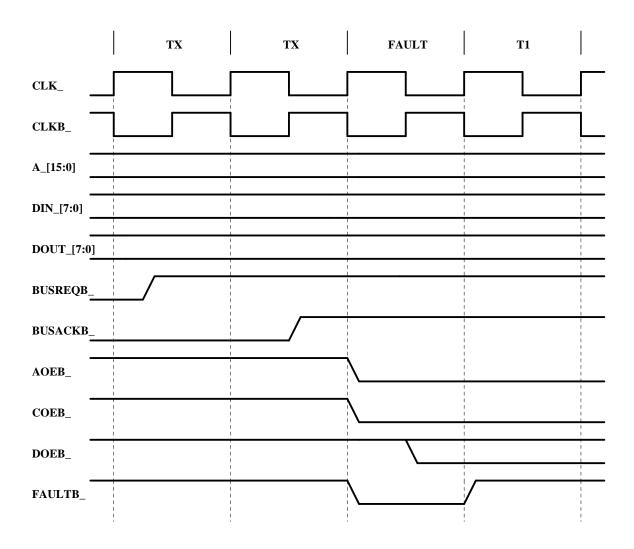

|         | 5.17 Fault Detect (during Bus Release)   |         |         |       |   | 55      |

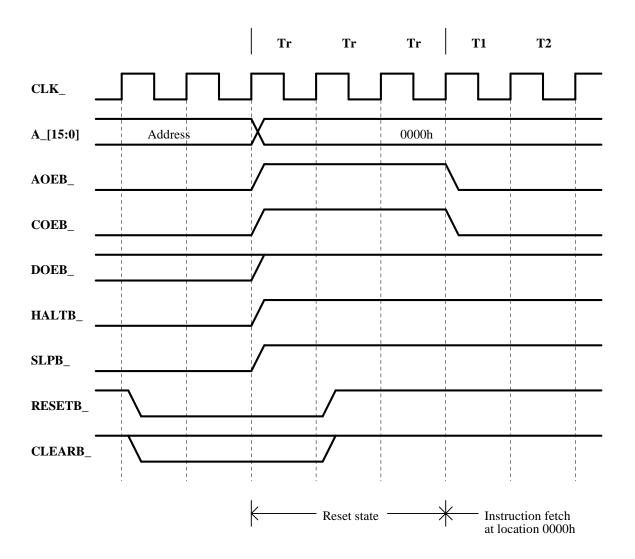

|         | 5.18 Reset and Clear                     |         |         |       |   | 56      |

| 6 Diffe | erences                                  |         |         |       |   | 57      |

|         | el Organization                          |         |         |       |   | 59      |

| , 1,100 | 7.1 Y180_TOP (Top Level Module) .        |         |         |       |   | 59      |

|         | 7.2 PARAMS (Parameter Definition `ind    | clude l | File)   |       |   | 59      |

|         | 7.3 IO_CTRL (I/O Interface Module)       |         |         |       |   | 60      |

|         | 7.4 M_STATE (Machine State Module)       |         |         |       |   | 60      |

|         | 7.5 CTR_CTL (Central Control Module      |         |         |       |   | 60      |

|         | 7.6 DATA_IO (Address and Data Model      |         | '       | •     |   | 60      |

|         | 7.7 REG_BYTE (Byte-wide Register in      |         | egister | File) |   | 60      |

|         | 7.8 REG_8BIT (Byte-wide General-Pur      |         | _       |       |   | 61      |

| 8 Test  |                                          | pose    | registe | • /   |   | 62      |

| 0 1050  | 8.1 TOP_LEV (Top Level for Simulation    | on)     |         | •     |   | 62      |

|         | 8.2 SETUP_HL (Initialization Pattern)    | 011)    |         | •     |   | 62      |

|         | 8.3 INT_OPS (Interrupt Operation) .      | •       | '       | •     |   | 63      |

|         | 8.4 ALU_OPS (ALU Operation) .            | •       |         | •     |   | 63      |

|         | 8.5 DAT_MOV (Data Movement Opera         | ation)  |         | •     |   | 63      |

|         | 8.6 TRP_2ND (Trap on Second Byte O       | ,       | on)     | •     |   | 63      |

|         | 8.7 TRP_3RD (Trap on Third Byte Ope      | •       | ,       | •     |   | 63      |

|         | 8.8 BIT_OPS (Bit Manipulation Operat     |         |         | •     |   | 63      |

|         | 8.9 JMP_OPS (Jump Operation) .           | 1011)   |         | •     |   | 64      |

|         | 8.8 IO OPS (I/O Operation) .             | •       |         |       |   | 64      |

|         | 0.0 10 (71 D (1/Q) (71)C(AUQII)          |         |         |       |   | $\cdot$ |

# **Table of Contents (continued)**

| 9 Installation                             | • |   | 65 |

|--------------------------------------------|---|---|----|

| 9.1 File Structure                         |   |   | 65 |

| Appendix 1: Single Event Upset Tolerance . |   | • | 66 |

| A1.1 User-controlled Registers .           |   |   | 66 |

| A1.2 Continuously-clocked Flip-flops       |   |   | 68 |

| A1.3 State machines                        |   |   | 69 |

| A1.3.1 fetch_hld state machine             |   |   | 69 |

| A1.3.2 inta_hld state machine.             |   | • | 70 |

| A1.3.3 clock_cyc state machine             |   | • | 70 |

| A1.3.4 page_reg state machine              |   | • | 70 |

| A1.3.5 mach_cyc state machine              |   | • | 72 |

| Appendix 2: Performance Estimates          |   |   | 74 |

| A2.1 Clock Frequency                       |   | • | 74 |

| A2.2 Instruction Frequency                 |   | • | 74 |

| A2.3 Gate Count                            |   |   | 75 |

| Appendix 3: Implementation Comments .      |   |   | 76 |

#### 1 Introduction

The Y180 is a synthesizable Verilog HDL model of the Z80180 CPU. It is software and hardware compatible with the Z80180 CPU and is software compatible with several other industry-standard processors. The Y180 is an original design, based on publicly available documentation, that employs design techniques suitable for a technology-independent implementation. It is a fully synchronous design that does not use 3-state busses. The design is structured in a way that allows its use either with or without modification by the customer. The combinatorial logic portions of the design may be implemented in either random logic or as a PLA, and control signals are treated symbolically in the design to allow either encoded or unencoded implementations (the default is encoded). The Y180 is accompanied by full design documentation, in the form of a large spreadsheet, which describes nearly every facet of the internal operation of the processor. This provides knowledgeable users the opportunity to customize the design for unique application requirements.

The Y180 is a powerful medium-performance processor that executes 181 instructions and includes an undefined opcode trap for illegal opcodes. The device contains a full complement of 8-bit arithmetic and logical instructions, and enough 16-bit instructions to properly handle the 16-bit address range. Included are bit manipulation instructions as well as an 8x8 multiply instruction. The device allows for other bus masters and includes a powerful vectored interrupt capability. The Y180 can be easily integrated with RAM, ROM or other application-specific logic to create a single-chip product. The technology-independent nature of the design provides the full spectrum of design alternatives relative to cost, power consumption and speed.

The Y180 is written in Verilog HDL and can be synthesized using any Verilog-compatible logic synthesizer. The Y180 package includes full design documentation, including a Verilog simulation and test suite.

#### 2 Features

- \* Fully functional synthesizable Verilog HDL model of the Z80180 CPU

- \* Vendor and technology independent

- \* Software compatible with several industry-standard processors

- \* 181 Instructions, plus an undefined opcode trap

- \* Eight addressing modes

- \* 64K byte addressing capability

- \* 8 bit ALU with bit, byte and BCD operations

- \* 8x8 multiply instruction

- \* Powerful vectored interrupt capability

- \* Static, fully synchronous design

- \* Designed without 3-state busses

- \* Easily modified external interface

- \* Fully decoded state machines, with illegal state detection

- \* Full design documentation included

- \* Verilog simulation and test suite included

#### 3 Functional Description

The Y180 is a general-purpose 8-bit microprocessor that is compatible with the Zilog Z80180 CPU. The device contains an 8-bit ALU, numerous 8- and 16-bit registers, a 64K byte addressing range, and a powerful vectored interrupt capability. The device executes 181 instructions, and performs an undefined opcode trap on all illegal instructions. The Y180 is completely software compatible with several industry-standard processors.

The Y180 is designed without using 3-state buses internally for maximum technology independence, and is a static, fully synchronous design. The Y180 is supplied in the form of a synthesizable Verilog HDL model, which is independent of technology, clock speed (within the limits of the chosen technology), and vendor.

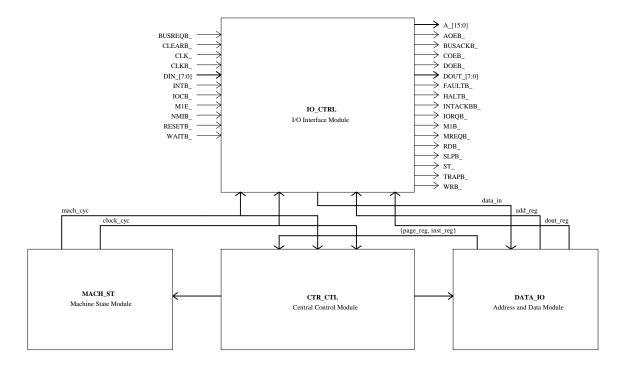

### 3.1 Block Diagram

The figure below shows a simplified block diagram of the Y180, organized in the same fashion as the Verilog HDL model is organized. The I/O Interface Module controls all of the pins of the Y180, and translates the internal busses and signals into the externally visible pins. The Machine State Module contains the machine cycle and clock cycle state machines, which control the sequence and timing of everything that happens within the Y180. The Central Control Module decodes the instruction and state information to generate all of the internal control signals. And the Address and Data Module contains the actual address and data manipulation portions of the Y180, including the ALU, the register file, and the various busses and special purpose registers.

### 3.2 Register Description

The figure below shows the registers contained in the Y180 that are visible to the programmer. The main registers have both a primary and an alternate version. The primary register set consists of A, F, B, C, D, E, H, and L, while the alternate register set consists of A', F', B', C', D', E', H', and L'. At any given time only one bank is active, and care must be used when switching between banks, as there is no way for the programmer to check which bank is active. The accumulator, A, is the destination for all 8-bit arithmetic and logic operations, while the Flag register F contains the flag results of arithmetic and logic operations. The other general-purpose registers can be paired, BC or DE or HL, to form 16-bit registers. There are two index registers, IX and IY, used for indexed addressing mode. The I register holds the upper eight bits of the interrupt vector table address for use in Interrupt Mode 2. The R register is left over from the original Z80 architecture, where it was used to hold a refresh address for DRAMs. In the Y180 it is just another general purpose register. The Stack pointer, SP, holds the address of the stack, and the Program Counter, PC, holds the address of the currently executing instruction.

| A  | F          |    |

|----|------------|----|

| В  | C          |    |

| D  | E          | M  |

| H  | L          |    |

| Γ  | X          |    |

| Г  | Y          |    |

|    |            | •  |

| A' | F'         |    |

| В' | C'         | Al |

| D' | <b>E</b> ' |    |

| Н' | L'         |    |

|    |            | •  |

|    |            | •  |

Main Register Bank

| , | C'         | Alternate Register Bank |

|---|------------|-------------------------|

| • | <b>E</b> ' |                         |

| I | R |

|---|---|

|   |   |

| SP |

|----|

| PC |

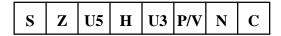

### 3.3 Flags Description

The figure below shows the flags contained in the F register, which report the results of instruction execution.

- S (Sign) The Sign flag stores the most significant bit of the result. This is used with signed arithmetic, where the MSB is zero for positive numbers and one for negative numbers.

- Z (Zero) The Zero flag is set to one if the result of the operation is 0.

- U5 (User) This is a user-defined flag. It is difficult to use however, because the only way to access it is to Push the AF register pair onto the stack and then Pop it back into some other register pair before testing the bit.

- H (Half-Carry) The Half-Carry flag is used only by the DAA (Decimal Adjust Accumulator) instruction to properly adjust the result of an arithmetic operation on BCD numbers.

- U3 (User) This is a user-defined flag. It is difficult to use however, because the only way to access it is to Push the AF register pair onto the stack and then Pop it back into some other register pair before testing the bit.

- P/V (Parity/Overflow) The Parity/Overflow flag reports the parity of the result for logical operations, with the flag set to one if the result has even parity and zero if the result has odd parity. This bit reports the overflow status of arithmetic operations. Overflow occurs when the two operands have the same sign but the sign of the result is different. This means that the actual result cannot be represented in the eight or sixteen bits allocated for the result.

- N (Negative) The Negative flag records the type of the last arithmetic operation (add or subtract) for use with the DAA instruction. The bit is set to one for subtract operations and set to zero for add operations.

- C (Carry) The Carry flag is set to one whenever there is a carry or borrow from the most significant bit of the result of an arithmetic operation. This is useful for implementing multiple precision arithmetic in software.

### 3.4 Instruction Maps

The following sections contain the opcode maps for the Y180. The most significant nibble is indexed vertically in the tables, while the least-significant nibble is indexed horizontally in the tables. Shaded opcodes are invalid and attempted execution of these opcodes will result in a Trap. In these maps, d is an 8-bit signed displacement, e is an 8-bit signed relative address, n is an 8-bit constant, and mn is a 16-bit constant.

### 3.4.1 Main Code Page

This table shows the main code page for the Y180. These instructions are all one byte long unless they contain immediate data or addresses. The four bytes marked as esc (for escape) are the first byte of multi-byte instructions, which are shown in subsequent tables.

| \LSB<br>MSB\ | 0            | 1            | 2             | 3             | 4             | 5            | 6             | 7            | 8            | 9            | Α             | В           | С             | D          | E             | F          |

|--------------|--------------|--------------|---------------|---------------|---------------|--------------|---------------|--------------|--------------|--------------|---------------|-------------|---------------|------------|---------------|------------|

| 0            | NOP          | LD<br>BC,mn  | LD<br>(BC),A  | INC<br>BC     | INC<br>B      | DEC<br>B     | LD<br>B,n     | RLCA         | EX<br>AF,AF' | ADD<br>HL,BC | LD<br>A,(BC)  | DEC<br>BC   | INC<br>C      | DEC<br>C   | LD<br>C,n     | RRCA       |

| 1            | DJNZ<br>e    | LD<br>DE,mn  | LD<br>(DE),A  | INC<br>DE     | INC<br>D      | DEC<br>D     | LD<br>D,n     | RLA          | JR<br>e      | ADD<br>HL,DE | LD<br>A,(DE)  | DEC<br>DE   | INC<br>E      | DEC<br>E   | LD<br>E,n     | RRA        |

| 2            | JR<br>NZ,e   | LD<br>HL,mn  | LD<br>(mn),HL | INC<br>HL     | INC<br>H      | DEC<br>H     | LD<br>H,n     | DAA          | JR<br>Z,e    | ADD<br>HL,HL | LD<br>HL,(mn) | DEC<br>HL   | INC<br>L      | DEC<br>L   | LD<br>L,n     | CPL        |

| 3            | JR<br>NC,e   | LD<br>SP,mn  | LD<br>(mn),A  | INC<br>SP     | INC<br>(HL)   | DEC<br>(HL)  | LD<br>(HL),n  | SCF          | JR<br>C,e    | ADD<br>HL,SP | LD<br>A,(mn)  | DEC<br>SP   | INC<br>A      | DEC<br>A   | LD<br>A,n     | CCF        |

| 4            | LD<br>B,B    | LD<br>B,C    | LD<br>B,D     | LD<br>B,E     | LD<br>B,H     | LD<br>B,L    | LD<br>B,(HL)  | LD<br>B,A    | LD<br>C,B    | LD<br>C,C    | LD<br>C,D     | LD<br>C,E   | LD<br>C,H     | LD<br>C,L  | LD<br>C,(HL)  | LD<br>C,A  |

| 5            | LD<br>D,B    | LD<br>D,C    | LD<br>D,D     | LD<br>D,E     | LD<br>D,H     | LD<br>D,L    | LD<br>D,(HL)  | LD<br>D,A    | LD<br>E,B    | LD<br>E,C    | LD<br>E,D     | LD<br>E,E   | LD<br>E,H     | LD<br>E,L  | LD<br>E,(HL)  | LD<br>E,A  |

| 6            | LD<br>H,B    | LD<br>H,C    | LD<br>H,D     | LD<br>H,E     | LD<br>H,H     | LD<br>H,L    | LD<br>H,(HL)  | LD<br>H,A    | LD<br>L,B    | LD<br>L,C    | LD<br>L,D     | LD<br>L,E   | LD<br>L,H     | LD<br>L,L  | LD<br>L,(HL)  | LD<br>L,A  |

| 7            | LD<br>(HL),B | LD<br>(HL),C | LD<br>(HL),D  | LD<br>(HL),E  | LD<br>(HL),H  | LD<br>(HL),L | HALT          | LD<br>(HL),A | LD<br>A,B    | LD<br>A,C    | LD<br>A,D     | LD<br>A,E   | LD<br>A,H     | LD<br>A,L  | LD<br>A,(HL)  | LD<br>A,A  |

| 8            | ADD<br>A,B   | ADD<br>A,C   | ADD<br>A,D    | ADD<br>A,E    | ADD<br>A,H    | ADD<br>A,L   | ADD<br>A,(HL) | ADD<br>A,A   | ADC<br>A,B   | ADC<br>A,C   | ADC<br>A,D    | ADC<br>A,E  | ADC<br>A,H    | ADC<br>A,L | ADC<br>A,(HL) | ADC<br>A,A |

| 9            | SUB<br>B     | SUB<br>C     | SUB<br>D      | SUB<br>E      | SUB<br>H      | SUB<br>L     | SUB<br>(HL)   | SUB<br>A     | SBC<br>A,B   | SBC<br>A,C   | SBC<br>A,D    | SBC<br>A,E  | SBC<br>A,H    | SBC<br>A,L | SBC<br>A,(HL) | SBC<br>A,A |

| Α            | AND<br>B     | AND<br>C     | AND<br>D      | AND<br>E      | AND<br>H      | AND<br>L     | AND<br>(HL)   | AND<br>A     | XOR<br>B     | XOR<br>C     | XOR<br>D      | XOR<br>E    | XOR<br>H      | XOR<br>L   | XOR<br>(HL)   | XOR<br>A   |

| В            | OR<br>B      | OR<br>C      | OR<br>D       | OR<br>E       | OR<br>H       | OR<br>L      | OR<br>(HL)    | OR<br>A      | CP<br>B      | CP<br>C      | CP<br>D       | CP<br>E     | CP<br>H       | CP<br>L    | CP<br>(HL)    | CP<br>A    |

| С            | RET<br>NZ    | POP<br>BC    | JP<br>NZ,mn   | JP<br>mn      | CALL<br>NZ,mn | PUSH<br>BC   | ADD<br>A,n    | RST<br>0     | RET<br>Z     | RET          | JP<br>Z,mn    | esc         | CALL<br>Z,mn  | CALL<br>nn | ADC<br>A,n    | RST<br>1   |

| D            | RET<br>NC    | POP<br>DE    | JP<br>NC,mn   | OUT<br>(n),A  | CALL<br>NC,mn | PUSH<br>DE   | SUB<br>n      | RST<br>20    | RET<br>C     | EXX          | JP<br>C,mn    | IN<br>A,(n) | CALL<br>C,mn  | esc        | SBC<br>A,n    | RST<br>3   |

| E            | RET<br>PO    | POP<br>HL    | JP<br>PO,mn   | EX<br>(SP),HL | CALL<br>PO,mn | PUSH<br>HL   | AND<br>n      | RST<br>4     | RET<br>PE    | JP<br>(HL)   | JP<br>PE,mn   | EX<br>DE,HL | CALL<br>PE,mn | esc        | XOR<br>n      | RST<br>5   |

| F            | RET<br>P     | POP<br>AF    | JP<br>P,mn    | DI            | CALL<br>P,mn  | PUSH<br>AF   | OR<br>n       | RST 6        | RET<br>M     | LD<br>SP,HL  | JP<br>M,mn    | EI          | CALL<br>M,mn  | esc        | CP<br>n       | RST<br>7   |

# 3.4.2 ED Code Page

This table shows the code page for instructions whose first byte is EDh. These are miscellaneous instructions that will usually not be used as often as those on the main code page.

| \LSB<br>MSB\ | 0            | 1             | 2            | 3             | 4           | 5    | 6       | 7         | 8            | 9             | Α            | В             | С         | D    | E       | F         |

|--------------|--------------|---------------|--------------|---------------|-------------|------|---------|-----------|--------------|---------------|--------------|---------------|-----------|------|---------|-----------|

| 0            | IN0<br>B,(n) | OUT0<br>(n),B |              |               | TST<br>B    |      |         |           | IN0<br>C,(n) | OUT0<br>(n),C |              |               | TST<br>C  |      |         |           |

| 1            | IN0<br>D,(n) | OUT0<br>(n),D |              |               | TST<br>D    |      |         |           | IN0<br>E,(n) | OUT0<br>(n),E |              |               | TST<br>E  |      |         |           |

| 2            | IN0<br>H,(n) | OUT0<br>(n),H |              |               | TST<br>H    |      |         |           | IN0<br>L,(n) | OUT0<br>(n),L |              |               | TST<br>L  |      |         |           |

| 3            |              |               |              |               | TST<br>(HL) |      |         |           | IN0<br>A,(n) | OUT0<br>(n),A |              |               | TST<br>A  |      |         |           |

| 4            | IN<br>B,(C)  | OUT<br>(C),B  | SBC<br>HL,BC | LD<br>(mn),BC | NEG         | RETN | IM<br>0 | LD<br>I,A | IN<br>C,(C)  | OUT<br>(C),C  | ADC<br>HL,BC | LD<br>BC,(mn) | MLT<br>BC | RETI |         | LD<br>R,A |

| 5            | IN<br>D,(C)  | OUT<br>(C),D  | SBC<br>HL,DE | LD<br>(mn),DE |             |      | IM<br>1 | LD<br>A,I | IN<br>E,(C)  | OUT<br>(C),E  | ADC<br>HL,DE | LD<br>DE,(mn) | MLT<br>DE |      | IM<br>2 | LD<br>A,R |

| 6            | IN<br>H,(C)  | OUT<br>(C),H  | SBC<br>HL,HL | LD<br>(mn),HL | TST<br>n    |      |         | RRD       | IN L,(C)     | OUT<br>(C),L  | ADC<br>HL,HL | LD<br>HL,(mn) | MLT<br>HL |      |         | RLD       |

| 7            |              |               | SBC<br>HL,SP | LD<br>(mn),SP | TSTIO<br>n  |      | SLP     |           | IN<br>A,(C)  | OUT<br>(C),A  | ADC<br>HL,SP | LD<br>SP,(mn) | MLT<br>SP |      |         |           |

| 8            |              |               |              | OTIM          |             |      |         |           |              |               |              | OTDM          |           |      |         |           |

| 9            |              |               |              | OTIMR         |             |      |         |           |              |               |              | OTDMR         |           |      |         |           |

| Α            | LDI          | CPI           | INI          | OUTI          |             |      |         |           | LDD          | CPD           | IND          | OUTD          |           |      |         |           |

| В            | LDIR         | CPIR          | INIR         | OTIR          |             |      |         |           | LDDR         | CPDR          | INDR         | OTDR          |           |      |         |           |

| С            |              |               |              |               |             |      |         |           |              |               |              |               |           |      |         |           |

| D            |              |               |              |               |             |      |         |           |              |               |              |               |           |      |         |           |

| Е            |              |               |              |               |             |      |         |           |              |               |              |               |           |      |         |           |

| F            |              |               |              |               |             |      |         |           |              |               |              |               |           |      |         |           |

## 3.4.3 DD Code Page

This table shows the code page for instructions whose first byte is DDh. All instructions on this code page imply the use of the IX register in one way or another. Note that wherever the HL register is used in a main code page instruction, the corresponding instruction on this code page uses either the IX register, or the indexed addressing mode using the IX register.

| \LSB<br>MSB\ | 0              | 1              | 2              | 3              | 4              | 5              | 6               | 7              | 8 | 9            | Α             | В         | С | D | Е               | F |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|---|--------------|---------------|-----------|---|---|-----------------|---|

| 0            |                |                |                |                |                |                |                 |                |   | ADD<br>IX,BC |               |           |   |   |                 |   |

| 1            |                |                |                |                |                |                |                 |                |   | ADD<br>IX,DE |               |           |   |   |                 |   |

| 2            |                | LD<br>IX,mn    | LD<br>(mn),IX  | INC<br>IX      |                |                |                 |                |   | ADD<br>IX,IX | LD<br>IX,(mn) | DEC<br>IX |   |   |                 |   |

| 3            |                |                |                |                | INC<br>(IX+d)  | DEC<br>(IX+d)  | LD<br>(IX+d),n  |                |   | ADD<br>IX,SP |               |           |   |   |                 |   |

| 4            |                |                |                |                |                |                | LD<br>B,(IX+d)  |                |   |              |               |           |   |   | LD<br>C,(IX+d)  |   |

| 5            |                |                |                |                |                |                | LD<br>D,(IX+d)  |                |   |              |               |           |   |   | LD<br>E,(IX+d)  |   |

| 6            |                |                |                |                |                |                | LD<br>H,(IX+d)  |                |   |              |               |           |   |   | LD<br>L,(IX+d)  |   |

| 7            | LD<br>(IX+d),B | LD<br>(IX+d),C | LD<br>(IX+d),D | LD<br>(IX+d),E | LD<br>(IX+d),H | LD<br>(IX+d),L |                 | LD<br>(IX+d),A |   |              |               |           |   |   | LD<br>A,(IX+d)  |   |

| 8            |                |                |                |                |                |                | ADD<br>A,(IX+d) |                |   |              |               |           |   |   | ADC<br>A,(IX+d) |   |

| 9            |                |                |                |                |                |                | SUB<br>(IX+d)   |                |   |              |               |           |   |   | SBC<br>A,(IX+d) |   |

| Α            |                |                |                |                |                |                | AND<br>(IX+d)   |                |   |              |               |           |   |   | XOR<br>(IX+d)   |   |

| В            |                |                |                |                |                |                | OR<br>(IX+d)    |                |   |              |               |           |   |   | CP<br>(IX+d)    |   |

| С            |                |                |                |                |                |                |                 |                |   |              |               | esc       |   |   |                 |   |

| D            |                |                |                |                |                |                |                 |                |   |              |               |           |   |   |                 |   |

| E            |                | POP<br>IX      |                | EX<br>(SP),IX  |                | PUSH<br>IX     |                 |                |   | JP<br>(IX)   |               |           |   |   |                 |   |

| F            |                |                |                |                |                |                |                 |                |   | LD<br>SP,IX  |               |           |   |   |                 |   |

## 3.4.4 FD Code Page

This table shows the code page for instructions whose first byte is FDh. All instructions on this code page imply the use of the IY register in one way or another. This code page is identical to the DD code page with the IY register substituted for the IX register.

| \LSB<br>MSB\ | 0              | 1              | 2              | 3              | 4              | 5              | 6               | 7              | 8 | 9            | Α             | В         | С | D | Е               | F |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|---|--------------|---------------|-----------|---|---|-----------------|---|

| 0            |                |                |                |                |                |                |                 |                |   | ADD<br>IY,BC |               |           |   |   |                 |   |

| 1            |                |                |                |                |                |                |                 |                |   | ADD<br>IY,DE |               |           |   |   |                 |   |

| 2            |                | LD<br>IY,mn    | LD<br>(mn),IY  | INC<br>IY      |                |                |                 |                |   | ADD<br>IY,IY | LD<br>IY,(mn) | DEC<br>IY |   |   |                 |   |

| 3            |                | ,              | χ,,            |                | INC<br>(IY+d)  | DEC<br>(IY+d)  | LD<br>(IY+d),n  |                |   | ADD<br>IX,SP | ,             |           |   |   |                 |   |

| 4            |                |                |                |                | , , , , , ,    | , ,            | LD<br>B,(IY+d)  |                |   | ,=           |               |           |   |   | LD<br>C,(IY+d)  |   |

| 5            |                |                |                |                |                |                | LD<br>D,(IY+d)  |                |   |              |               |           |   |   | LD<br>E,(IY+d)  |   |

| 6            |                |                |                |                |                |                | LD<br>H,(IY+d)  |                |   |              |               |           |   |   | LD<br>L,(IY+d)  |   |

| 7            | LD<br>(IY+d),B | LD<br>(IY+d),C | LD<br>(IY+d),D | LD<br>(IY+d),E | LD<br>(IY+d),H | LD<br>(IY+d),L |                 | LD<br>(IY+d),A |   |              |               |           |   |   | LD<br>A,(IY+d)  |   |

| 8            |                |                |                |                |                |                | ADD<br>A,(IY+d) |                |   |              |               |           |   |   | ADC<br>A,(IY+d) |   |

| 9            |                |                |                |                |                |                | SUB<br>(IY+d)   |                |   |              |               |           |   |   | SBC<br>A,(IY+d) |   |

| Α            |                |                |                |                |                |                | AND<br>(IY+d)   |                |   |              |               |           |   |   | XOR<br>(IY+d)   |   |

| В            |                |                |                |                |                |                | OR<br>(IY+d)    |                |   |              |               |           |   |   | CP<br>(IY+d)    |   |

| С            |                |                |                |                |                |                |                 |                |   |              |               | esc       |   |   |                 |   |

| D            |                |                |                |                |                |                |                 |                |   |              |               |           |   |   |                 |   |

| Е            |                | POP<br>IY      |                | EX<br>(SP),IY  |                | PUSH<br>IY     |                 |                |   | JP<br>(IY)   |               |           |   |   |                 |   |

| F            |                |                |                |                |                |                |                 |                |   | LD<br>SP,IY  |               |           |   |   |                 |   |

# 3.4.5 CB Code Page

This table shows the code page for instructions whose first byte is CBh. The instructions on this code page are the majority of the shift, rotate and bit manipulation instructions.

| \LSB<br>MSB\ | 0          | 1          | 2          | 3          | 4          | 5          | 6             | 7          | 8          | 9          | Α          | В          | С          | D          | Е             | F          |

|--------------|------------|------------|------------|------------|------------|------------|---------------|------------|------------|------------|------------|------------|------------|------------|---------------|------------|

|              | RLC           | RLC        | RRC           | RRC        |

| 0            | В          | C          | D          | E          | Н          | L          | (HL)          | A          | В          | C          | D          | E          | Н          | L          | (HL)          | A          |

|              | RL            | RL         | RR            | RR         |

| 1            | В          | С          | D          | Е          | Н          | L          | (HL)          | Α          | В          | С          | D          | Е          | Н          | L          | (HL)          | Α          |

| 2            | SLA           | SLA        | SRA           | SRA        |

|              | В          | С          | D          | E          | Н          | L          | (HL)          | Α          | В          | С          | D          | E          | Н          | L          | (HL)          | Α          |

| 3            |            |            |            |            |            |            |               |            | SRL           | SRL        |

|              |            |            |            |            |            |            |               |            | В          | С          | D          | Е          | Н          | L          | (HL)          | Α          |

| 4            | BIT           | BIT        | BIT        | BIT        | BIT        | BIT        | BIT        | BIT        | BIT           | BIT        |

|              | 0,B        | 0,C        | 0,D        | 0,E        | 0,H        | 0,L        | 0,(HL)        | 0,A        | 1,B        | 1,C        | 1,D        | 1,E        | 1,H        | 1,L        | 1,(HL)        | 1,A        |

| 5            | BIT<br>2.B | BIT<br>2.C | BIT<br>2.D | BIT        | BIT        | BIT        | BIT<br>2.(HL) | BIT        | BIT<br>3.B | BIT        | BIT        | BIT<br>3.E | BIT<br>3.H | BIT<br>3.L | BIT           | BIT        |

|              | Z,B<br>BIT | 2,C<br>BIT | Z,D<br>BIT | 2,E<br>BIT | 2,H<br>BIT | 2,L<br>BIT | 2,(HL)<br>BIT | 2,A<br>BIT | 3,B<br>BIT | 3,C<br>BIT | 3,D<br>BIT | 3,E<br>BIT | 3,H<br>BIT | 3,L<br>BIT | 3,(HL)<br>BIT | 3,A<br>BIT |

| 6            | 4.B        | 4.C        | 4.D        | 4,E        | 4,H        | 4.L        | 4.(HL)        | 4,A        | 5.B        | 5.C        | 5.D        | 5.E        | 5.H        | 5.L        | 5,(HL)        | 5,A        |

|              | BIT           | BIT        | BIT        | BIT        | BIT        | BIT        | BIT        | BIT        | BIT           | BIT        |

| 7            | 6,B        | 6,C        | 6,D        | 6,E        | 6,H        | 6,L        | 6,(HL)        | 6,A        | 7,B        | 7,C        | 7,D        | 7,E        | 7,H        | 7,L        | 7,(HL)        | 7,A        |

| 8            | RES           | RES        | RES        | RES        | RES        | RES        | RES        | RES        | RES           | RES        |

| ٥            | 0,B        | 0,C        | 0,D        | 0,E        | 0,H        | 0,L        | 0,(HL)        | 0,A        | 1,B        | 1,C        | 1,D        | 1,E        | 1,H        | 1,L        | 1,(HL)        | 1,A        |

| 9            | RES           | RES        | RES        | RES        | RES        | RES        | RES        | RES        | RES           | RES        |

|              | 2,B        | 2,C        | 2,D        | 2,E        | 2,H        | 2,L        | 2,(HL)        | 2,A        | 3,B        | 3,C        | 3,D        | 3,E        | 3,H        | 3,L        | 3,(HL)        | 3,A        |

| Α            | RES           | RES        | RES        | RES        | RES        | RES        | RES        | RES        | RES           | RES        |

|              | 4,B        | 4,C        | 4,D        | 4,E        | 4,H        | 4,L        | 4,(HL)        | 4,A        | 5,B        | 5,C        | 5,D        | 5,E        | 5,H        | 5,L        | 5,(HL)        | 5,A        |

| В            | RES           | RES        | RES        | RES        | RES        | RES        | RES        | RES        | RES           | RES        |

|              | 6,B        | 6,C        | 6,D        | 6,E        | 6,H        | 6,L        | 6,(HL)        | 6,A        | 7,B        | 7,C        | 7,D        | 7,E        | 7,H        | 7,L        | 7,(HL)        | 7,A        |

| С            | SET           | SET        | SET        | SET        | SET        | SET        | SET        | SET        | SET           | SET        |

|              | 0,B<br>SET | 0,C<br>SET | 0,D<br>SET | 0,E<br>SET | 0,H<br>SET | 0,L<br>SET | 0,(HL)<br>SET | 0,A<br>SET | 1,B<br>SET | 1,C<br>SET | 1,D<br>SET | 1,E<br>SET | 1,H<br>SET | 1,L<br>SET | 1,(HL)<br>SET | 1,A<br>SET |

| D            | 2.B        | 2.C        | 2.D        | 2.E        | 2.H        | 2.L        | 2.(HL)        | 2.A        | 3.B        | 3.C        | 3.D        | 3.E        | 3.H        | 3.L        | 3.(HL)        | 3,A        |

|              | SET           | SET        | SET        | SET        | SET        | SET        | SET        | SET        | SET           | SET        |

| E            | 4.B        | 4.C        | 4.D        | 4,E        | 4,H        | 4.L        | 4,(HL)        | 4.A        | 5.B        | 5,C        | 5.D        | 5.E        | 5.H        | 5.L        | 5.(HL)        | 5,A        |

|              | SET           | SET        | SET        | SET        | SET        | SET        | SET        | SET        | SET           | SET        |

| F            | 6,B        | 6,C        | 6,D        | 6,E        | 6,H        | 6,L        | 6.(HL)        | 6,A        | 7,B        | 7,C        | 7,D        | 7,E        | 7,H        | 7,L        | 7,(HL)        | 7,A        |

### 3.4.6 DD-CB Code Page

This table shows the code page for instructions whose first two bytes are DDh, followed by CBh. All instructions on this code page imply the use of the IX register in one way or another. Note that wherever the HL register is used in a CB code page instruction, the corresponding instruction on this code page uses either the IX register, or the indexed addressing mode using the IX register.

| \LSB<br>MSB\ | 0 | 1 | 2 | 3 | 4 | 5 | 6               | 7 | 8 | 9 | Α | В | С | D | E               | F |

|--------------|---|---|---|---|---|---|-----------------|---|---|---|---|---|---|---|-----------------|---|

| 0            |   |   |   |   |   |   | RLC             |   |   |   |   |   |   |   | RRC             |   |

|              |   |   |   |   |   |   | (IX+d)          |   |   |   |   |   |   |   | (IX+d)          |   |

| 1            |   |   |   |   |   |   | RL              |   |   |   |   |   |   |   | RR              |   |

| -            |   |   |   |   |   |   | (IX+d)<br>SLA   |   |   |   |   |   |   |   | (IX+d)<br>SRA   |   |

| 2            |   |   |   |   |   |   | (IX+d)          |   |   |   |   |   |   |   | (IX+d)          |   |

|              |   |   |   |   |   |   | (IA+u)          |   |   |   |   |   |   |   | SRL             |   |

| 3            |   |   |   |   |   |   |                 |   |   |   |   |   |   |   | (IX+d)          |   |

|              |   |   |   |   |   |   | BIT             |   |   |   |   |   |   |   | BIT             |   |

| 4            |   |   |   |   |   |   | 0,(IX+d)        |   |   |   |   |   |   |   | 1,(IX+d)        |   |

| 5            |   |   |   |   |   |   | BIT             |   |   |   |   |   |   |   | BIT             |   |

| 3            |   |   |   |   |   |   | 2,(IX+d)        |   |   |   |   |   |   |   | 3,(IX+d)        |   |

| 6            |   |   |   |   |   |   | BIT             |   |   |   |   |   |   |   | BIT             |   |

|              |   |   |   |   |   |   | 4,(IX+d)        |   |   |   |   |   |   |   | 5,(IX+d)        |   |

| 7            |   |   |   |   |   |   | BIT             |   |   |   |   |   |   |   | BIT             |   |

| -            |   |   |   |   |   |   | 6,(IX+d)        |   |   |   |   |   |   |   | 7,(IX+d)        |   |

| 8            |   |   |   |   |   |   | RES<br>0,(IX+d) |   |   |   |   |   |   |   | RES<br>1,(IX+d) |   |

|              |   |   |   |   |   |   | RES             |   |   |   |   |   |   |   | RES             |   |

| 9            |   |   |   |   |   |   | 2,(IX+d)        |   |   |   |   |   |   |   | 3,(IX+d)        |   |

|              |   |   |   |   |   |   | RES             |   |   |   |   |   |   |   | RES             |   |

| Α            |   |   |   |   |   |   | 4,(IX+d)        |   |   |   |   |   |   |   | 5,(IX+d)        |   |

|              |   |   |   |   |   |   | RES             |   |   |   |   |   |   |   | RES             |   |

| В            |   |   |   |   |   |   | 6,(IX+d)        |   |   |   |   |   |   |   | 7,(IX+d)        |   |

| С            |   |   |   |   |   |   | SET             |   |   |   |   |   |   |   | SET             |   |

|              |   |   |   |   |   |   | 0,(IX+d)        |   |   |   |   |   |   |   | 1,(IX+d)        |   |

| D            |   |   |   |   |   |   | SET             |   |   |   |   |   |   |   | SET             |   |

|              |   |   |   |   |   |   | 2,(IX+d)        |   |   |   |   |   |   |   | 3,(IX+d)        |   |

| E            |   |   |   |   |   |   | SET             |   |   |   |   |   |   |   | SET             |   |

| <b>—</b>     |   |   |   |   |   |   | 4,(IX+d)        |   |   |   |   |   |   |   | 5,(IX+d)        |   |

| F            |   |   |   |   |   |   | SET<br>6,(IX+d) |   |   |   |   |   |   |   | SET<br>7,(IX+d) |   |

|              |   |   |   |   |   |   | 0,(IX+0)        |   |   |   |   |   |   |   | 7,(IA+a)        |   |

## 3.4.7 FD-CB Code Page

This table shows the code page for instructions whose first two bytes are FDh, followed by CBh. All instructions on this code page imply the use of the IY register in one way or another. This code page is identical to the DD-CB code page with the IY register substituted for the IX register.

| \LSB<br>MSB\ | 0 | 1 | 2 | 3 | 4 | 5 | 6               | 7 | 8 | 9 | Α | В | С | D | E               | F |

|--------------|---|---|---|---|---|---|-----------------|---|---|---|---|---|---|---|-----------------|---|

| 0            |   |   |   |   |   |   | RLC<br>(IY+d)   |   |   |   |   |   |   |   | RRC<br>(IY+d)   |   |

| 1            |   |   |   |   |   |   | RL<br>(IY+d)    |   |   |   |   |   |   |   | RR<br>(IY+d)    |   |

| 2            |   |   |   |   |   |   | SLA<br>(IY+d)   |   |   |   |   |   |   |   | SRA<br>(IY+d)   |   |

| 3            |   |   |   |   |   |   | (11+4)          |   |   |   |   |   |   |   | SRL<br>(IY+d)   |   |

| 4            |   |   |   |   |   |   | BIT<br>0,(IY+d) |   |   |   |   |   |   |   | BIT<br>1,(IY+d) |   |

| 5            |   |   |   |   |   |   | BIT<br>2,(IY+d) |   |   |   |   |   |   |   | BIT<br>3,(IY+d) |   |

| 6            |   |   |   |   |   |   | BIT<br>4,(IY+d) |   |   |   |   |   |   |   | BIT<br>5,(IY+d) |   |

| 7            |   |   |   |   |   |   | BIT<br>6,(IY+d) |   |   |   |   |   |   |   | BIT<br>7,(IY+d) |   |

| 8            |   |   |   |   |   |   | RES<br>0,(IY+d) |   |   |   |   |   |   |   | RES<br>1,(IY+d) |   |

| 9            |   |   |   |   |   |   | RES<br>2,(IY+d) |   |   |   |   |   |   |   | RES<br>3,(IY+d) |   |

| Α            |   |   |   |   |   |   | RES<br>4,(IY+d) |   |   |   |   |   |   |   | RES<br>5,(IY+d) |   |

| В            |   |   |   |   |   |   | RES<br>6,(IY+d) |   |   |   |   |   |   |   | RES<br>7,(IY+d) |   |

| С            |   |   |   |   |   |   | SET<br>0,(IY+d) |   |   |   |   |   |   |   | SET<br>1,(IY+d) |   |

| D            |   |   |   |   |   |   | SET<br>2,(IY+d) |   |   |   |   |   |   |   | SET<br>3,(IY+d) |   |

| E            |   |   |   |   |   |   | SET<br>4,(IY+d) |   |   |   |   |   |   |   | SET<br>5,(IY+d) |   |

| F            |   |   |   |   |   |   | SET<br>6,(IY+d) |   |   |   |   |   |   |   | SET<br>7,(IY+d) |   |

#### 3.5 Execution Tables

The tables below show the operation of the Y180 in detail for all instructions and exception conditions. These tables are a part of the spreadsheet included in the full electronic documentation for the Y180, which contains things like ALU operations, bus contents, internal register addresses, etc. The tables below should be sufficient for the majority of users of the Y180, but if you intend to modify the Y180 for your application, or merely want to understand the internal workings of the design, refer to the full spreadsheet for more detailed information.

#### 3.5.1 Execution Table Conventions

The conventions used in the instruction, opcode and operation columns of the execution tables are as follows:

```

b

bit select (000 = bit 0, 001 = bit 1, 010 = bit 2, 011 = bit 3, 100 = bit 4, 101 = bit 5,

110 = bit 6, 111 = bit 7

condition code select (00 = NZ, 01 = Z, 10 = NC, 11 = C)

cc

8-bit (signed) displacement

d

word register select (00 = BC, 01 = DE, 10 = IX, 11 = SP)

dd

8-bit (signed) displacement

e

f

condition code select (000 = NZ, 001 = Z, 010 = NC, 011 = C,

100 = PO, 101 = PE, 110 = P, 111 = M

MSB of a 16-bit constant

m

16-bit constant

mn

8-bit constant or LSB of a 16-bit constant

n

r, r'

byte register select (000 = B, 001 = C, 010 = D, 011 = E, 100 = H,

101 = L, 111 = A)

word register select (00 = BC, 01 = DE, 10 = HL, 11 = SP)

SS

Restart address select (000 = 0000h, 001 = 0008h, 010 = 0010h, 011 = 0018h,

V

100 = 0020h, 101 = 0028h, 110 = 0030h, 111 = 0038h)

word register select (00 = BC, 01 = DE, 10 = IX, 11 = SP)

XX

word register select (00 = BC, 01 = DE, 10 = IY, 11 = SP)

уу

word register select (00 = BC, 01 = DE, 10 = HL, 11 = AF)

ZZ

```

The conventions used in the flag columns of the execution tables are as follows:

- No change

- \* Updated per convention

- 0.1 Reset to zero or set to one

- IE Set to value of IEF 1 bit

- P, V Reports the parity (P) or overflow (V) status of the result

# 3.5.2 Instruction Opcode, Timing and Operation

The execution table below shows the instruction or exception, the opcode, the addressing mode, the number of machine cycles, the number and organization of the clock cycles, the flags affected by the instruction, and the operation performed by the instruction or exception.

| Instruction   | Opcode   | Opcode   | Opcode  | Opcode   | Addr     | Mach           | Clock cycles                   | s | z | н | Р | N | С | Operation                                                              |

|---------------|----------|----------|---------|----------|----------|----------------|--------------------------------|---|---|---|---|---|---|------------------------------------------------------------------------|

|               | byte 1   | byte 2   | byte 3  | byte 4   | Mode     | State          |                                |   |   |   | ٧ |   |   |                                                                        |

|               |          |          |         |          |          |                |                                |   |   |   |   |   |   |                                                                        |

| ADC A,(HL)    | 10001110 |          |         |          | reg ind  | 2              | 6 (3,3)                        | * | * | * | ٧ | 0 | * | A = A + (HL) + CF                                                      |

| ADC A,(IX+d)  | 11011101 | 10001110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | * | ٧ | 0 | * | A = A + (IX+d) + CF                                                    |

| ADC A,(IY+d)  | 11111101 | 10001110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | * | ٧ | 0 | * | A = A + (IY+d) + CF                                                    |

| ADC A,n       | 11001110 | n        |         |          | immed    | 2              | 6 (3,3)                        | * | * | * | ٧ | 0 | * | A = A + n + CF                                                         |

| ADC A,r       | 10001-r- |          |         |          | reg      | 2              | 4 (3,1)                        | * | * | * | ٧ | 0 | * | A = A + r + CF                                                         |

| ADC HL,ss     | 11101101 | 01ss1010 |         |          | reg      | 3              | 10 (3,3,4)                     | * | * | * | ٧ | 0 | * | HL = HL + ss + CF                                                      |

| ADD A,(HL)    | 10000110 |          | 1999    |          | reg ind  | 2              | 6 (3,3)                        | * | * | * | ٧ | 0 | * | A = A + (HL)                                                           |

| ADD A,(IX+d)  | 11011101 | 10000110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | * | ٧ | 0 | * | A = A + (IX+d)                                                         |

| ADD A,(IY+d)  | 11111101 | 10000110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | * | ٧ | 0 | * | A = A + (IY+d)                                                         |

| ADD A,n       | 11000110 | n        |         |          | immed    | 2              | 6 (3,3)                        | * | * | * | ٧ | 0 | * | A = A + n                                                              |

| ADD A,r       | 10000-r- |          |         |          | reg      | 2              | 4 (3,1)                        | * | * | * | ٧ | 0 | * | A = A + r                                                              |

| ADD HL,ss     | 00ss1001 |          |         |          | reg      | 2              | 7 (3,4)                        | - | - | - | ٧ | 0 | * | HL = HL + ss                                                           |

| ADD IX,xx     | 11011101 | 00xx1001 |         |          | reg      | 3              | 10 (3,3,4)                     | - | - | - | ٧ | 0 | * | IX = IX + xx                                                           |

| ADD IY,yy     | 11111101 | 00yy1001 |         |          | reg      | 3              | 10 (3,3,4)                     | - | • | - | ٧ | 0 | * | IY = IY + yy                                                           |

| AND (HL)      | 10100110 |          |         |          | reg ind  | 2              | 6 (3,3)                        | * | * | 1 | Р | 0 | 0 | A = A & (HL)                                                           |

| AND (IX+d)    | 11011101 | 10100110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | 1 | Р | 0 | 0 | A = A & (IX+d)                                                         |

| AND (IY+d)    | 11111101 | 10100110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | 1 | Р | 0 | 0 | A = A & (IY+d)                                                         |

| AND n         | 11100110 | n        |         |          | immed    | 2              | 6 (3,3)                        | * | * | 1 | Р | 0 | 0 | A = A & n                                                              |

| AND r         | 10100-r- |          |         |          | reg      | 2              | 4 (3,1)                        | * | * | 1 | Ρ | 0 | 0 | A = A & r                                                              |

| BIT b,(HL)    | 11001011 | 01-b-110 |         |          | reg ind  | 3              | 9 (3,3,3)                      | - | * | 1 | - | 0 | - | (HL) & bit                                                             |

| BIT b,(IX+d)) | 11011101 | 11001011 | d       | 01-b-110 | index    | 5              | 15 (3,3,3,3,3)                 | - | * | 1 | - | 0 | - | (IX+d) & bit                                                           |

| BIT b,(IY+d)) | 11111101 | 11001011 | d       | 01-b-110 | index    | 5              | 15 (3,3,3,3,3)                 | - | * | 1 | - | 0 | - | (IY+d) & bit                                                           |

| BIT b,r       | 11001011 | 01-br-   |         |          | reg      | 2              | 6 (3,3)                        | - | * | 1 | - | 0 | - | r & bit                                                                |

| CALL f,mn     | 11-f-100 | n        | m       |          |          | 2 (F)          | 6 (3,3)                        |   |   |   |   |   |   | if {f}                                                                 |

| CALL I,IIIII  |          |          | ***     |          | immed    | 6 (T)          | 16 (3,3,3,1,3,3)               | Ĺ | _ | Ľ | Ĺ | Ľ | Ĺ | (SP-1) = PCH; (SP-2) = PCL; PC = mn; SP = SP-2                         |

| CALL mn       | 11001101 | n        | m       |          | immed    | 6              | 16 (3,3,3,1,3,3)               | - | - | Ŀ | - | Ŀ | - | (SP-1) = PCH; (SP-2) = PCL; PC = mn; SP = SP-2                         |

| CCF           | 00111111 |          |         |          | none     | 1              | 3                              | - | - | 0 | - | 0 | * | CF = ~CF                                                               |

| CP (HL)       | 10111110 |          | ::::::: |          | reg ind  | 2              | 6 (3,3)                        | * | * | * | ٧ | 1 | * | A - (HL)                                                               |

| CP (IX+d)     | 11011101 | 10111110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | * | ٧ | 1 | * | A - (IX+d)                                                             |

| CP (IY+d)     | 11111101 | 10111110 | d       |          | index    | 5              | 14 (3,3,3,2,3)                 | * | * | * | ٧ | 1 | * | A - (IY+d)                                                             |

| CP n          | 11111110 | n        |         |          | immed    | 2              | 6 (3,3)                        | * | * | * | ٧ | 1 | * | A - n                                                                  |

| CP r          | 10111-r- |          |         |          | reg      | 2              | 4 (3,1)                        | * | * | * | ٧ | 1 | * | A - r                                                                  |

| CPD           | 11101101 | 10101001 |         |          | implied  | 4              | 12 (3,3,3,3)                   | * | * | * | * | 1 | - | A - (HL); BC = BC-1; HL = HL-1                                         |

| CPDR          | 11101101 | 10111001 |         |          | implied  | 4 (F)<br>5 (T) | 12 (3,3,3,3)<br>14 (3,3,3,3,2) | * | * | * | * | 1 | - | if {(BC != 0)   (A != (HL))} repeat:<br>A - (HL); BC = BC-1; HL = HL-1 |

| CPI           | 11101101 | 10100001 |         |          | implied  | 4              | 12 (3,3,3,3)                   | * | * | * | * | 1 | - | A - (HL); BC = BC-1; HL = HL+1                                         |

| CPIR          | 11101101 | 10110001 |         |          | implied  | 4 (F)<br>5 (T) | 12 (3,3,3,3)<br>14 (3,3,3,3,2) | * | * | * | * | 1 | - | if {(BC != 0)   (A != (HL))} repeat:<br>A - (HL); BC = BC-1; HL = HL+1 |

| CPL           | 00101111 |          |         |          | implied  | 1              | 3                              | - | - | 1 | - | 1 | - | A = ~A                                                                 |

| DAA           | 00100111 |          |         |          | implied  | 2              | 4 (3,1)                        | * | * | * | Р | - | - | Decimal Adjust Accumulator                                             |

| DEC (HL)      | 00110101 |          | ::::::: |          | reg ind  | 4              | 10 (3,3,1,3)                   | * | * | * | ٧ | 1 | - | (HL) = (HL) - 1                                                        |

| DEC (IX+d)    | 11011101 | 00110101 | d       |          | index    | 7              | 18 (3,3,3,2,3,1,3)             | * | * | * | ٧ | 1 | - | (IX+d) = (IX+d) -1                                                     |

| DEC (IY+d)    | 11111101 | 00110101 | d       |          | index    | 7              | 18 (3,3,3,2,3,1,3)             | * | * | * | ٧ | 1 | - | (IY+d) = (IY+d) -1                                                     |

| DEC IX        | 11011101 | 00101011 |         |          | reg      | 3              | 7 (3,3,1)                      | - | - | - | - | - | - | IX = IX - 1                                                            |

| DEC IY        | 11111101 | 00101011 |         |          | reg      | 3              | 7 (3,3,1)                      | - | - | - | - | F | - | IY = IY - 1                                                            |

| DEC r         | 00-r-101 |          |         |          | reg      | 2              | 4 (3,1)                        | * | * | * | ٧ | 1 | - | r=r-1                                                                  |

| DEC ss        | 00ss1011 |          |         |          | reg      | 2              | 4 (3,1)                        | - | - | - | - | F | - | ss = ss - 1                                                            |

| DI            | 11110011 |          |         |          | none     | 1              | 3                              | - | - | - | - | ŀ | - | IEF1 = 0; IEF2 = 0                                                     |

| D IN7:        | 00010000 | (j-2)-   |         |          |          | 3 (F)          | 7 (3,1,3)                      |   | П | Г |   | Г |   |                                                                        |

| DJNZ j        | 20010000 | -(J-2)-  |         |          | relative | 4 (T)          | 9 (3,1,3,2)                    | Ĺ | Ī | Ľ | Ĺ | Ľ | Ĺ | B = B-1; if {B != 0} PC = PC + j                                       |

| Instruction            | Opcode<br>byte 1     | Opcode<br>byte 2 | Opcode<br>byte 3 | Opcode<br>byte 4 | Addr<br>Mode       | Mach<br>State  | Clock cycles                   | S | Z | Н | P<br>V | N | С | Operation                                           |

|------------------------|----------------------|------------------|------------------|------------------|--------------------|----------------|--------------------------------|---|---|---|--------|---|---|-----------------------------------------------------|

| EI                     | 11111011             |                  | :::::::          |                  | none               | 1              | 3                              | - | - | - | -      | - | - | IEF1 =1; IEF2 = 1                                   |

| EX (SP),HL             | 11100011             |                  |                  |                  | implied            | 6              | 16 (3,3,3,1,3,3)               | - | - | - | -      | - | - | H <-> (SP+1); L <-> (SP)                            |

| EX (SP),IX             | 11011101             | 11100011         |                  | 10111            | implied            | 7              | 19 (3,3,3,3,1,3,3)             | - | - | - | -      | - | - | IXH <-> (SP+1); IXL <-> (SP)                        |

| EX (SP),IY             | 11111101             | 11100011         |                  |                  | implied            | 7              | 19 (3,3,3,3,1,3,3)             | - | - | - | -      | - | - | IYH <-> (SP+1); IYL <-> (SP)                        |

| EX AF,AF'              | 00001000             |                  |                  |                  | implied            | 2              | 4 (3,1)                        |   |   |   | -      |   | • | AF <-> AF'                                          |

| EX DE,HL               | 11101011             |                  |                  |                  | implied            | 1              | 3                              | 1 | - | 1 | -      | 1 | 1 | DE <-> HL                                           |

| EXX                    | 11011001             |                  |                  |                  | implied            | 1              | 3                              | - | • |   | •      |   | • | BC <-> BC'; DE <-> DE'; HL <-> HL'                  |

| HALT                   | 01110110             |                  |                  |                  | none               | 1              | 3                              | - | - | - | -      | - | - | CPU halted                                          |

| IM 0                   | 11101101             | 01000110         |                  |                  | none               | 2              | 6 (3,3)                        | - | - | - | -      | - | - | No operation                                        |

| IM 1                   | 11101101             | 01010110         |                  | :::::::          | none               | 2              | 6 (3,3)                        | - | - | - | -      | - | - | Interrupt mode 1                                    |

| IM 2                   | 11101101             | 01011110         |                  |                  | none               | 2              | 6 (3,3)                        | - | - | - | Ŀ      | - | - | Interrupt mode 2                                    |

| IN A,(n)               | 11011011             | n                |                  |                  | direct             | 3              | 9 (3,3,3)                      | - | - | - | -      | - | - | A = (An)                                            |

| IN r,(C)               | 11101101             | 01-r-000         |                  | 100000           | indirect           | 3              | 9 (3,3,3)                      | * | * | 0 | Р      | 0 | - | r = (BC)                                            |

| IN0 r,(n)              | 11101101             | 00-r-000         | n                |                  | direct             | 4              | 12 (3,3,3,3)                   | * | * | 0 | Р      | 0 | - | r = (n)                                             |

| INC (HL)               | 00110100             |                  |                  |                  | reg ind            | 4              | 10 (3,3,1,3)                   | * | * | * | ٧      | 0 | - | (HL) = (HL) + 1                                     |

| INC (IX+d)             | 11011101             | 00110100         | d                |                  | index              | 7              | 18 (3,3,3,2,3,1,3)             | Ļ | Ť | _ | ٧      | 0 | - | (IX+d) = (IX+d) + 1                                 |

| INC (IY+d)             | 11111101             | 00110100         | d                |                  | index              | 7              | 18 (3,3,3,2,3,1,3)             | Ľ | _ | Ľ | ٧      | 0 | Ŀ | (IY+d) = (IY+d) + 1                                 |

| INC IX                 | 11011101             | 00100011         |                  |                  | reg                | 3              | 7 (3,3,1)                      | H | H | Ė | Ŀ      | Ė | Ė | IX = IX + 1                                         |

| INC IY                 | 11111101<br>00-r-100 | 00100011         |                  |                  | reg                | 3              | 7 (3,3,1)                      | Ļ | - | Ļ | -<br>V | ٠ | Ė | IY = IY + 1                                         |

| INC r                  |                      |                  |                  |                  | reg                | 2              | 4 (3,1)                        | Ė | Ĥ | Ě | ٧      | 0 | Ŀ | r=r+1                                               |

| INC ss                 | 00ss0011             | 10101010         |                  | 1:1:1:1:         | reg                | 2              | 4 (3,1)                        | Ė | * | - | -      | * | - | SS = SS + 1                                         |

| IND                    | 11101101             | 10101010         |                  |                  | implied            | 4              | 12 (3,3,3,3)                   | - | À | - | -      | Ė | - | (HL) = (BC); HL = HL-1; B = B-1                     |

| INDR                   | 11101101             | 10111010         |                  |                  | implied            | 4 (F)<br>5 (T) | 12 (3,3,3,3)<br>14 (3,3,3,3,2) | - | 1 |   | -      | * | • | if {B != 0} repeat: (HL) = (BC); HL = HL-1; B = B-1 |

| INI                    | 11101101             | 10100010         |                  |                  | implied            | 4              | 12 (3,3,3,3)                   | - | * | - | -      | * | - | (HL) = (BC); HL = HL+1; B = B-1                     |

| INIR                   | 11101101             | 10110010         |                  |                  | implied            | 4 (F)<br>5 (T) | 12 (3,3,3,3)<br>14 (3,3,3,3,2) |   | 1 | - | -      | * |   | if {B != 0} repeat: (HL) = (BC); HL = HL+1; B = B-1 |

| JP (HL)                | 11101001             |                  |                  |                  | implied            | 1              | 3                              | - | - | - | -      | - | - | PC = HL                                             |

| JP (IX)                | 11011101             | 11101001         |                  |                  | implied            | 2              | 6 (3,3)                        | - | - | - | -      | - | - | PC = IX                                             |

| JP (IY)                | 11111101             | 11101001         |                  |                  | implied            | 2              | 6 (3,3)                        | - | - | - | -      | - | Ŀ | PC = IY                                             |

| JP f,mn                | 11-f-010             | n                | m                |                  | immed              | 2 (F)<br>3 (T) | 6 (3,3)<br>9 (3,3,3)           |   | - | - | -      | - |   | if {f} PC = mn                                      |

| JP mn                  | 11000011             | n                | m                |                  | immed              | 3              | 9 (3,3,3)                      | - | - | - | -      | - | - | PC = mn                                             |

| JR cc,e                | 001cc000             | (e-2)-           |                  |                  | relative           | 2 (F)<br>3 (T) | 6 (3,3)<br>8 (3,3,2)           |   | - |   | -      |   | - | if $\{cc\}$ PC = PC + j                             |

| JR e                   | 00011000             | (e-2)-           |                  |                  | relative           | 3              | 8 (3,3,2)                      | - | - | - | -      | - | - | PC = PC + j                                         |

| LD (BC),A              | 00000010             |                  |                  |                  | implied            | 3              | 7 (3,1,3)                      | - | - | - | -      | - | - | (BC) = A                                            |

| LD (DE),A              | 00010010             |                  |                  |                  | implied            | 3              | 7 (3,1,3)                      | - | - | - | -      | - | - | (DE) = A                                            |

| LD (HL),n              | 00110110             | n                |                  |                  | immed              | 3              | 9 (3,3,3)                      | - | - | - | -      | - | - | (HL) = n                                            |

| LD (HL),r              | 01110-r-             |                  |                  |                  | reg                | 3              | 7 (3,1,3)                      | - | - | - | -      | - | - | (HL) = r                                            |

| LD (IX+d),n            | 11011101             | 00110110         | d                | n                | immed              | 5              | 15 (3,3,3,3,3)                 | - | - | - | ŀ      | - | - | (IX+d) = n                                          |