# **Y80 Microprocessor**

# **Technical Manual**

#### Disclaimer

Systemyde International Corporation reserves the right to make changes at any time, without notice, to improve design or performance and provide the best product possible. Systemyde International Corporation makes no warrant for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make any commitment to update the information contained herein.

Systemyde International Corporation products are not authorized for use in life support devices or systems unless a specific written agreement pertaining to such use is executed between the manufacturer and the President of Systemyde International Corporation. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents, copyrights or other rights of third parties. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Systemyde International Corporation. All trademarks are trademarks of their respective companies.

Every effort has been made to ensure the accuracy of the information contain herein. If you find errors or inconsistencies please bring them to our attention. In all cases, however, the Verilog HDL source code for the Y90 design defines "proper operation".

Copyright © 2011, Systemyde International Corporation. All rights reserved.

#### Notice:

"Z80" and "Zilog" are registered trademarks of Zilog, Inc. All uses of these terms in this document are to be construed as adjectives, whether or not the noun "microprocessor", "CPU" or "device" are actually present.

# Table of Contents

| Introduction     |    |

|------------------|----|

| Features         | 5  |

| Pin Descriptions | 7  |

| External Timing  | 11 |

| Instruction Set  | 25 |

# **Revison History**

Date Changes

Page(s)

# Introduction

This book documents the operation of the Y80 microprocessor. The Y80 design is supplied in Verilog HDL and can be implemented in any technology supported by a logic synthesis tool that accepts Verilog HDL. Included in the design package is a test bench that exercises all instructions, flag settings, and representative data patterns. The test patterns should achieve at least 95% fault coverage.

The Y80 CPU was designed in a clean-room environment and is compatible with the Zilog Z80 microprocessor. Only publicly available documentation was used to create this design so there may be minor differences where the public documentation is misleading or lacking. The instruction execution times are not identical between the two designs. The Y80 CPU operates with a consistent two-clock-cycle machine cycle, while the Z80 microprocessor uses machine cycles that vary from three to seven clock cycles.

This document should always be used as the final word on the operation of the Y80 CPU, but it is useful to refer to the Zilog documentation if the description given here is too cryptic. The Z80 architecture is over thirty years old, so it is assumed that it is already at least somewhat familiar to the reader.

The Y80 CPU is accompanied by full design documentation, in the form of a large spreadsheet, which describes nearly every facet of the internal operation of the processor. This provides knowledgeable users the opportunity to customize the design for unique application requirements.

# Features

- \* Fully functional synthesizable Verilog HDL version of the Z80 CPU

- \* Vendor and technology independent

- \* Software compatible with several industry-standard processors

- \* 189 instructions

- \* Eight addressing modes

- \* 64K byte memory addressing capability

- \* Separate 64K byte I/O address space

- \* 16 bit ALU with bit, byte and BCD operations

- \* Powerful vectored interrupt capability with separate interrupt vector input bus

- \* Static, fully synchronous design uses no 3-state buses

- \* Uniform 2 clock-cycle machine cycle

- \* Memory interface matches common FPGA and ASIC memory timing

- \* Separate I/O bus, compatible with AMBA Peripheral Bus

- \* Full design documentation included

- \* Verilog simulation and test suite included

Shown below are the registers visible to the programmer. The main registers have both a primary and an alternate version. The primary register set consists of A, F, B, C, D, E, H, and L, while the alternate register set consists of A', F', B', C', D', E', H', and L'. At any given time only one bank is active, and care must be used when switching between banks, as there is no way for the programmer to check which bank is active. The accumulator, A, is the destination for all 8-bit arithmetic and logic operations, while the Flag register F contains the flag results of arithmetic and logic operations. The other general-purpose registers can be paired, BC or DE or HL, to form 16-bit registers. There are two index registers, IX and IY, used for indexed addressing mode. The I register holds the upper eight bits of the interrupt vector table address for use in Interrupt Mode 2. The R register is left over from the original Z80 architecture, where it was used to hold a refresh address for DRAMs. In the Y80 it is just another general purpose register. The Stack pointer, SP, holds the address of the stack, and the Program Counter, PC, holds the address of the currently executing instruction.

| Α  | F |  |

|----|---|--|

| В  | С |  |

| D  | Ε |  |

| Н  | L |  |

| IX |   |  |

| IY |   |  |

Main Register Bank

| А' | F' |

|----|----|

| В' | C' |

| D' | Е' |

| Н' | L' |

I R

| SP |

|----|

| РС |

Alternate Register Bank

Special Function Registers

# **Pin Descriptions**

The Y80 design does not attempt to match the signals or timing present on the Z80 microprocessor. Rather, the interfaces and signals are optimized for use in either an ASIC or an FPGA.

Memory and I/O use separate address and data buses in addition to the separate control signals. The memory bus is designed to match typical ASIC and FPGA memory timing, although it can be used with stand-alone memory devices just as easily. A separate interrupt vector bus is provided for use with an interrupt controller. If desired, this interrupt vector bus can be tied to either the memory or I/O input bus for operation more closely resembling that of the original Z80.

The interface signals for the Y80 CPU are detailed below. Note that all inputs except the two resets are sampled by the rising edge of the clock and all outputs change in response to the rising edge of the clock.

**clearb** (input, active-Low) The Master (test) Reset signal is used to initialize all of the flip-flops that are not initialized by the user reset signal. Most user-visible registers are not affected by the user reset, so this signal allows full initialization for testing and simulation. This is an asynchronous signal that should be used for Power-On Reset.

clkc (input, active-High) The CPU Clock connects to all flip-flops in the design.

- dma\_ack (output, active-High) The DMA Acknowledge signal is activated to indicate that the processor has halted to allow another bus master to use the bus. The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out, mem\_data\_out, mem\_tran, reti\_tran and t1 signals are all inactive (Low) during this time. The processor will signal dma\_ack while in the Halt state without de-asserting the halt\_tran signal. Interrupts are not sampled while the dma\_ack signal is active, so the exit from a coincident Halt state will be deferred until the dma\_ack signal is no longer active.

- **dma\_req** (input, active-High) The DMA Request signal requests that the processor halt to allow another bus master to transfer data on the bus. The processor only

releases the bus between instructions, rather than between individual bus transactions.

- halt\_tran (output, active-High) The Halt Transaction signal is activated by the Halt

instruction. While in the Halt state the CPU freezes and waits for an interrupt.

The iack\_tran, io\_addr\_out, io\_data\_out, io\_tran, mem\_addr\_out,

mem\_data\_out, mem\_tran, reti\_tran and t1 signals are all inactive (Low)

during this time.

- **iack\_tran** (output, active-High) The Interrupt Acknowledge Transaction signal is activated to identify an interrupt acknowledge bus transaction. An interrupt acknowledge occurs in response to either a Non-Maskable Interrupt request or an enabled Maskable Interrupt request. During an interrupt acknowledge the interrupt vector data bus is sampled, although the sampled value is only used in Interrupt Mode 2 with a maskable interrupt request.

- int\_req (input, active-High) The Interrupt Request signal is the maskable interrupt request. Maskable interrupts can be enabled and disabled under program control. This interrupt request is not latched, so it should remain active until an interrupt acknowledge transaction occurs.

- io\_addr\_out (output, 16-bit bus) The I/O Address Output bus carries the address of the I/ O port during an I/O transaction. This bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **io\_data\_in** (input, 8-bit bus) The I/O Data Input bus is sampled during the various I/O input instructions. A separate bus allows peripherals to be connected without loading the memory data bus.

- **io\_data\_out** (output, 8-bit bus) The I/O Data Output bus carries the output data for I/O output instructions. This bus holds the current value until the next I/O transaction or until the **dma\_ack** signal is activated.

- **io\_read** (output, active-High) The I/O Read signal indicates the direction of data transfer during I/O transactions. High signals read and Low signals write. This signal is valid only during I/O transactions.

- **io\_strobe** (output, active-High) The I/O Strobe signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for I/O transactions.

- io\_tran (output, active-High) The I/O Transaction signal is activated for all I/O transactions.

- **ivec\_data\_in** (input, 8-bit bus) The Interrupt Vector Data Input bus is sampled during interrupt acknowledge transactions. If the interrupt acknowledge was for a maskable interrupt and the CPU is in Interrupt Mode 2, this vector is used as a pointer in the interrupt vector table to find the starting address of the interrupt service routine.

- **ivec\_read** (output, active-High) The Interrupt Vector Read signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for interrupt acknowledge transactions.

- mem\_addr\_out (output, 16-bit bus) The Memory Address Output bus carries the address during memory read and write transactions. This bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **mem\_data\_in** (input, 8-bit bus) The Memory Data Input bus is sampled during memory read transactions. A separate bus allows peripherals to be connected without loading the memory data bus.

- mem\_data\_out (output, 8-bit bus) The Memory Data Output bus carries the output data for memory write transactions. This bus holds the current value until the next I/O transaction or until the dma\_ack signal is activated.

- **mem\_rd** (output, active-High) The Memory Read signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for memory read transactions.

- **mem\_tran** (output, active-High) The Memory Transaction signal is activated for memory read and write transactions. The **mem\_tran** signal is active during the Halt state but is inactive during DMA transfers.

- **mem\_wr** (output, active-High) The Memory Write signal is one clock cycle wide (in the absence of Wait states) and identifies the data transfer clock cycle for memory write transactions.

- nmi\_req (input, active-High) The Non-Maskable Interrupt Request signal unconditionally interrupts the CPU. This request is internally latched, so that it can be as short as one clock cycle wide.

- **resetb** (input, active-Low) The User Reset signal is used to initialize all state flip-flops and some user registers (the I, R, PC and SP registers). This is an asynchronous signal.

- **reti\_tran** (output, active-High) The Return From Interrupt transaction signal is activated immediately after the second stack read transaction during the Return From

Interrupt (RETI) instruction. This signal may be used by an external interrupt controller to re-enable interrupts, for example.

- t1 (output, active-High) The T1 signal is active during the first clock cycle of a bus transaction. This signal is inactive during the Halt state.

- wait\_req (input, active-High) The Wait Request signal temporarily halts the CPU, usually

to wait for memory access time to be met. The wait request is not honored

during the bus idle state, or while the halt\_tran signal is active.

# **External Timing**

The Y80 CPU uses a uniform two-clock-cycle machine cycle. This consistent timing simplifies the design of logic external to the CPU makes it easier to track the state of the CPU.

The memory interface timing and signals are designed to make it easy to interface to standard ASIC and FPGA memories. It uses separate read and write strobes.

The I/O interface is very close to the AMBA Peripheral Bus (APB) to allow connection to APB peripherals with a minimum of logic. It uses a single strobe with a separate direction control. The only difference relative to the APB is the setup time for the write data. In the APB the write data is setup one clock before the strobe; in this interface the write data changes coincident with the leading edge of the strobe. In most cases this will not be a problem.

The separate interrupt vector bus provides an easy way to connect to the optional interrupt controller. The interrupt vector bus is used for Mode 2 maskable interrupts, so if this mode is not used the vector input bus can be tied to ground and the vector strobe output ignored.

In the diagrams below only the relevant signals are shown for each transaction. All other signals are either inactive or hold the previous value. Note that only one of the transaction identifiers (**mem\_tran, io\_tran, iack\_tran, reti\_tran,** and **halt\_tran**) can be active at a time. If all are inactive, an idle bus transaction (usually for address calculation) is in progress. The **dma\_ack** signal also indicates that the bus is idle, in response to the **dma\_req** signal. The **dma\_ack** signal can be active while **halt\_tran** is active.

The **wait\_req** input is only sampled for memory, I/O and interrupt acknowledge transactions and is ignored in all other cases. Wait states will disrupt the two-clock-cycle machine cycle rule. If this feature is important but wait states must be used, two wait states per transaction is recommended. If memory access time is an issue it might be better to stretch the first clock cycle of a transaction rather than add Wait states. The uniform two-clock machine cycle makes it relatively straightforward to do this.

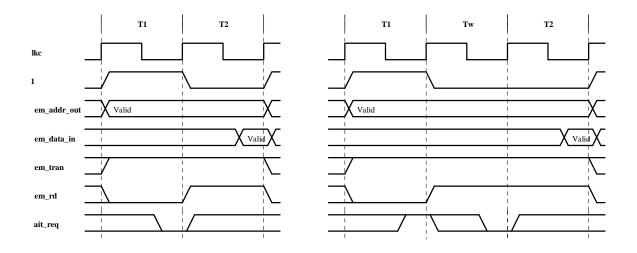

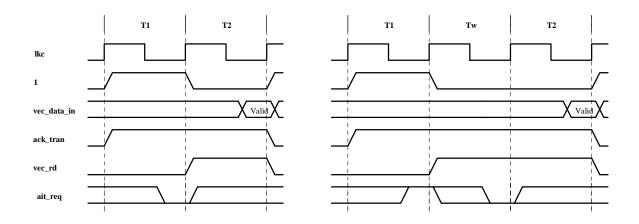

## **Memory Read**

The figure below shows the memory read transaction, without Wait states and with one Wait state. Memory read transactions are used for both instruction and data fetch. There is no separate instruction/data status indicator, although this status exists internally if it is needed.

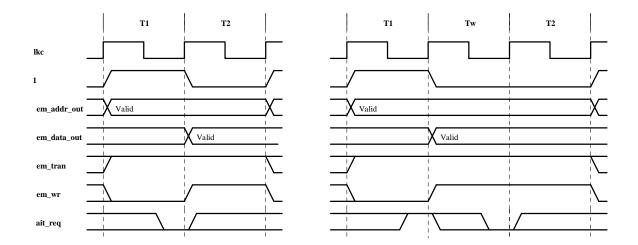

# **Memory Write**

The figure below shows the memory write transaction, without Wait states and with one Wait state.

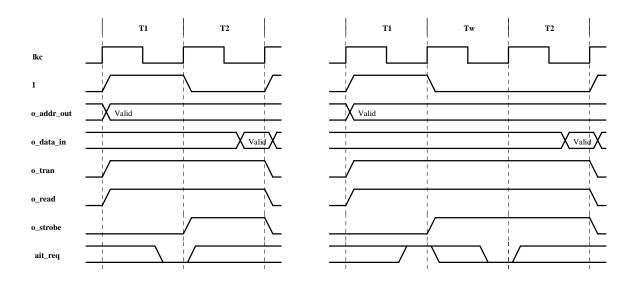

# I/O Read

The figure below shows an I/O read transaction, without Wait states and with one Wait state.

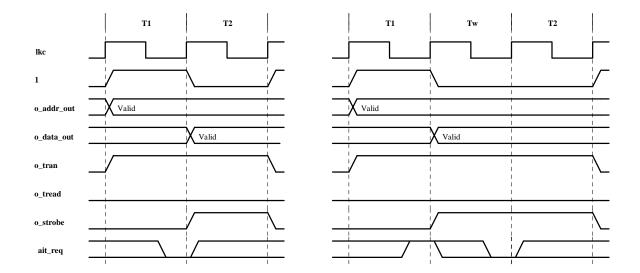

## I/O Write

The figure below shows an I/O write transaction, without Wait states and with one Wait state.

# **Interrupt Acknowledge**

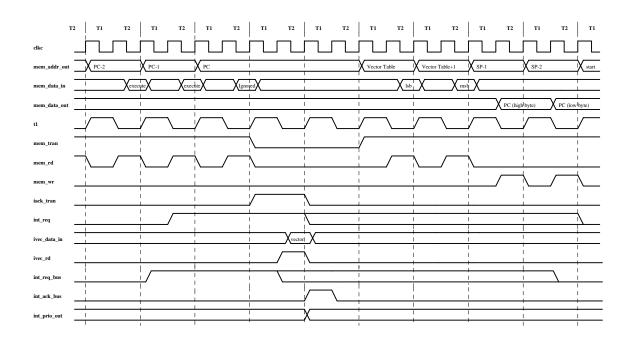

The figure below shows the interrupt acknowledge transaction, without Wait states and with one Wait state.

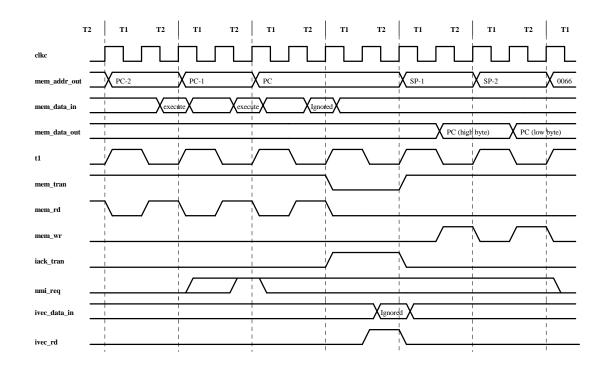

### **Non-maskable Interrupt**

The timing of a non-maskable interrupt acknowledge transaction is shown below. The **nmi\_req** input cannot be masked by software. This input must be sampled active by a rising edge of **clkc** to be recognized by the processor, but does not need to remain active until the interrupt acknowledge transaction. In fact, to prevent an endless loop of acknowledges, the **nmi\_req** input must be de-asserted before the start of the fetch of the first instruction of the service routine. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, and two writes to push the contents of the program counter onto the stack. Execution then begins at 0x0066 with an instruction fetch. The non-maskable interrupt service routine must end with the RETN instruction to properly restore the state of the interrupt enable flag prior to the non-maskable interrupt.

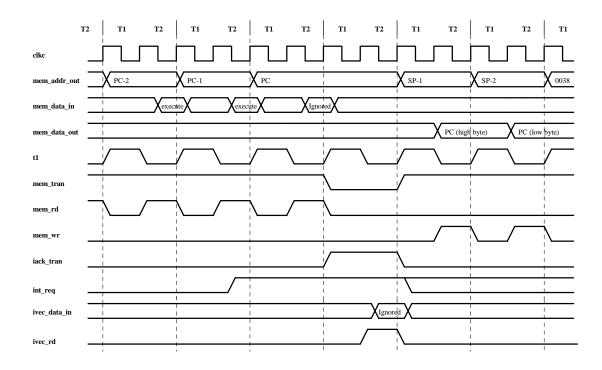

## **Interrupt Mode 0 or 1**

The timing of a Mode 0 or Mode 1 interrupt acknowledge cycle is shown below. The **int\_req** input needs to remain active until the interrupt acknowledge transaction. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, and two writes to push the contents of the program counter onto the stack. Execution then begins at address 0x0038 with an instruction fetch.

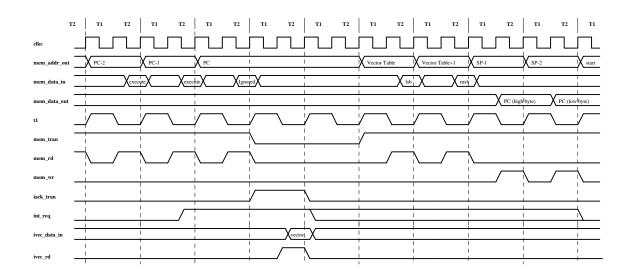

### **Interrupt Mode 2**

The timing of a Mode 2 maskable interrupt acknowledge is shown below. The **int\_req** input needs to remain active until the interrupt acknowledge transaction. The acknowledge sequence consists of an aborted instruction fetch, the interrupt acknowledge, an address calculation cycle, two reads of the interrupt vector table and two writes to push the contents of the program counter onto the stack. The processor automatically jumps to the address fetched from the interrupt vector table for the service routine. The upper eight bits of the interrupt vector table starting address are held in the I register in the processor. Note that the vector must be an even number. That is, the least significant bit of the vector must be a zero.

The interrupt controller in the Y80 MPU necessarily samples the **int\_req\_bus** inputs, which changes the timing slightly. The diagram below illustrates this change for Interrupt Mode 2. Also shown is the timing of the **int\_ack\_bus** and the **int\_prio\_out** signals.

Although Interrupt Mode 2 is the preferred mode for use with the interrupt controller, the design allows the use of any interrupt mode. In Interrupt Mode 0 or 1 it will be necessary to use the **int\_ack\_bus** signals to externally latch the information about which interrupt is being acknowledged. This is because Interrupt Modes 0 and 1 will branch to a common interrupt service routine, rather than the individual routines possible in Interrupt Mode 2.

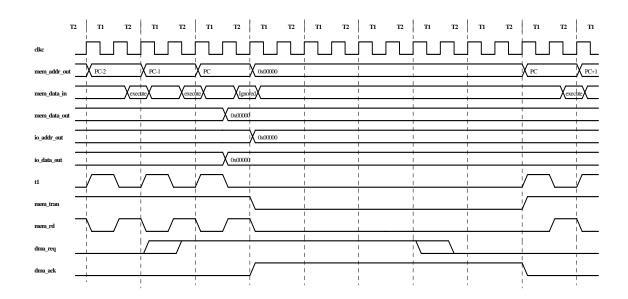

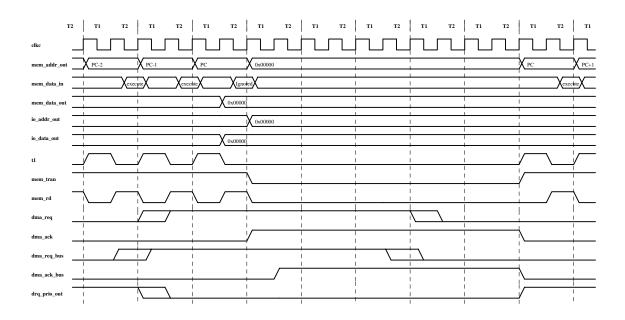

# **DMA Request/Acknowledge**

The timing of a DMA request and acknowledge is shown below. Note that like an interrupt, the **dma\_req** signal is only sampled at the end of instructions. This guarantees that all instructions are atomic.

The delay from the **dma\_req** signal to the **dma\_ack** signal is always at least one bus cycle, irrespective of whether the processor is running, in the Halt state or in the Sleep state. This implies that it is more efficient to transfer multiple bytes each time that the **dma\_req** signal is activated.

The **dma\_req** signal can be asserted during the Halt or Sleep states. In this case the active **dma\_req** signal will take precedence over **int\_req** or **nmi\_req** and inhibit either of these signals from causing an exit from the Halt or Sleep state. Once the **dma\_req** signal is deasserted any pending or future interrupt request will cause the exit from the Halt or Sleep state.

The DMA request controller in the Y80 MPU necessarily samples the **dma\_req\_bus** inputs, which changes the timing slightly. The diagram below illustrates this change. Also shown is the timing of the **dma\_ack\_bus** and the **dma\_prio\_out** signals. In particular, note that the leading edge of the **dma\_ack\_bus** signals are delayed by one clock cycle from the normal **dma\_ack** timing. The timing of the trailing edge of these signals is not affected.

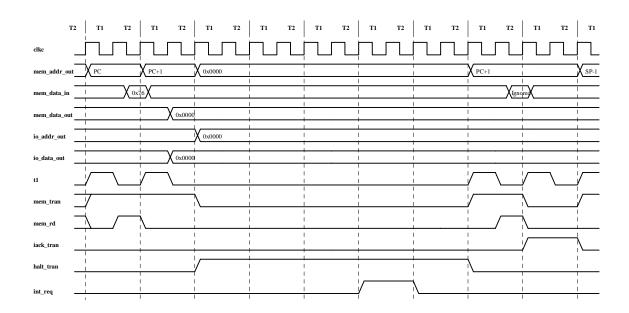

### Halt state

The Halt state is entered when the HALT instruction is executed, as shown below. In the Halt state the processor freezes, for an unlimited number of two clock cycle machine cycles, with the **halt\_tran** output active. The only way to exit the Halt state is with either an interrupt (either **nmi\_req** or **int\_req**) or via reset. Note that **int\_req** can only be used to exit the Halt mode if interrupts are enabled when the HALT instruction is executed. The timing for exiting the Halt state with an interrupt is also shown below.

If the Halt state is exited by an interrupt, the processor will resume instruction execution (after the interrupt service routine) at the address of the instruction following the HALT instruction. The minimum width of the **halt\_tran** signal is two clock cycles.

The Halt state in this design is slightly different from that in the Z80 microprocessor. In that design the processor continues to fetch the Halt instruction during the Halt state, leading to continued power dissipation. Since this operation requires the special step of "rewinding" the PC, no attempt was made to match this operation. Rather, the Halt state reduces the power consumption to a minimum by minimizing the number of signals that are transitioning during this state.

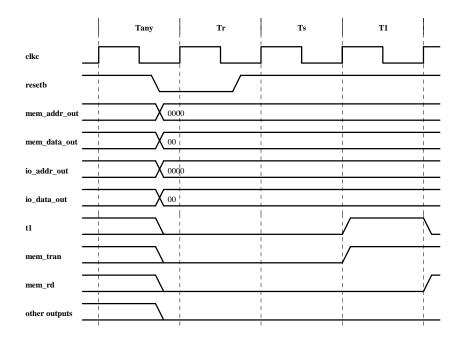

### Reset

The Reset state is entered immediately when the **resetb** signal goes Low, independent of the current state, and this state continues until the first rising edge of **clkc** after the **resetb** signal is de-asserted. At this rising edge there is a one clock cycle transient state to set up the internal pipeline controls, and on the next clock the processor begins fetching the first instruction from address 0x0000.

Software starting at location 0x0000 must be able to distinguish between reset, execution of an RST 0 instruction, a trap, or watch-dog time-out. All of these cases cause the Program Counter to be reset to 0x0000. In the case of the Y90 MPU this information is available in the System Status Block.

The minimum width of the **resetb** signal is set by the flip-flops used in the design. The setup time for the **resetb** signal to the rising edge of the **clkc** signal is likewise determined by the flip-flops used in the design.

The **clearb** signal has the same timing requirements as the **resetb** signal. The **clearb** signal should only be used in the power-on case, and only affects those flip-flops not affected by the **resetb** signal.

# **Instruction Set**

This chapter presents the assembly language syntax, addressing modes, flag settings, binary encoding, and execution time for the Y80 instruction set. The entire instruction set is presented in alphabetical order.

The assembly language syntax is identical to that used by the original Zilog assembler. Different assembler programs may or may not use identical syntax. The syntax is presented generically at the beginning of each instruction, with the details presented for each addressing mode later in each entry.

The operation of each instruction is specified in a format similar to Verilog HDL for minimum ambiguity, but no descriptive text or examples are included.

The effect of the instruction on each flag is listed, with a brief description. Normally the flags are updated by the main operation of the instruction, but for some complex instructions different flags may be affected by different parts of the instruction. This is specified in the description. The flags are organized as below in the F (Flag) register:

| S | Z | U5 | Н | U3 | P/V | Ν | С |

|---|---|----|---|----|-----|---|---|

|---|---|----|---|----|-----|---|---|

These flags have the following meanings:

| Flag | Meaning                                                                                    |

|------|--------------------------------------------------------------------------------------------|

| S    | Sign (a copy of the MSB of the result).                                                    |

| Z    | Zero (indicating that the result was zero).                                                |

| U5   | Unused Bit 5 (an unused Flag register bit).                                                |

| Н    | Half-Carry (carry out of the lower nibble, used for BCD math).                             |

| U3   | Unused Bit 3 (an unused Flag register bit).                                                |

| P/V  | Parity/Overflow (parity of the result, or arithmetic overflow; depends on the instruction) |

| Ν    | Negative (add/subtract flag, necessary for BCD math)                                       |

| С    | Carry (arithmetic carry, or shift linkage bit)                                             |

Fields in the instruction are listed using shortcuts for common fields. These shortcuts should be self-explanatory in most cases, but will be detailed here for completeness.

The most common field in the instruction specifies a CPU register, employing the following encoding:

| rrr | <b>Register Selected</b> |

|-----|--------------------------|

| 000 | В                        |

| 001 | С                        |

| 010 | D                        |

| 011 | E                        |

| 100 | Н                        |

| 101 | L                        |

| 111 | A (Accumulator)          |

Word registers are similarly encoded, although the exact encoding depends on the instruction:

| dd, ss, tt, xx or yy | dd, ss Register | tt Register | xx Register | yy Register |

|----------------------|-----------------|-------------|-------------|-------------|

| 00                   | BC              | BC          | BC          | BC          |

| 01                   | DE              | DE          | DE          | DE          |

| 10                   | HL              | HL          | IX          | IY          |

| 11                   | SP              | AF          | SP          | SP          |

The execution time for instructions is always a multiple of two clocks.

| ADC A, src | src: R, IM, IR, X                                                                                                                                                                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | A <= A + src + CF                                                                                                                                                                                                                                                                                                                                      |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set if arithmetic carry out of bit 3; cleared otherwise.</li> <li>P/V: Set if arithmetic overflow; cleared otherwise.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit 7; cleared otherwise.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax                | Encoding             | Clocks |

|---------------------|--------------------------------|----------------------|--------|

| R:                  | ADC A, r                       | 10001rrr             | 2      |

| IM:                 | ADC A, n                       | 11001110             | 4      |

|                     | l                              | n                    |        |

| IR:                 | ADC A, (HL)                    | 10001110             | 6      |

| X:                  | ADC A, (IX+d) or ADC A, (IY+d) | 11y11101<br>10001110 | 10     |

|                     |                                | d                    |        |

Notes:

1. The **rrr** field uses the standard register select encoding

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

|                                                                                                                                                          | src: RR                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HL <= HL + src + CF                                                                                                                                      |                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul><li>Z: Set if result is zero; cleared othe</li><li>H: Set if arithmetic carry out of bit</li><li>P/V: Set if arithmetic overflow; cleared.</li></ul> | rwise.<br>11; cleared otherwise.<br>ared otherwise.                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                             |

| Assembly Syntax                                                                                                                                          | Encoding                                                                                                                                                                                                                                                                                                     | Clocks                                                                                                                                                                                                                                                                                                                                                                                      |

| ADC HL, ss                                                                                                                                               | 11101101<br>01ss1010                                                                                                                                                                                                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                          | <ul> <li>S: Set if result is negative; cleared of</li> <li>Z: Set if result is zero; cleared other</li> <li>H: Set if arithmetic carry out of bit</li> <li>P/V: Set if arithmetic overflow; cleared.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit</li> <li>Assembly Syntax</li> </ul> | S: Set if result is negative; cleared otherwise.         Z: Set if result is zero; cleared otherwise.         H: Set if arithmetic carry out of bit 11; cleared otherwise.         P/V: Set if arithmetic overflow; cleared otherwise.         N: Cleared.         C: Set if arithmetic carry out of bit 15; cleared otherwise.         Assembly Syntax         Encoding         ADC HL, ss |

#### Notes:

1. The **ss** field uses the standard word register encoding.

# ADD

Add

| ADD A, src | src: R, IM, IR, X                                                                                                                                                                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | A <= A + src                                                                                                                                                                                                                                                                                                                                           |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set if arithmetic carry out of bit 3; cleared otherwise.</li> <li>P/V: Set if arithmetic overflow; cleared otherwise.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit 7; cleared otherwise.</li> </ul> |

| Assembly Syntax | Encoding      | Clocks                                                                                                                                                                 |  |

|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADD A, r        | 10000rrr      | 2                                                                                                                                                                      |  |

| ADD A, n        | 11000110      | 4                                                                                                                                                                      |  |

|                 |               | 6                                                                                                                                                                      |  |

|                 |               |                                                                                                                                                                        |  |

|                 | 10000110<br>d | -                                                                                                                                                                      |  |

|                 | ADD A, r      | ADD A, r     10000rrr       ADD A, n     11000110      n        ADD A, (HL)     10000110       ADD A, (IX+d) or ADD A, (IY+d)     11y11101       10000110     10000110 |  |

Notes:

1. The  ${\bf rrr}$  field uses the standard register select encoding.

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

| ADC dst, src        |                                                                                                                                                                                                                                                       | dst: HL, IX, IY<br>src: RR |        |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|--|

| Operation:          | dst <= dst + src                                                                                                                                                                                                                                      |                            |        |  |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Set if arithmetic carry out of bit 11; cleared otherwise.</li> <li>P/V: Unaffected.</li> <li>N: Cleared.</li> <li>C: Set if arithmetic carry out of bit 15; cleared otherwise.</li> </ul> |                            |        |  |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                                                                                                                       | Encoding                   | Clocks |  |

| RR:                 | ADD HL, ss                                                                                                                                                                                                                                            | 00ss1001                   | 2      |  |

|                     | ADC IX, xx                                                                                                                                                                                                                                            | 11011101<br>01xx1001       | 4      |  |

|                     | ADC IY, yy                                                                                                                                                                                                                                            | 11111101<br>01yy1001       | 4      |  |

#### Notes:

1. The ss, xx and yy fields use the standard word register select encodings.

| AND A, src | src: R, IM, IR, X                                                                                                                                                                                                                                    |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operation: | A <= A & src                                                                                                                                                                                                                                         |  |  |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set.</li> <li>P/V: Set if parity of result even; cleared otherwise.</li> <li>N: Cleared.</li> <li>C: Cleared.</li> </ul> |  |  |

| Addressing<br>Modes | Assembly Syntax                | Encoding | Clocks |

|---------------------|--------------------------------|----------|--------|

| R:                  | AND A, r                       | 10100rrr | 2      |

| IM:                 | AND A, n                       | 11100110 | 4      |

|                     |                                | n        |        |

| IR:                 | AND A, (HL)                    | 10100110 | 6      |

| X:                  | AND A, (IX+d) or AND A, (IY+d) | 11y11101 | 10     |

|                     |                                | 10100110 |        |

|                     |                                | d        | 7      |

Notes:

1. The **rrr** field uses the standard register select encoding.

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

## BIT

Bit Test

| BIT b, src | src: R, IR, X                                            |

|------------|----------------------------------------------------------|

| Operation: | $Z \leq -src[b]$                                         |

| Flags:     | S: Unaffected.                                           |

|            | <b>Z</b> : Set if tested bit is zero; cleared otherwise. |

|            | H: Set.                                                  |

|            | P/V: Unaffected.                                         |

|            | N: Cleared.                                              |

|            | C: Unaffected.                                           |

|            |                                                          |

|            |                                                          |

| Addressing<br>Modes | Assembly Syntax                | Encoding  | Clocks |

|---------------------|--------------------------------|-----------|--------|

| R:                  | BIT b, r                       | 11001011  | 4      |

|                     |                                | 01bbbrrr  |        |

| IR:                 | BIT b, (HL)                    | 10100110  | 8      |

|                     |                                | 01bbb1110 |        |

| X:                  | BIT b, (IX+d) or BIT b, (IY+d) | 11y11101  | 10     |

|                     |                                | 11001011  |        |

|                     |                                | d         |        |

|                     |                                | 01bbb110  | 1      |

Notes:

1. The **rrr** field uses the standard register select encoding.

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY.

- 3. The **bbb** field uses normal binary encoding.

- 4. For the original Z80, the  ${\bf S}$  and  ${\bf C}$  flags are undefined.

### CALL Call Subroutine

| CALL dst            |                                                                                                                                                              | dst: DA            |        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|

| Operation:          | SP <= SP - 2<br>(SP) <= PC<br>PC <= dst                                                                                                                      |                    |        |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |                    |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding           | Clocks |

| DA:                 | CALL mn                                                                                                                                                      | 11001101<br>n<br>m | 10     |

#### CALL Conditional Call Subroutine

| CALL cc, dst        |                                                                                                                                                              | dst: DA            |                           |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------|

| Operation:          | if (cc = true) begin<br>SP <= SP - 2<br>(SP) <= PC<br>PC <= dst<br>end                                                                                       |                    |                           |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |                    |                           |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding           | Clocks                    |

| DA:                 | CALL cc, mn                                                                                                                                                  | 11fff100<br>n<br>m | 10/6<br>(taken/not taken) |

| <b>Notes:</b><br>1. | Mnemonic Encoding (fff)                                                                                                                                      | Meaning Flag case  |                           |

| 1. | Mnemonic | Encoding (fff) | Meaning     | Flag case        |

|----|----------|----------------|-------------|------------------|

|    | NZ       | 000            | Non-zero    | Z = 0            |

|    | Z        | 001            | Zero        | Z = 1            |

|    | NC       | 010            | Non-carry   | C = 0            |

|    | С        | 011            | Carry       | C = 1            |

|    | PO       | 100            | Parity Odd  | P/V = 0          |

|    | PE       | 101            | Parity Even | P/V = 1          |

|    | Р        | 110            | Plus        | $\mathbf{S} = 0$ |

|    | Μ        | 111            | Minus       | <b>S</b> = 1     |

|    |          |                |             |                  |

| Operation:          | CF <= ~CF                                                         |          |        |  |

|---------------------|-------------------------------------------------------------------|----------|--------|--|

| Flags:              | S: Unaffected.                                                    |          |        |  |

|                     | Z: Unaffected.                                                    |          |        |  |

|                     | H: Copy of previous value of Carry flag.                          |          |        |  |

|                     | P/V: Unaffected.                                                  |          |        |  |

|                     | P/V: Unaffected.                                                  |          |        |  |

|                     | P/V: Unaffected.<br>N: Cleared.                                   |          |        |  |

|                     |                                                                   | herwise. |        |  |

| Addressing          | N: Cleared.<br>C: Set if previous Carry flag was zero; cleared ot |          | Chala  |  |

| Addressing<br>Modes | N: Cleared.<br>C: Set if previous Carry flag was zero; cleared ot | herwise. | Clocks |  |

| CP A, src  | src: R, IM, IR, X                                                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | A - src                                                                                                                                                                                                                                                                                                                                              |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set if arithmetic borrow out of bit 3; cleared otherwise.</li> <li>P/V: Set if arithmetic overflow; cleared otherwise.</li> <li>N: Set.</li> <li>C: Set if arithmetic borrow out of bit 7; cleared otherwise.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax           | Encoding             | Clocks |

|---------------------|---------------------------|----------------------|--------|

| R:                  | CP A, r                   | 10111rrr             | 2      |

| IM:                 | CP A, n                   | 11111110             | 4      |

|                     |                           | n                    |        |

| IR:                 | CP A, (HL)                | 10111110             | 6      |

| X:                  | CP A, (IX+d) or CP (IY+d) | 11y11101<br>10111110 | 10     |

|                     | -                         | d                    |        |

1. The  ${\bf rrr}$  field uses the standard register select encoding

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

| CPD                 |                                                                                                                                                                                                                                                                                                                                                            |                      |        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|

| Operation:          | A - (HL)<br>HL <= HL - 1<br>BC <= BC - 1                                                                                                                                                                                                                                                                                                                   |                      |        |

| Flags:              | <ul> <li>S: Set if result of compare is negative, cleared otherwise.</li> <li>Z: Set if result of compare is zero; cleared otherwise.</li> <li>H: Set if arithmetic borrow out of bit 3 during compare; cleared otherwise.</li> <li>P/V: Set if result of BC decrement is non-zero; cleared otherwise.</li> <li>N: Set.</li> <li>C: Unaffected.</li> </ul> |                      |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                                                                                                                                                                                                                            | Encoding             | Clocks |

|                     | CPD                                                                                                                                                                                                                                                                                                                                                        | 11101101<br>10101001 | 10     |

# **CPDR**

**Compare, Decrement and Repeat**

## CPDR

| Operation: | A - (HL)<br>HL <= HL - 1<br>BC <= BC - 1<br>repeat if BC != 0 and A - (HL) != 0                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flags:     | <ul> <li>S: Set if result of compare is negative, cleared otherwise.</li> <li>Z: Set if result of compare is zero; cleared otherwise.</li> <li>H: Set if arithmetic borrow out of bit 3 during compare; cleared otherwise.</li> <li>P/V: Set if result of BC decrement is non-zero; cleared otherwise.</li> </ul> |

|            | N: Set.<br>C: Unaffected.                                                                                                                                                                                                                                                                                         |

| Addressing<br>Modes | Assembly Syntax | Encoding | Clocks   |

|---------------------|-----------------|----------|----------|

| (                   | CPDR            | 11101101 | 8 + 4i   |

|                     |                 | 10111001 |          |

|                     | L               |          | <b>_</b> |

### Notes:

1. This instruction can be interrupted after each iteration. The address saved on the stack in this case is the address of this instruction, allowing completion of the instruction after the interrupt service routine.

2. Interrupts are sampled during each memory read operation.

| CPI                 |                                                                                                                                                                                                                                      |                                                             |        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------|

| Operation:          | A - (HL)<br>HL <= HL + 1<br>BC <= BC - 1                                                                                                                                                                                             |                                                             |        |

| Flags:              | <ul> <li>S: Set if result of compare is nega</li> <li>Z: Set if result of compare is zero</li> <li>H: Set if arithmetic borrow out o</li> <li>P/V: Set if result of decrementing</li> <li>N: Set.</li> <li>C: Unaffected.</li> </ul> | o; cleared otherwise.<br>f bit 3 during compare; cleared or |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                                                                                                      | Encoding                                                    | Clocks |

|                     | СРІ                                                                                                                                                                                                                                  | 11101101<br>10100001                                        | 10     |

# CPIR

**Compare, Increment and Repeat**

## CPIR

| Operation: | A - (HL)<br>HL <= HL + 1<br>BC <= BC - 1<br>repeat if BC != 0 and A - (HL) != 0                                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flags:     | <ul> <li>S: Set if result of compare is negative, cleared otherwise.</li> <li>Z: Set if result of compare is zero; cleared otherwise.</li> <li>H: Set if arithmetic borrow out of bit 3 during compare; cleared otherwise.</li> <li>P/V: Set if result of decrementing BC is non-zero; cleared otherwise.</li> <li>N: Set.</li> <li>C: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax | Encoding | Clocks |

|---------------------|-----------------|----------|--------|

| (                   | CPIR            | 11101101 | 8 + 4i |

|                     |                 | 10110001 |        |

|                     |                 |          | -      |

### Notes:

1. This instruction can be interrupted after each iteration. The address saved on the stack in this case is the address of this instruction, allowing completion of the instruction after the interrupt service routine

2. Interrupts are sampled during each memory read operation.

| CPL                 |                                                                                                                                                |          |        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| Operation:          | A <= ~A                                                                                                                                        |          |        |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Set.</li> <li>P/V: Unaffected.</li> <li>N: Set.</li> <li>C: Unaffected.</li> </ul> |          |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                | Encoding | Clocks |

|                     | CPL                                                                                                                                            | 00101111 | 2      |

## DAA

| vise. |

|-------|

|       |

|       |

|       |

|       |

| Addressing<br>Modes | Assembly Syntax | Encoding | Clocks |

|---------------------|-----------------|----------|--------|

| D                   | DAA [           | 00100111 | ] 2    |

Notes:

| Instruction          | C before | A[7:4]     | H before | A[3:0]     | Number     | C after |

|----------------------|----------|------------|----------|------------|------------|---------|

| Instruction          | DAA      | before DAA | DAA      | before DAA | added to A | DAA     |

|                      | 0        | 0-9        | 0        | 0-9        | 00         | 0       |

|                      | 0        | 0-8        | 0        | A-F        | 06         | 0       |

|                      | 0        | 0-9        | 1        | 0-3        | 06         | 0       |

| ADC, ADD or INC      | 0        | A-F        | 0        | 0-9        | 60         | 1       |

|                      | 0        | 9-F        | 0        | A-F        | 66         | 1       |

|                      | 0        | A-F        | 1        | 0-3        | 66         | 1       |

|                      | 1        | 0-2        | 0        | 0-9        | 60         | 1       |

|                      | 1        | 0-2        | 0        | A-F        | 66         | 1       |

|                      | 1        | 0-3        | 1        | 0-3        | 66         | 1       |

|                      | 0        | 0-9        | 0        | 0-9        | 00         | 0       |

| DEC, NEG, SUB or SBC | 0        | 0-8        | 1        | 6-F        | FA         | 0       |

|                      | 1        | 7-F        | 0        | 0-9        | A0         | 1       |

|                      | 1        | 6-F        | 1        | 6-F        | 9A         | 1       |

| DEC dst    | dst: R, IR, X                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation: | dst <= dst - 1                                                                                                                                                                                                                                                                                         |

| Flags:     | <ul> <li>S: Set if result is negative; cleared otherwise.</li> <li>Z: Set if result is zero; cleared otherwise.</li> <li>H: Set if arithmetic borrow out of bit 3; cleared otherwise.</li> <li>P/V: Set if arithmetic overflow; cleared otherwise.</li> <li>N: Set.</li> <li>C: Unaffected.</li> </ul> |

| Addressing<br>Modes | Assembly Syntax          | Encoding                  | Clocks |

|---------------------|--------------------------|---------------------------|--------|

| R:                  | DEC r                    | 00rrr101                  | 2      |

| IR:                 | DEC (HL)                 | 00110101                  | 8      |

| <b>X</b> :          | DEC (IX+d) or DEC (IY+d) | 11y11101<br>00110101<br>d | 12     |

|                     |                          | 00110101                  |        |

1. The **rrr** field uses the standard register select encoding

2.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

# **DEC** Decrement (Word)

| dst - 1<br>ffected.<br>ffected.<br>ffected. |                 |                                                           |                                   |

|---------------------------------------------|-----------------|-----------------------------------------------------------|-----------------------------------|

| ffected.<br>ffected.                        |                 |                                                           |                                   |

| naffected.<br>ffected.<br>ffected.          |                 |                                                           |                                   |

| Assembly Syntax                             | Encodir         | ng                                                        | Clocks                            |

| 1                                           | 00dd101         | 11                                                        | 2                                 |

| K or DEC IY                                 |                 |                                                           | 4                                 |

| 1                                           | Assembly Syntax | Assembly Syntax Encodin<br>000dd10<br>C or DEC IY 11y1110 | Assembly Syntax Encoding 00dd1011 |

Notes:

1. The **dd** field uses the standard word register encoding.

| DI                  |                         |          |        |

|---------------------|-------------------------|----------|--------|

|                     |                         |          |        |

| <b>Operation:</b>   | IFF1 <= 0               |          |        |

|                     | IFF2 <= 0               |          |        |

|                     |                         |          |        |

| Flags:              | S: Unaffected.          |          |        |

| 8                   | <b>Z:</b> Unaffected.   |          |        |

|                     | <b>H:</b> Unaffected.   |          |        |

|                     | <b>P/V:</b> Unaffected. |          |        |

|                     | <b>N:</b> Unaffected.   |          |        |

|                     | <b>C:</b> Unaffected.   |          |        |

|                     |                         |          |        |

|                     |                         |          |        |

| Addressing<br>Modes | Assembly Syntax         | Encoding | Clocks |

|                     | זת                      | 11110011 | 2      |

|                     | DI                      | 11110011 | 2      |

|                     |                         |          |        |

1. Interrupts are last sampled during the machine cycle that fetches this instruction.

# DJNZ

Decrement, Jump if Non-zero

### **DJNZ** e

| Operation:          | $B \le B - 1$<br>if ( $B \ge 0$ ) PC $\le PC + e$ (where PC is the PC of this instruction)                                                                   |                    |        |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|--|--|

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |                    |        |  |  |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding           | Clocks |  |  |

|                     | DJNZ e                                                                                                                                                       | 00010000<br>(e-2)- | 6      |  |  |

### Notes:

1. Relative to the address of this instruction, the jump range is -126 to +129. Relative to the address of the next instruction, the jump range is -128 to +127.

| EI                  |                                                                                                                                                              |          |        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| Operation:          | IFF1 <= 1<br>IFF2 <= 1                                                                                                                                       |          |        |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |          |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding | Clocks |

|                     | EI                                                                                                                                                           | 11111011 | 2      |

|                     |                                                                                                                                                              |          |        |

1. Interrupts are first sampled during the fetch of the next instruction. If an interrupt is pending this instruction fetch will be ignored and an interrupt acknowledge cycle started.

# EX

## Exchange with Top-of-Stack

| EX (SP), src        |                                                                                                                                                              | src: HL, IX, IY      |        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|

| Operation:          | (SP) <=> L or IXL or IYL<br>(SP+1) <=> H or IXH or IYH                                                                                                       |                      |        |

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |                      |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding             | Clocks |

|                     | EX (SP), HL                                                                                                                                                  | 11100011             | 12     |

|                     | EX (SP), IX or EX (SP), IY                                                                                                                                   | 11y11101<br>11100011 | 14     |

Notes:

1.  $\mathbf{y} = 0$  selects IX and  $\mathbf{y} = 1$  selects IY

EX AF, AF' Exchange Accumulator

| Auuressing | Assembly Syntax                                                                                                                  | Encoding | Clocks |

|------------|----------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| Addressing | <ul><li>P/V: Replaced by alternate flag.</li><li>N: Replaced by alternate flag.</li><li>C: Replaced by alternate flag.</li></ul> |          |        |

| Flags:     | <ul><li>S: Replaced by alternate flag.</li><li>Z: Replaced by alternate flag.</li><li>H: Replaced by alternate flag.</li></ul>   |          |        |

| Operation: | AF <=> AF'                                                                                                                       |          |        |

## Notes:

1. No data is actually moved. Instead the registers are renamed.

## EX DE, HL

| <b>Operation:</b>   | DE <=> HL                          |          |        |

|---------------------|------------------------------------|----------|--------|

| Flags:              | S: Unaffected.<br>Z: Unaffected.   |          |        |

|                     | H: Unaffected.<br>P/V: Unaffected. |          |        |

|                     | N: Unaffected.<br>C: Unaffected.   |          |        |

|                     |                                    |          |        |

| Addressing<br>Modes | Assembly Syntax                    | Encoding | Clocks |

|                     | EX DE, HL                          | 11101011 | 2      |

|                     | EA DE, HL                          | 11101011 |        |

|                     | EXX                                                       | 11011001 | 2      |

|---------------------|-----------------------------------------------------------|----------|--------|

| Addressing<br>Modes | Assembly Syntax                                           | Encoding | Clocks |

|                     | C: Unaffected.                                            |          |        |

|                     | <ul><li>P/V: Unaffected.</li><li>N: Unaffected.</li></ul> |          |        |

|                     | H: Unaffected.                                            |          |        |

|                     | Z: Unaffected.                                            |          |        |

| Flags:              | S: Unaffected.                                            |          |        |

|                     | HL <=> HL'                                                |          |        |

|                     | DE <=> DE'                                                |          |        |

| <b>Operation:</b>   | BC <=> BC'                                                |          |        |

|                     |                                                           |          |        |

1. No data is actually moved. Instead the registers are renamed.

# HALT

Halt

## HALT

| Operation:          | activate Halt signal and wait fo                                                                                                                             | or interrupt |        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|

| Flags:              | <ul> <li>S: Unaffected.</li> <li>Z: Unaffected.</li> <li>H: Unaffected.</li> <li>P/V: Unaffected.</li> <li>N: Unaffected.</li> <li>C: Unaffected.</li> </ul> |              |        |

| Addressing<br>Modes | Assembly Syntax                                                                                                                                              | Encoding     | Clocks |

|                     | HALT                                                                                                                                                         | 01110110     | 4 + 2n |

### Notes:

1. The CPU halts with an idle bus until an interrupt is requested. The address pushed to the stack during the interrupt acknowledge is the address of the next instruction. During Halt the **mem\_addr\_out** and **io\_addr\_out** are driven with 0x0000, and the **mem\_data\_out** and **io\_data\_out** are driven with 0x000.

### IM i

| Operation: | Set Interrupt Mode i |  |  |

|------------|----------------------|--|--|

| Flags:     | S: Unaffected.       |  |  |

| -          | Z: Unaffected.       |  |  |

|            | H: Unaffected.       |  |  |

|            | P/V: Unaffected.     |  |  |

|            | N: Unaffected.       |  |  |

|            | C: Unaffected.       |  |  |

| Addressing<br>Modes | Assembly Syntax | Encoding | Clocks |

|---------------------|-----------------|----------|--------|

| IM                  | 0               | 11101101 | 4      |

|                     |                 | 01000110 |        |

|                     |                 |          | -      |

| IM                  | [1              | 11101101 | 4      |

|                     |                 | 01010110 |        |

|                     |                 |          | -      |

| IM                  | [2              | 11101101 | 4      |

|                     |                 | 01011110 |        |

|                     |                 |          |        |

### Notes:

1. Interrupt Mode 0 always jumps to location 0x0038 in response to a maskable interrupt request.